# **CSIT REPORT**

Release rls2009

# **CONTENTS**

| 1   | Introduction                                                                                                                               | 1                                                    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|     | 1.1 Report History                                                                                                                         |                                                      |

|     | 1.2 Report Structure                                                                                                                       |                                                      |

|     | 1.3 Test Scenarios                                                                                                                         |                                                      |

|     | 1.4 Physical Testbeds                                                                                                                      |                                                      |

|     | 1.5 Test Methodology                                                                                                                       | . 13                                                 |

| 2   | VPP Performance 2.1 Overview                                                                                                               | . 46<br>. 48<br>. 287<br>. 524<br>. 785<br>. 790     |

|     | 2.8 NFV Service Density   2.9 Hoststack Testing   2.10 Comparisons   2.11 Throughput Trending   2.12 Test Environment   2.13 Documentation | . 874<br>. 880<br>. 892<br>. 894                     |

| 3   | DPDK Performance  3.1 Overview                                                                                                             | . 942<br>. 944<br>. 982<br>. 998<br>. 1001<br>. 1002 |

| 4   | VPP Device 4.1 Overview                                                                                                                    | . 1045<br>. 1045                                     |

|     | CSIT Framework 5.1 Design                                                                                                                  | . 1055<br>. 1058<br>. 1060<br>. 1088                 |

| RII | liography                                                                                                                                  | 1104                                                 |

# INTRODUCTION

# 1.1 Report History

FD.io CSIT-2009 Report history and per .[ww] revision changes are listed below.

| .[ww] Revision | Changes                                                                                                                                                                                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .43            | <ol> <li>Added data:         <ul> <li>VPP Coverage</li> <li>3n-skx</li> <li>2n-clx</li> </ul> </li> <li>VPP Iterative         <ul> <li>3n-skx</li> <li>3n-tsh</li> </ul> </li> <li>Replaced faulty runs:         <ul> <li>VPP Iterative</li> <li>2n-clx</li> </ul> </li> </ol> |

| .42            | Initial version                                                                                                                                                                                                                                                                |

FD.io CSIT Reports follow CSIT-[yy][mm].[ww] numbering format, with version denoted by concatenation of two digit year [yy] and two digit month [mm], and maintenance revision identified by two digit calendar week number [ww].

# 1.2 Report Structure

FD.io CSIT-2009 report contains system performance and functional testing data of VPP-20.09 release. PDF version of this report<sup>1</sup> is available for download.

CSIT-2009 report is structured as follows:

- 1. INTRODUCTION: General introduction to FD.io CSIT-2009.

- Introduction: This section.

- Test Scenarios Overview: A brief overview of test scenarios covered in this report.

- Physical Testbeds: Description of physical testbeds.

- Test Methodology: Performance benchmarking and functional test methodologies.

- 2. VPP PERFORMANCE: VPP performance tests executed in physical FD.io testbeds.

- Overview: Tested logical topologies, test coverage and naming specifics.

<sup>&</sup>lt;sup>1</sup> https://docs.fd.io/csit/rls2009/report/\_static/archive/csit\_rls2009.43.pdf

- Release Notes: Changes in CSIT-2009, added tests, environment or methodology changes, known issues.

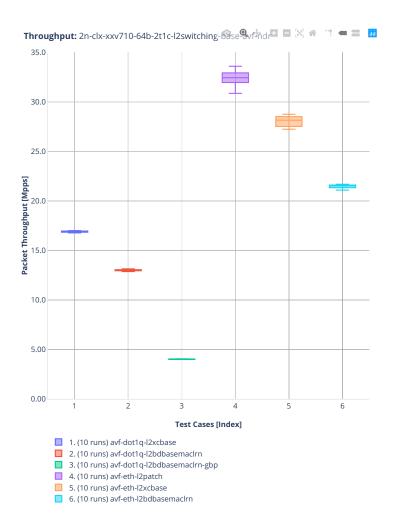

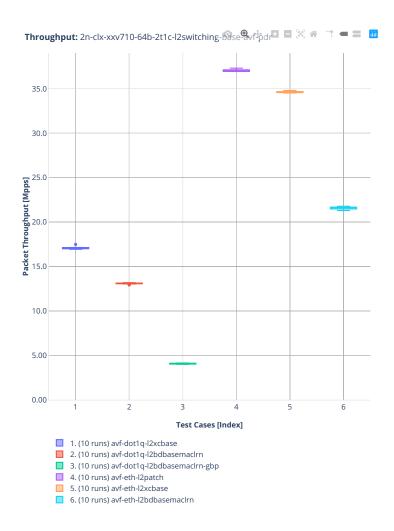

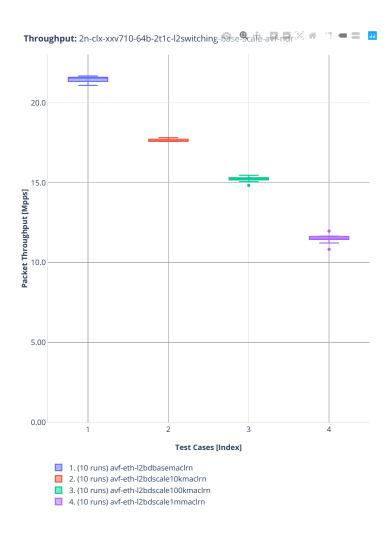

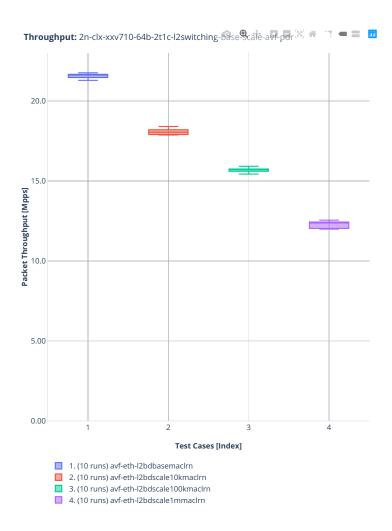

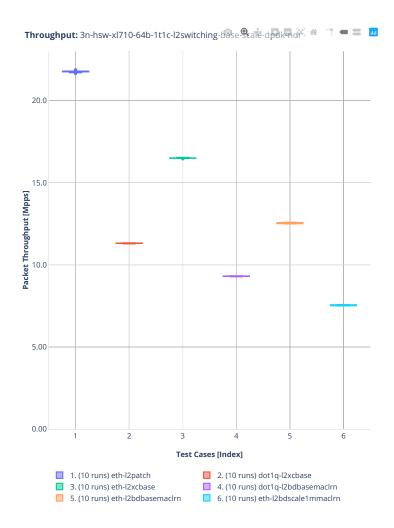

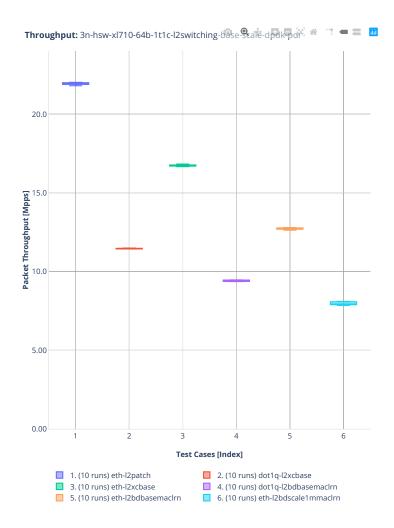

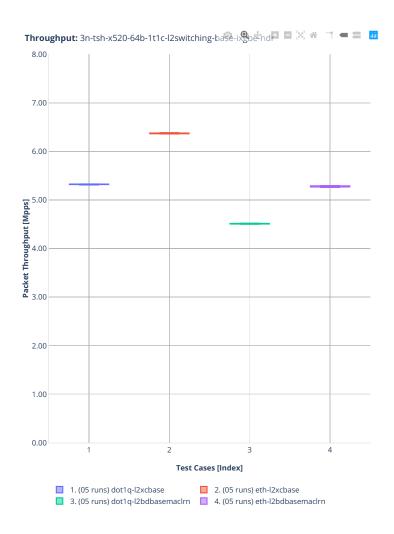

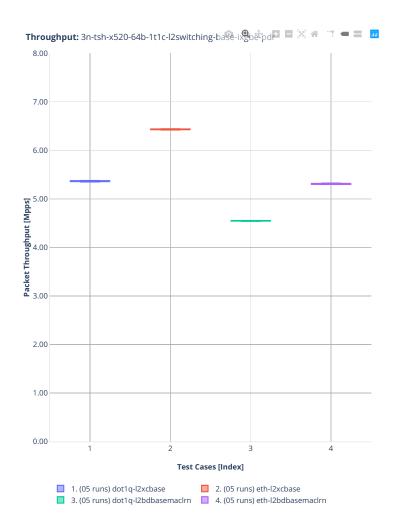

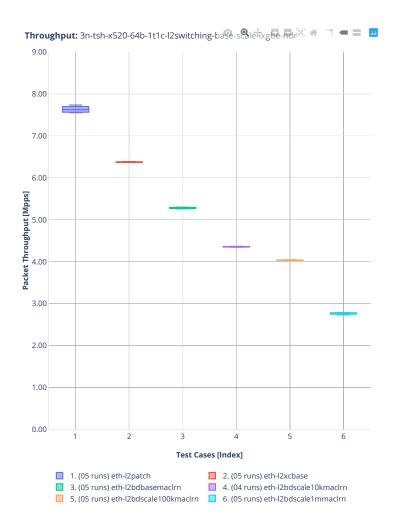

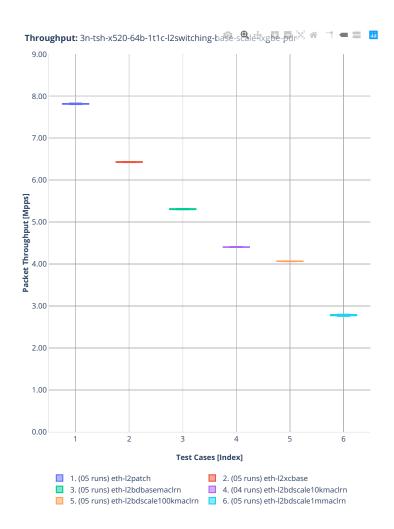

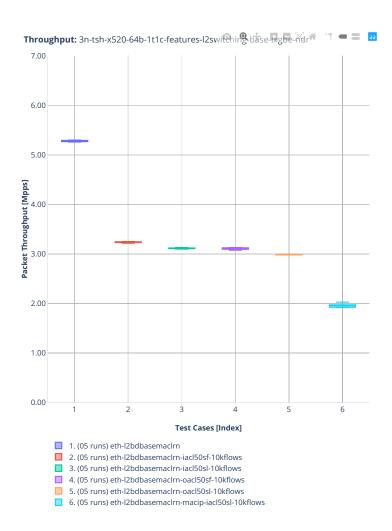

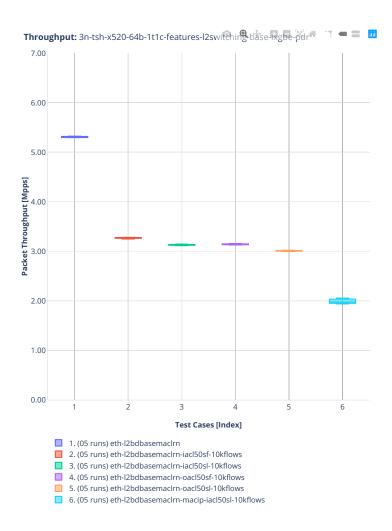

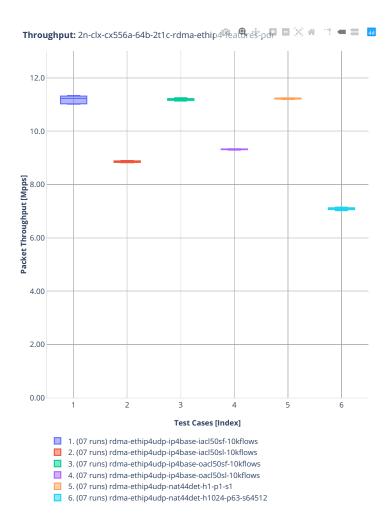

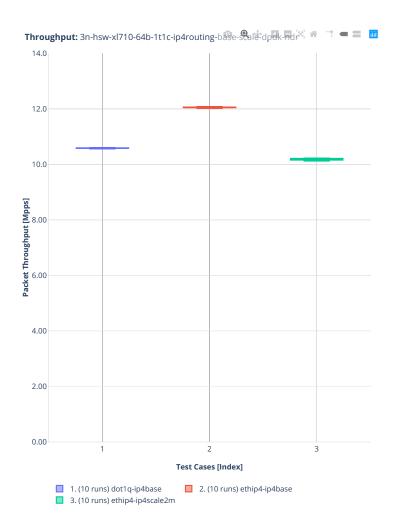

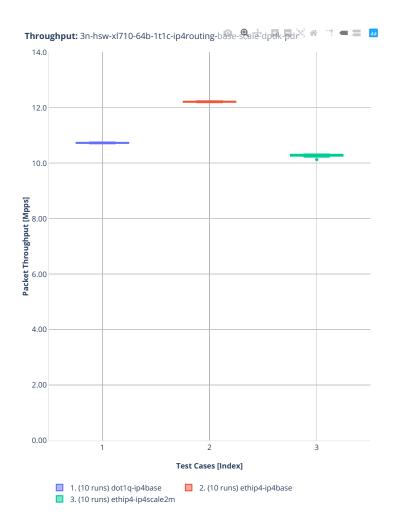

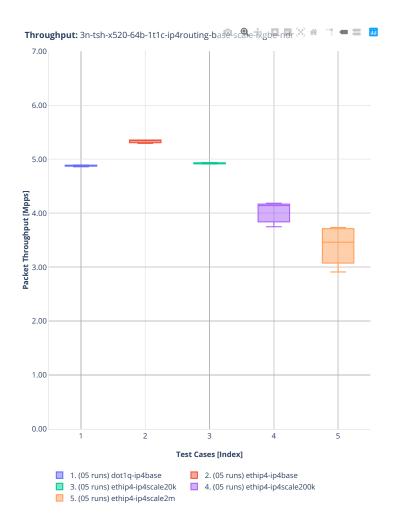

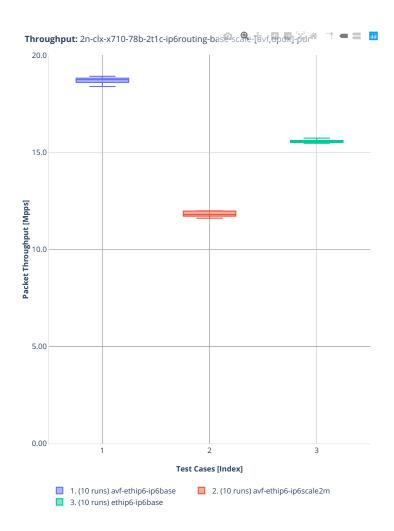

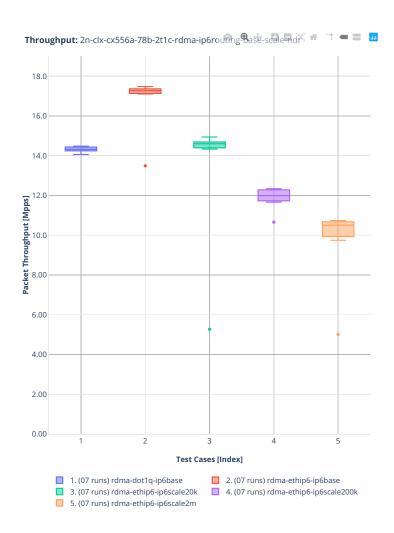

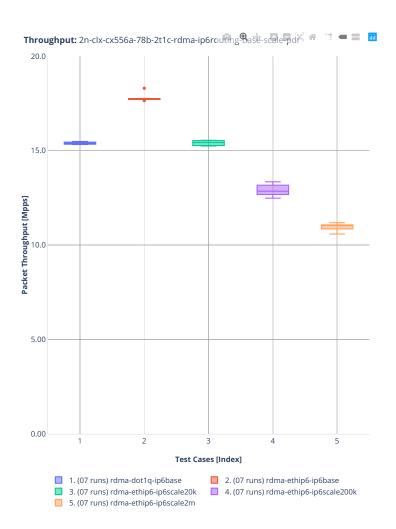

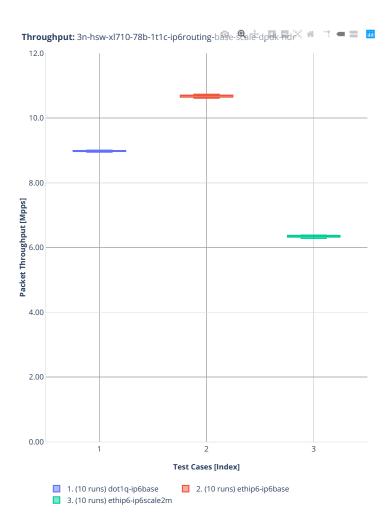

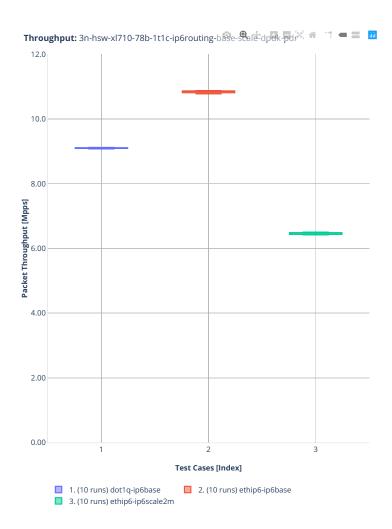

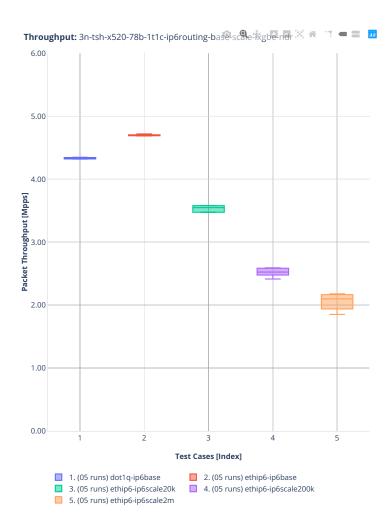

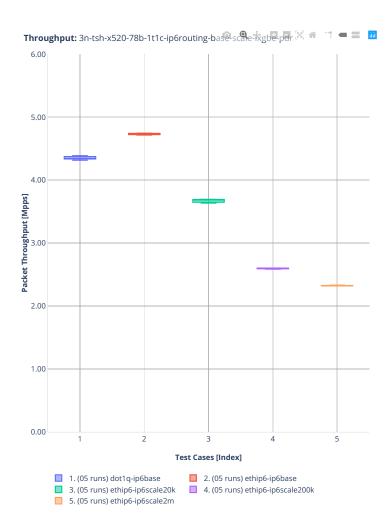

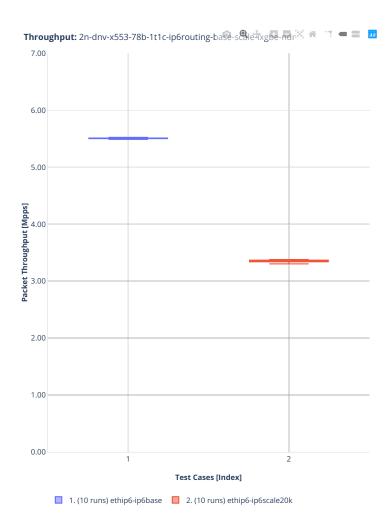

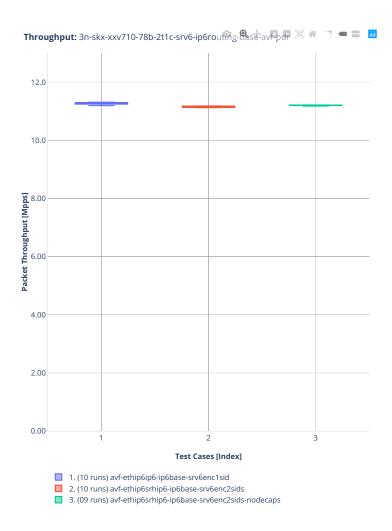

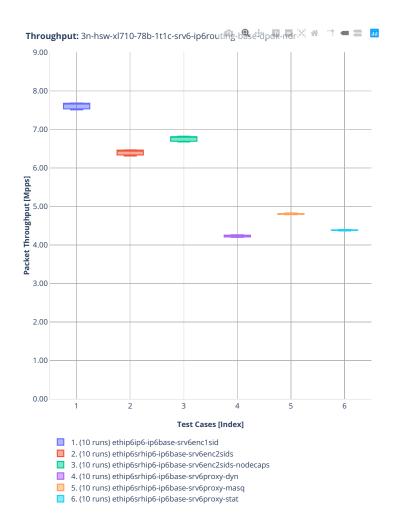

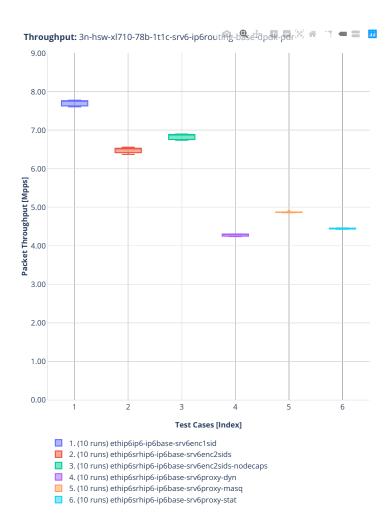

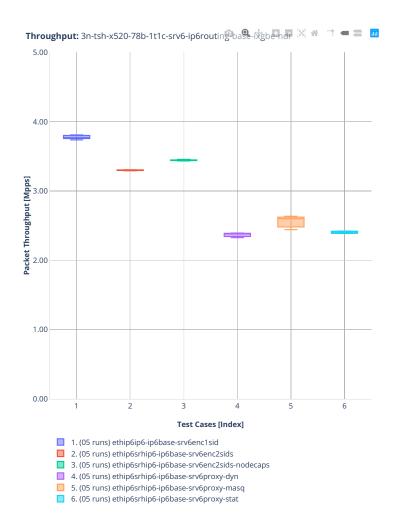

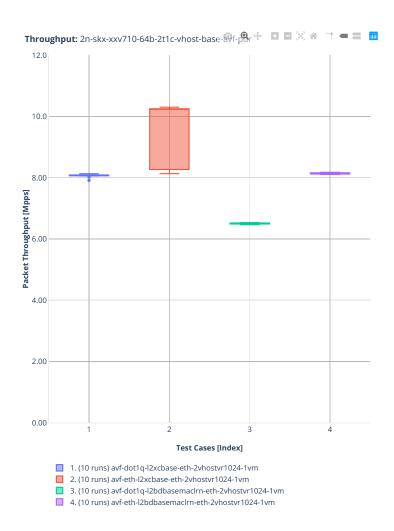

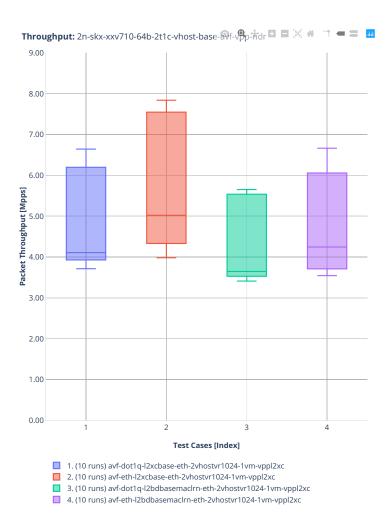

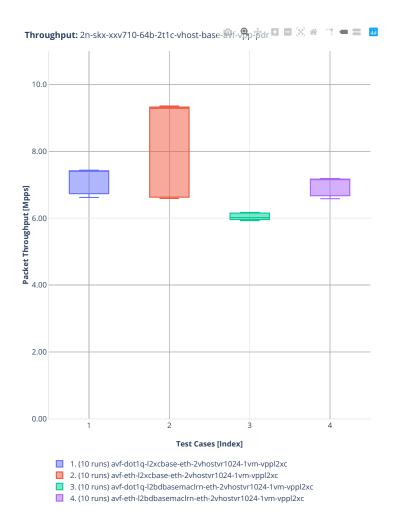

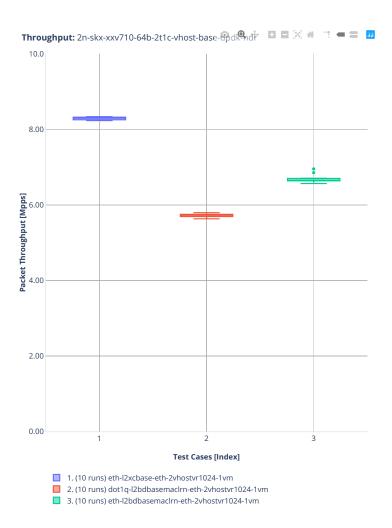

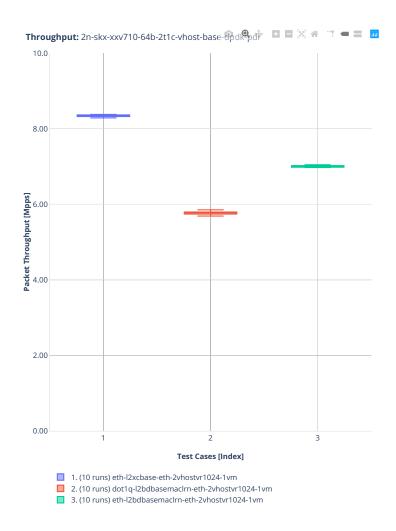

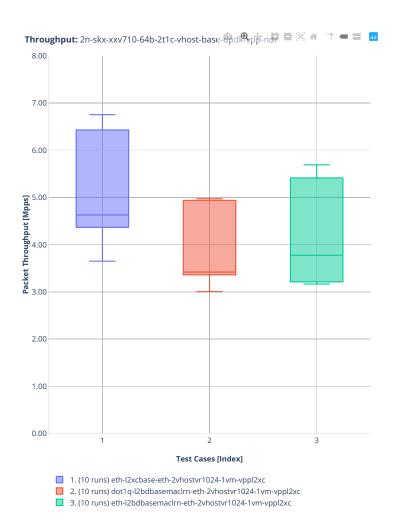

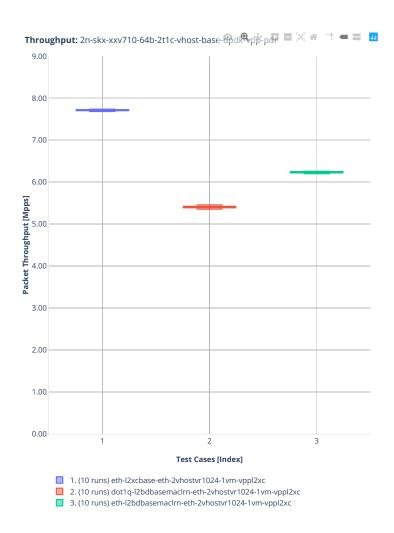

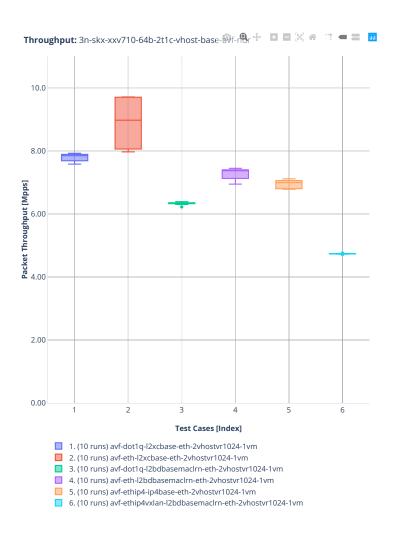

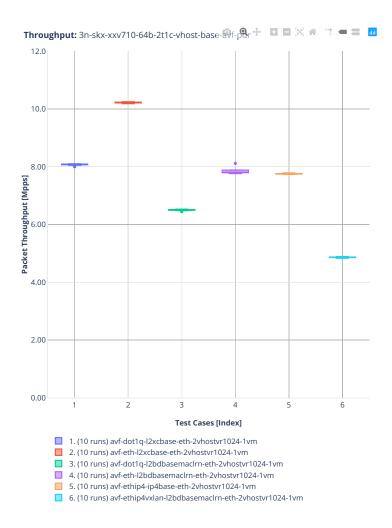

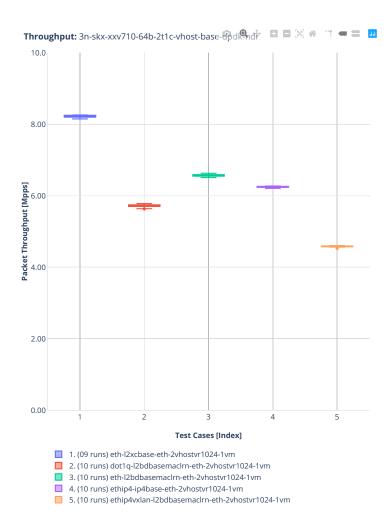

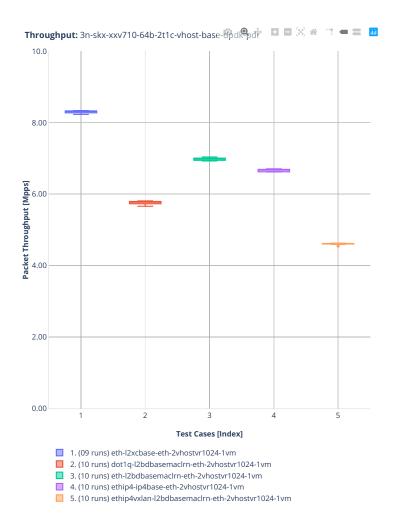

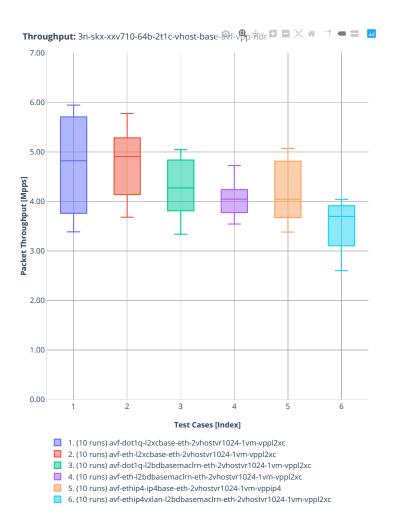

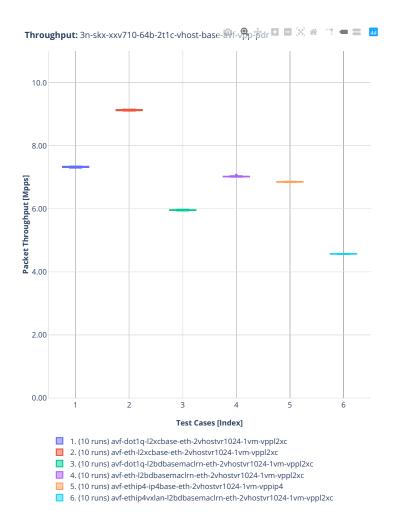

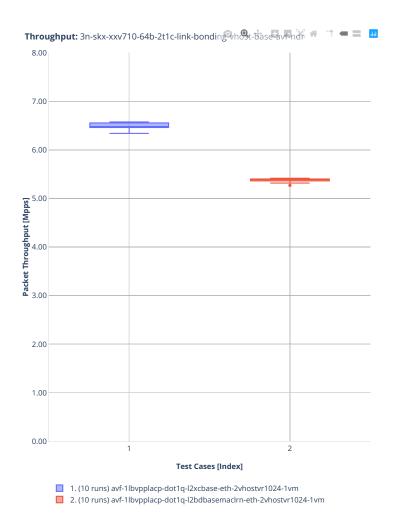

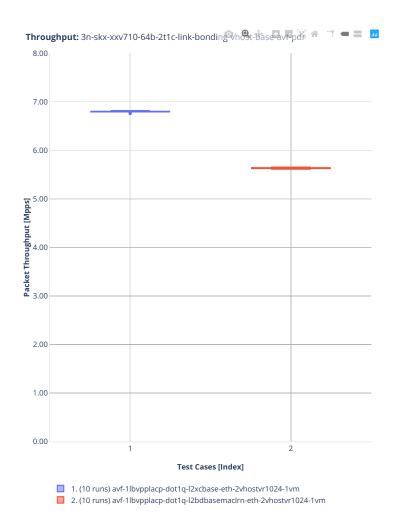

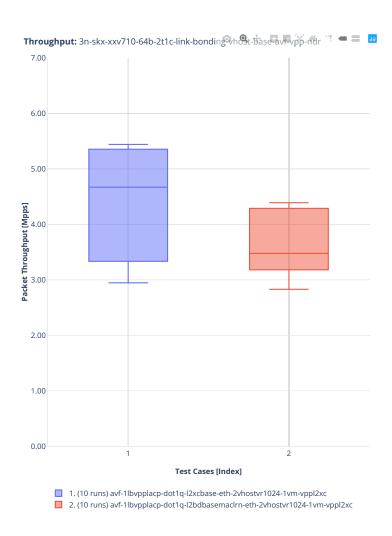

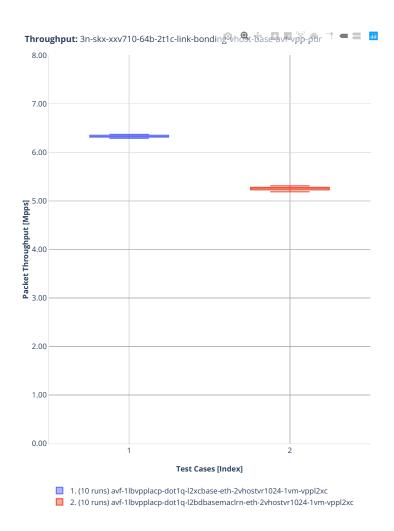

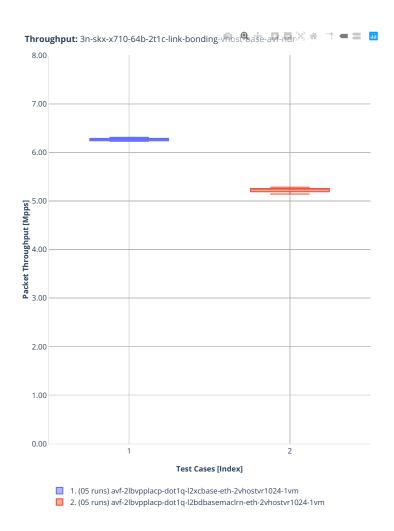

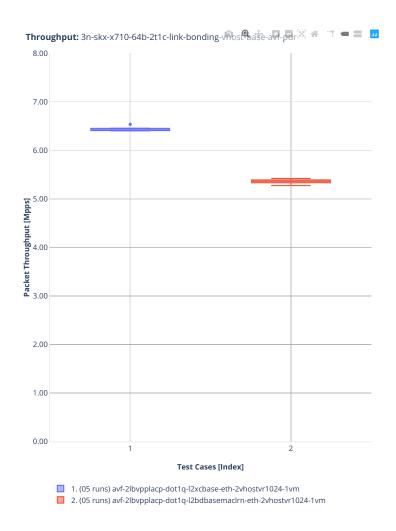

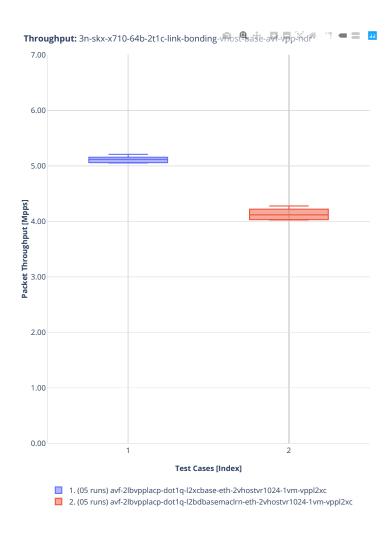

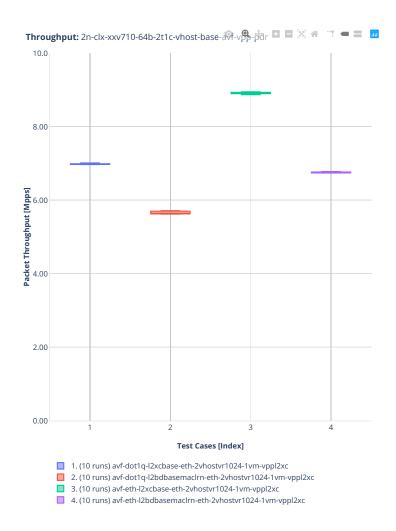

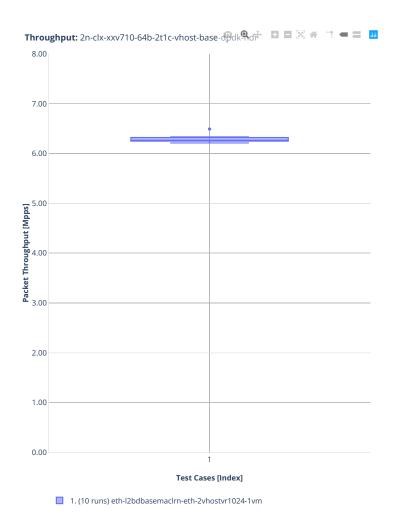

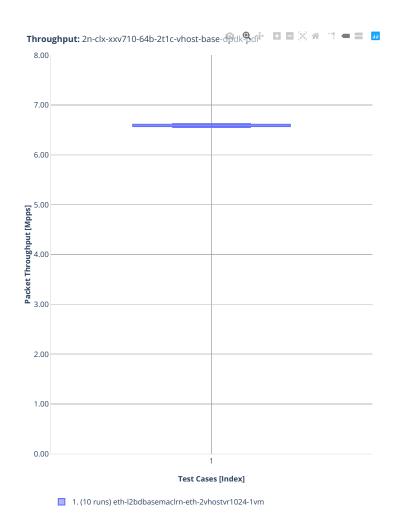

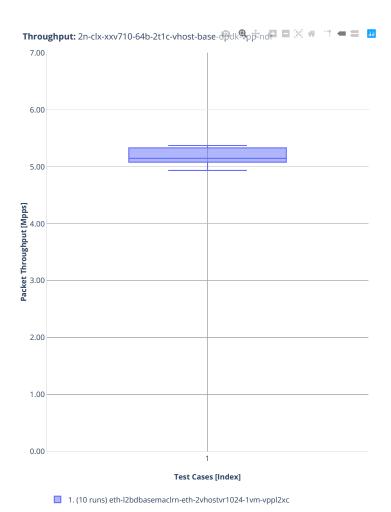

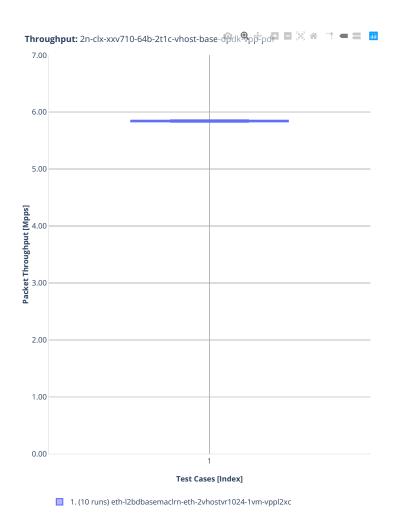

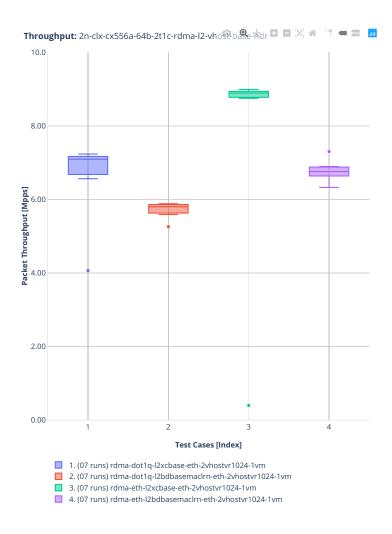

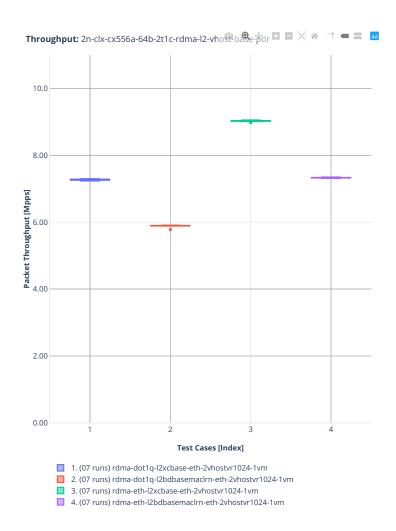

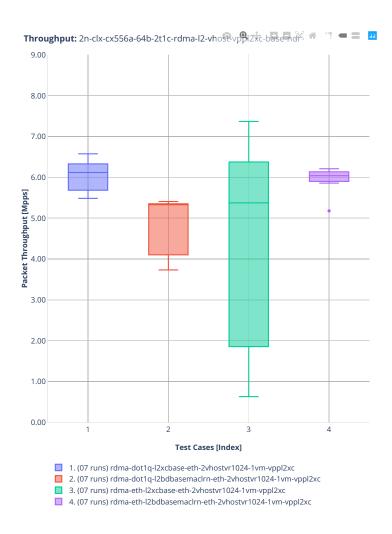

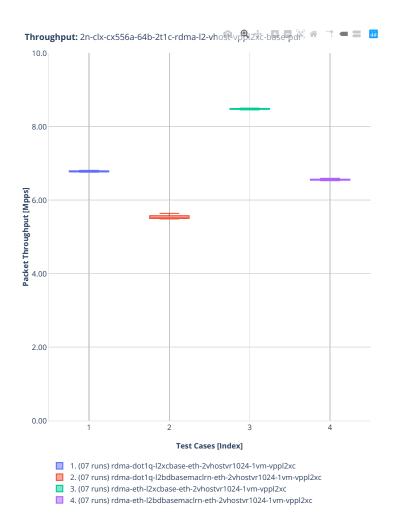

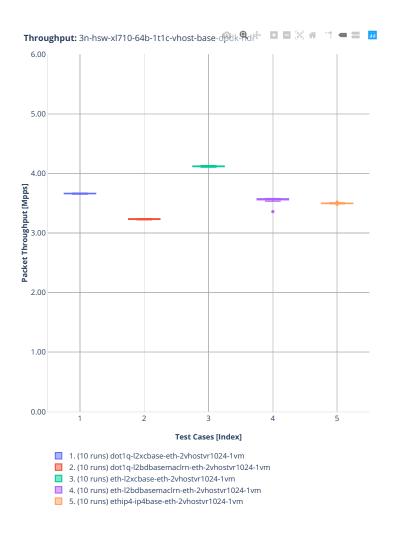

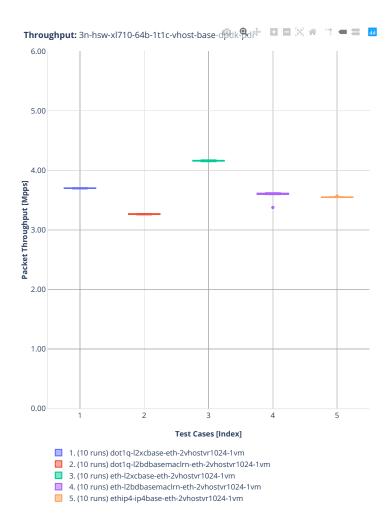

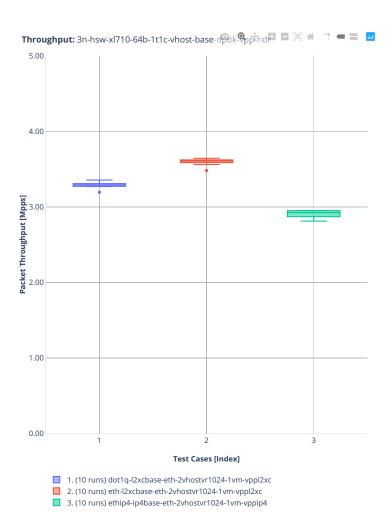

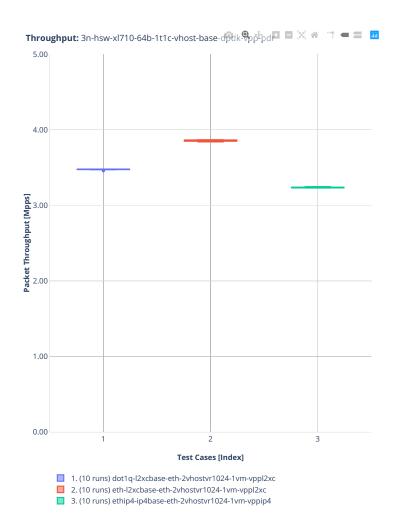

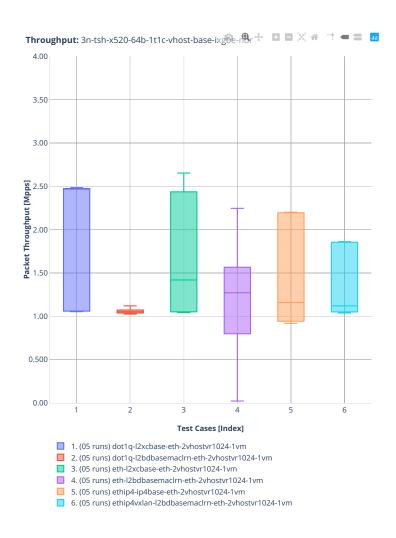

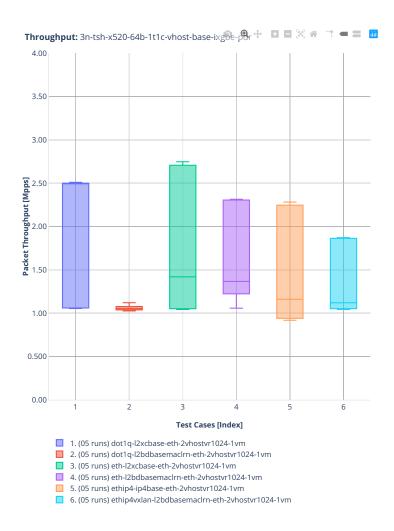

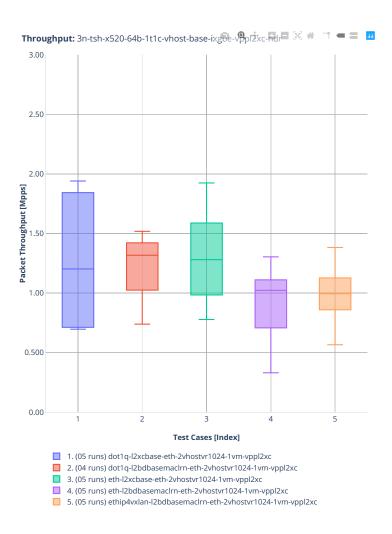

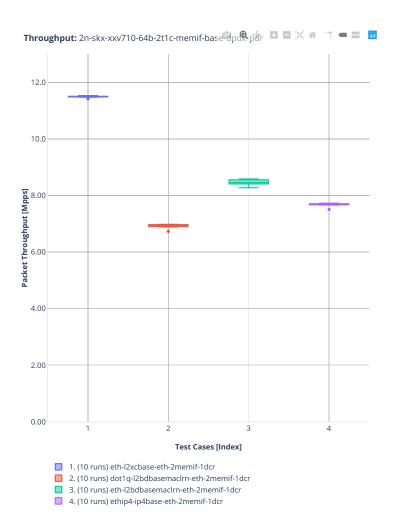

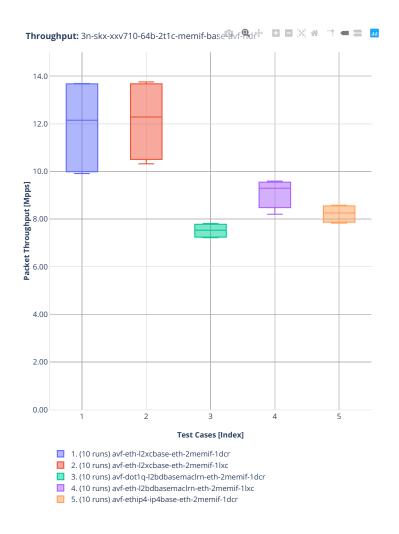

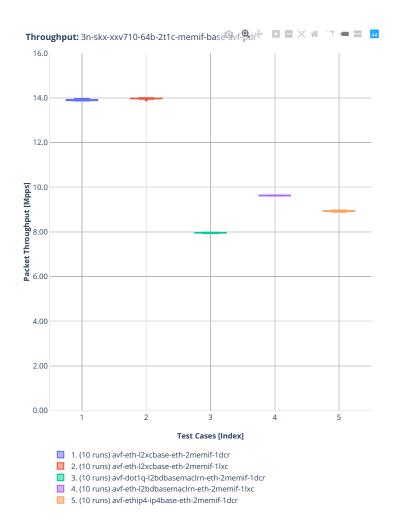

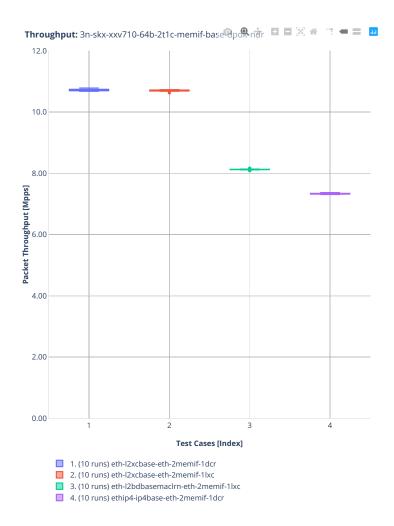

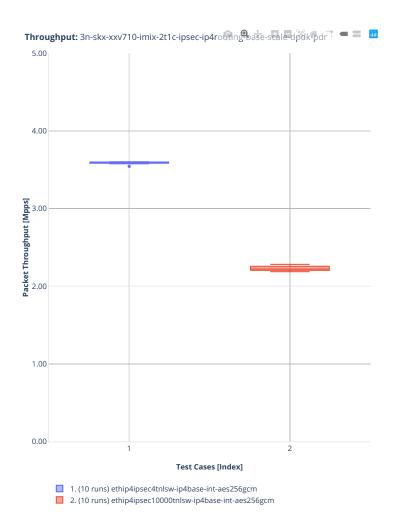

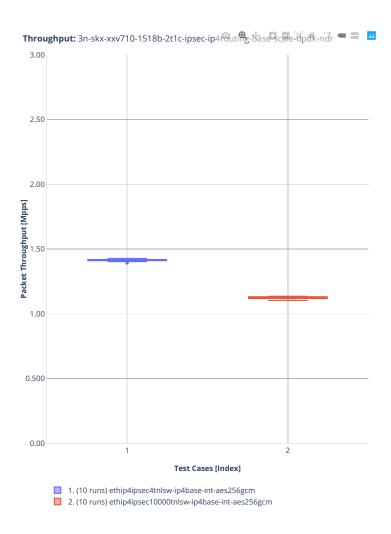

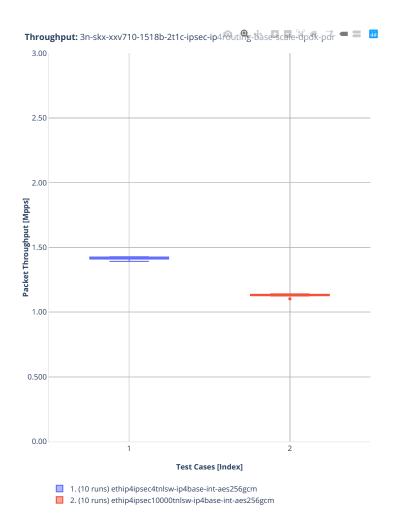

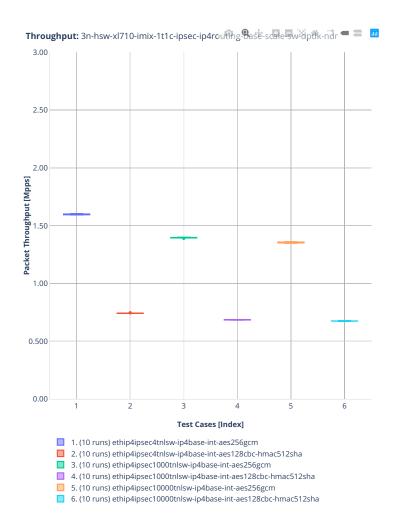

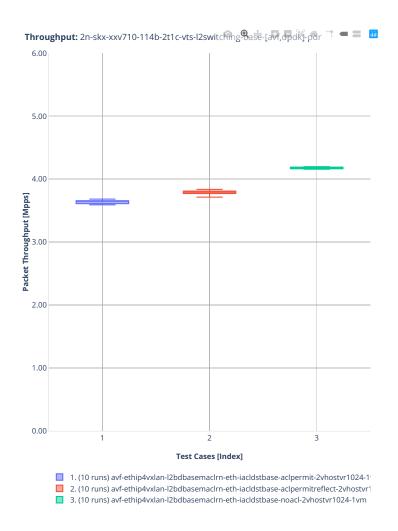

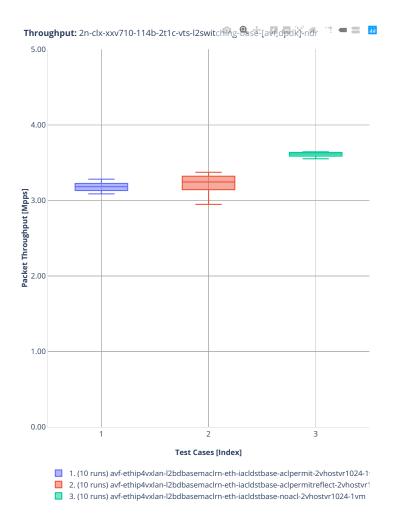

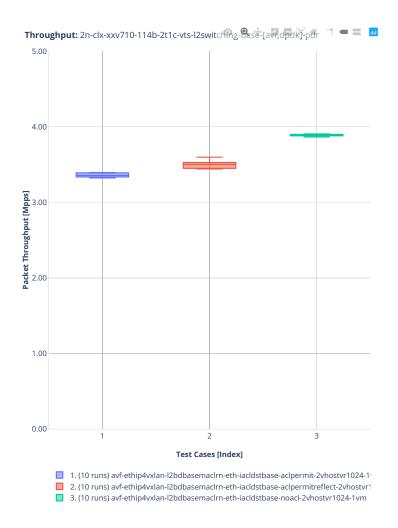

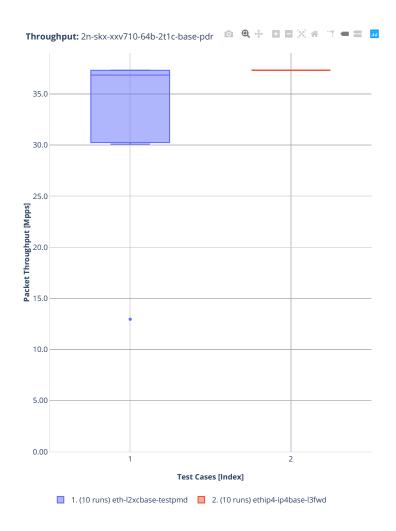

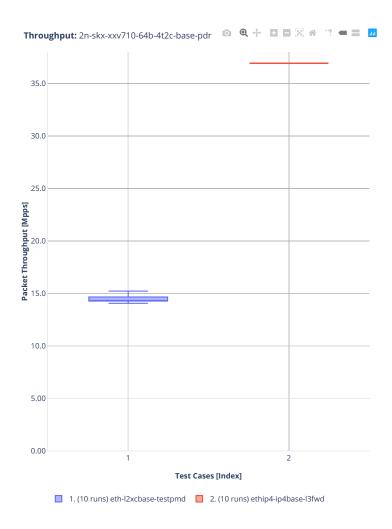

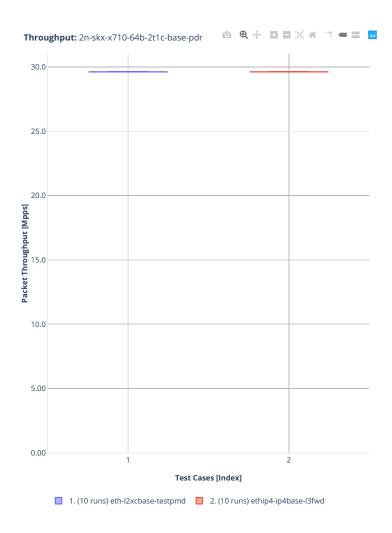

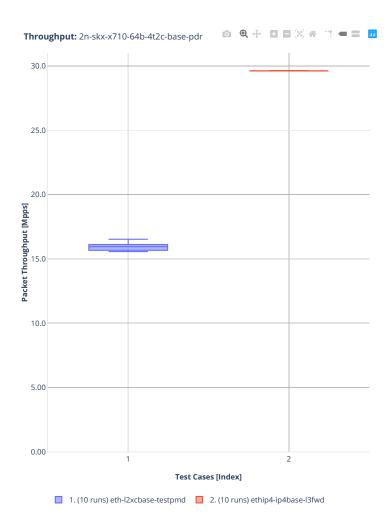

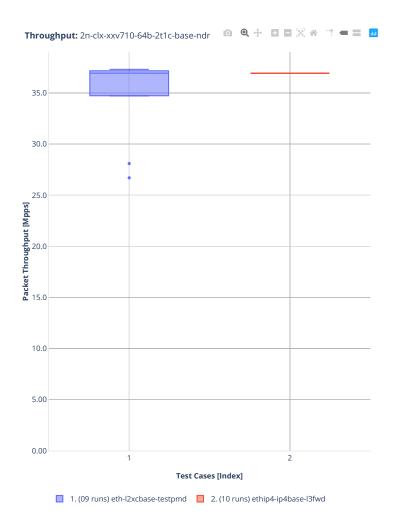

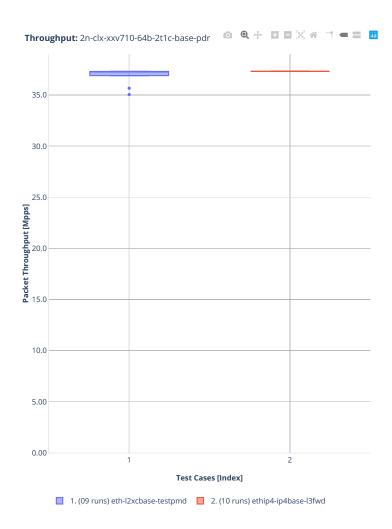

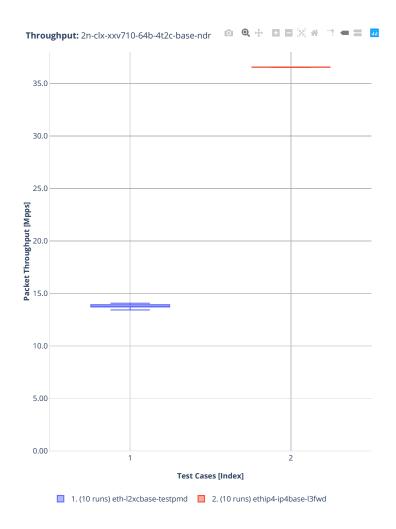

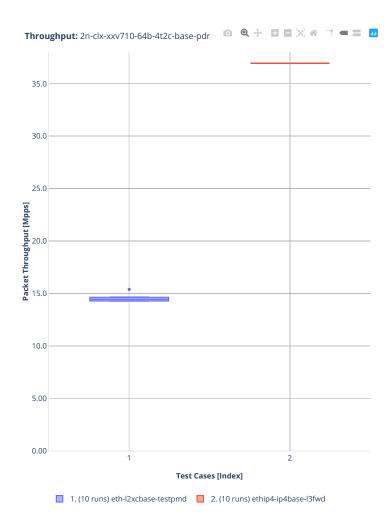

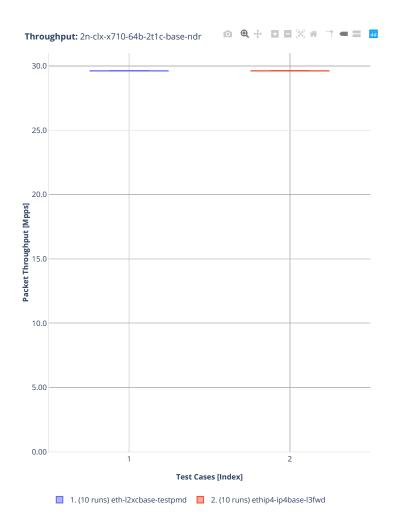

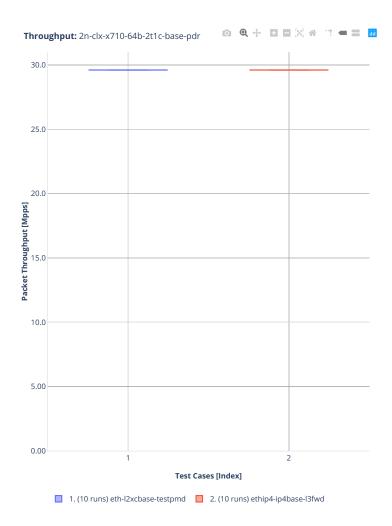

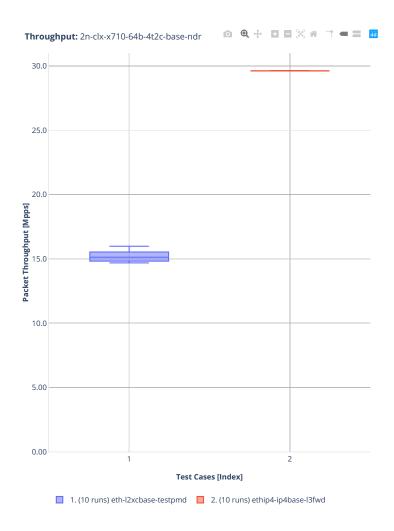

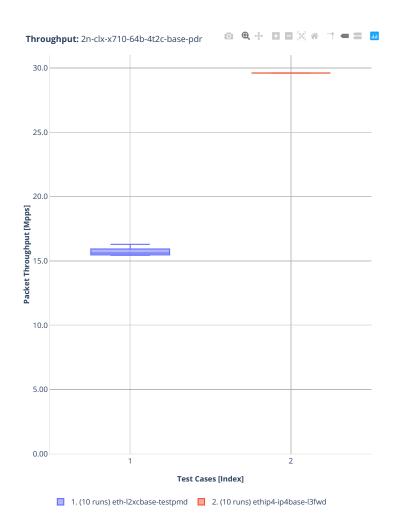

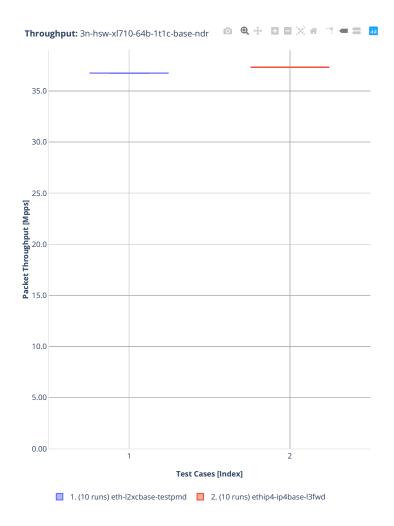

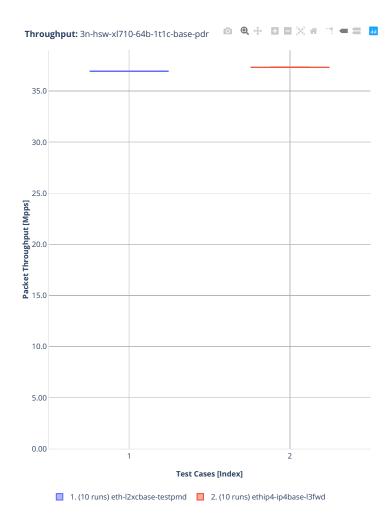

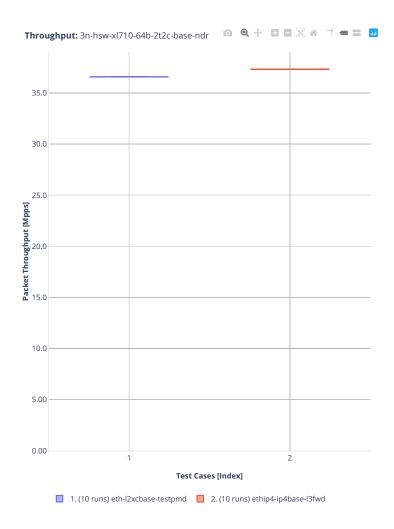

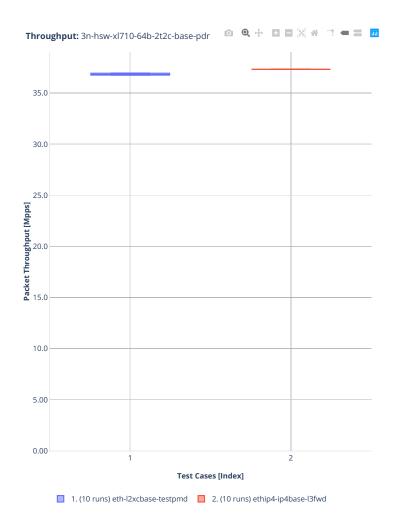

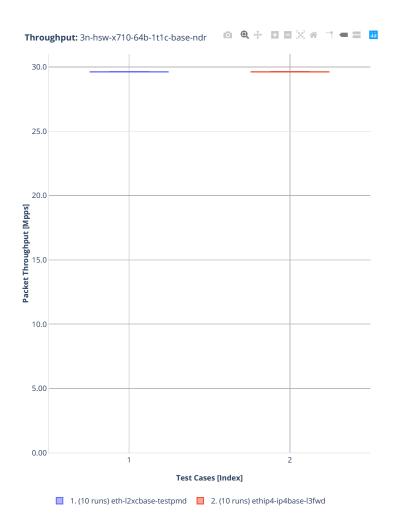

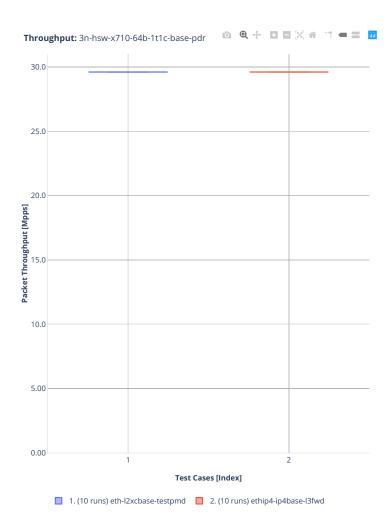

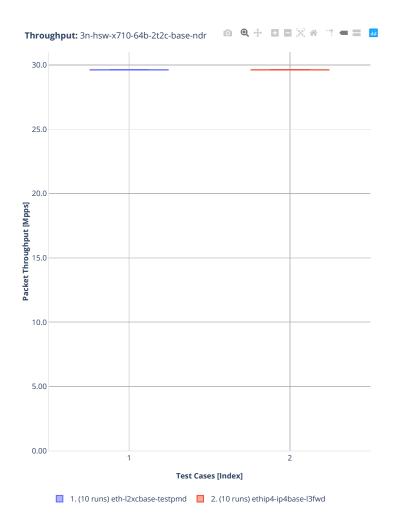

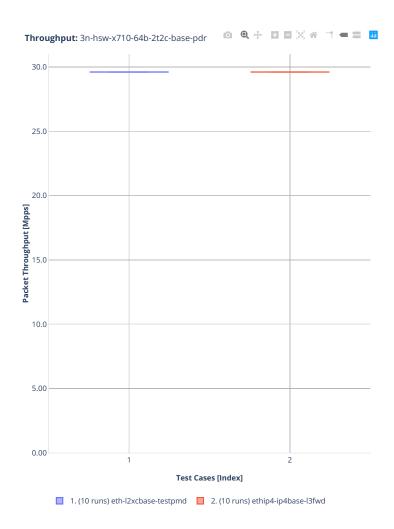

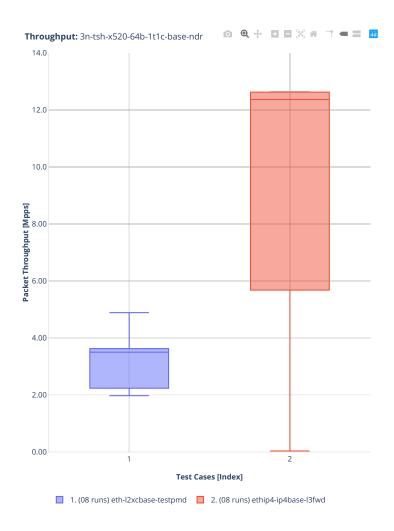

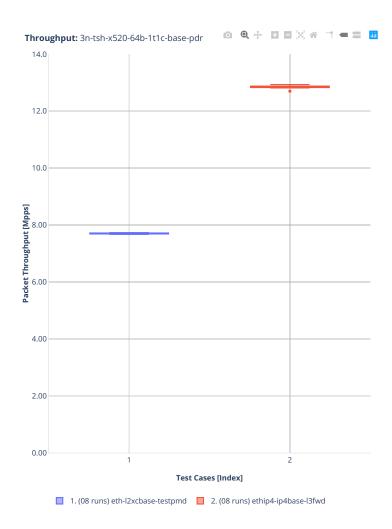

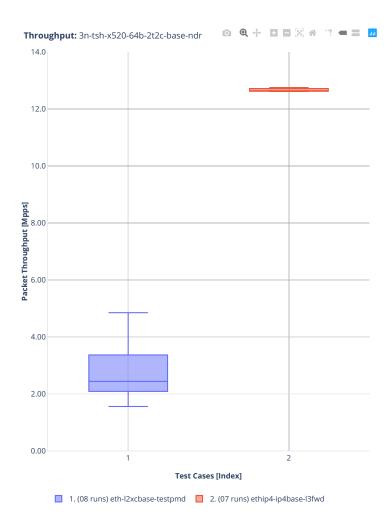

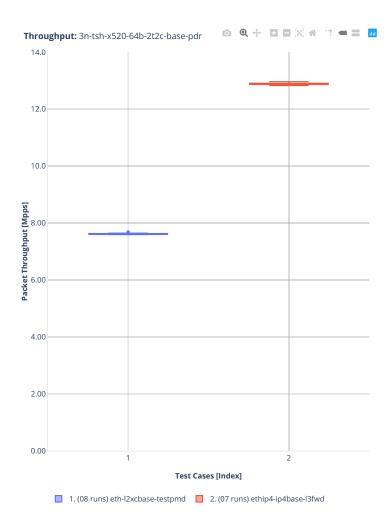

- Packet Throughput: NDR, PDR throughput graphs based on results from repeated same test job executions to verify repeatibility of measurements.

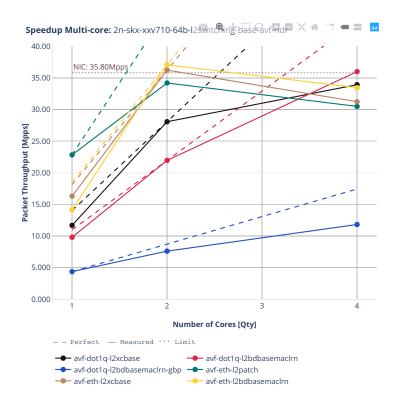

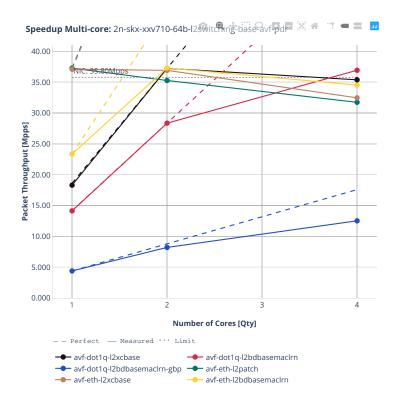

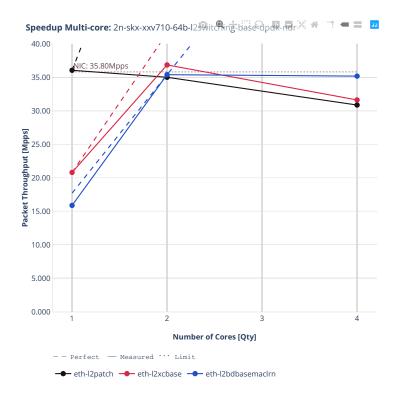

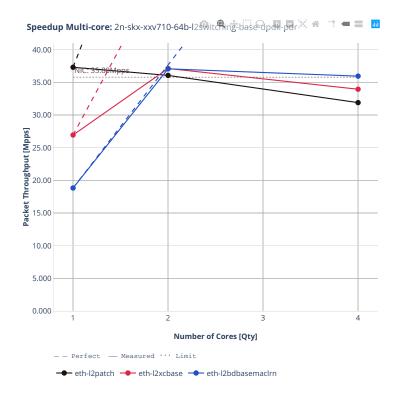

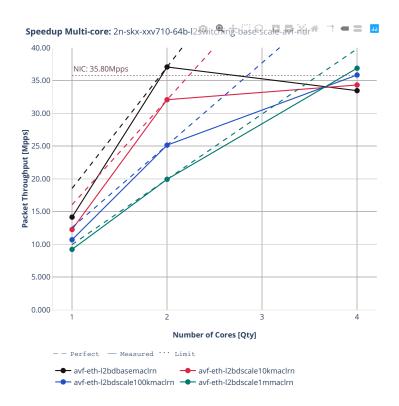

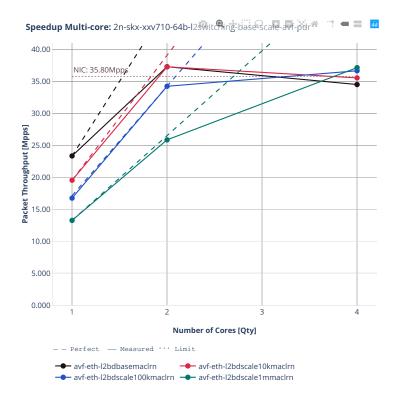

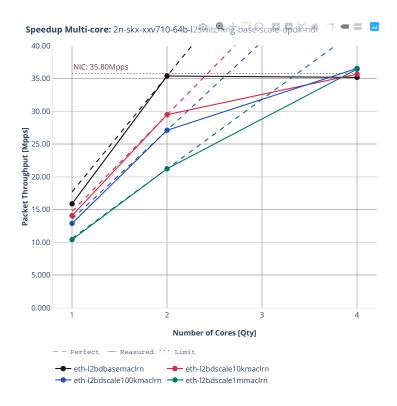

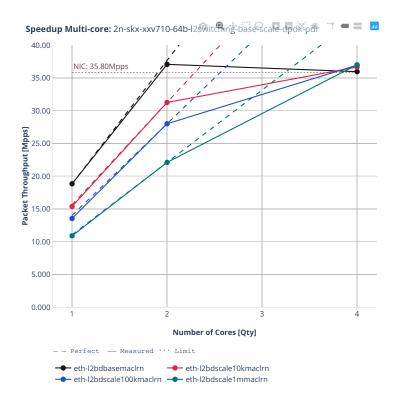

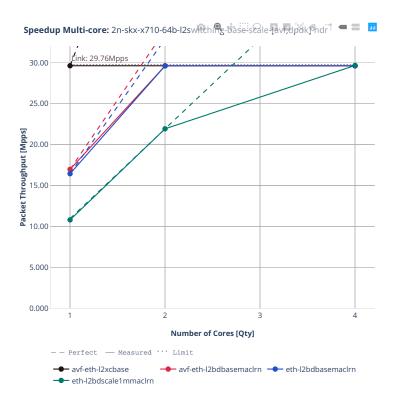

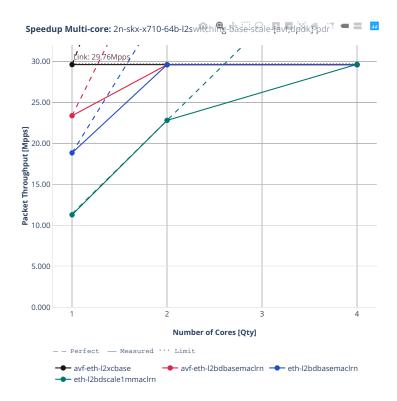

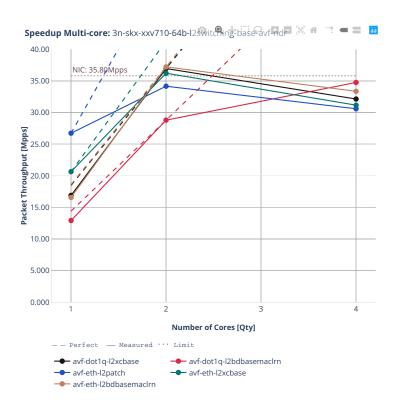

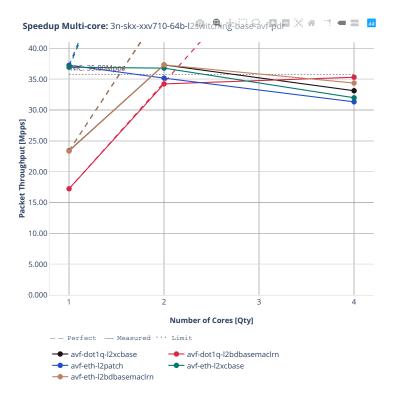

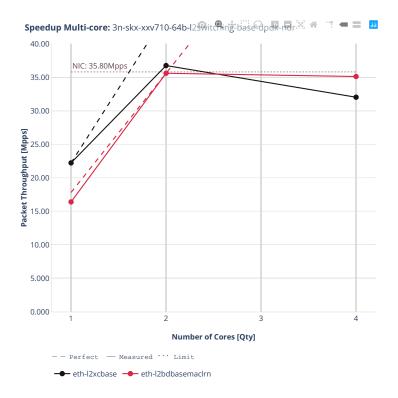

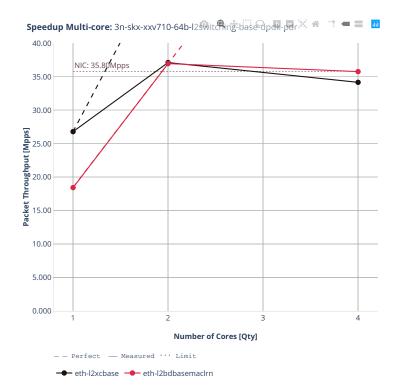

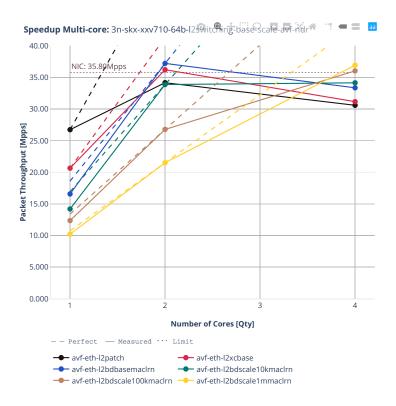

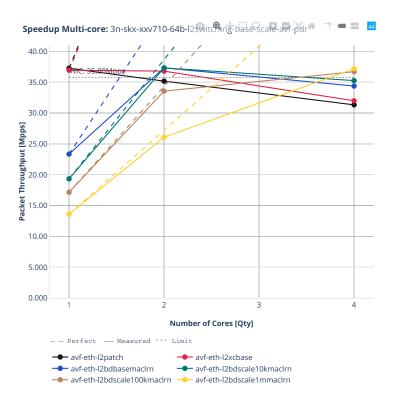

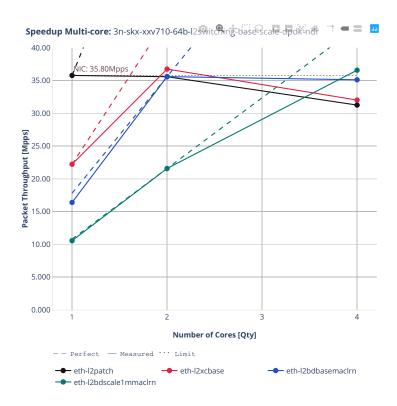

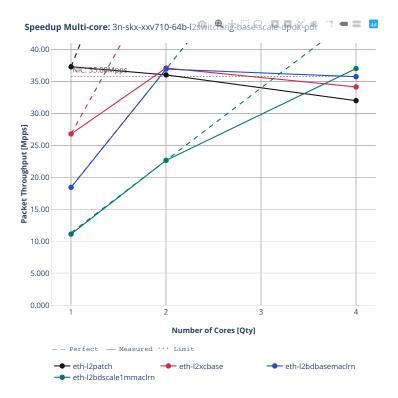

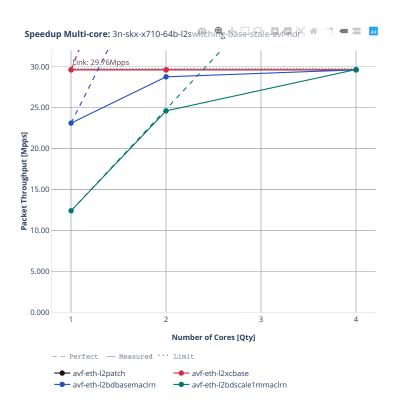

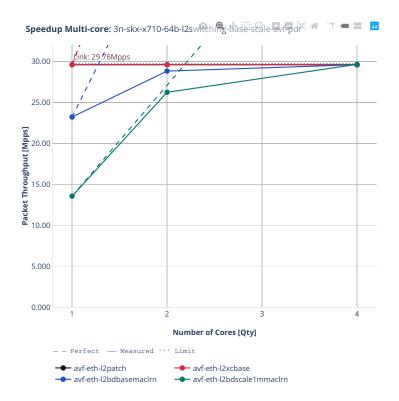

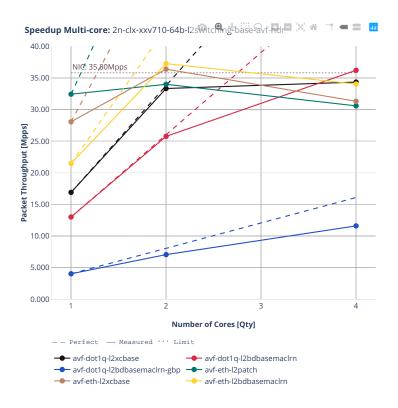

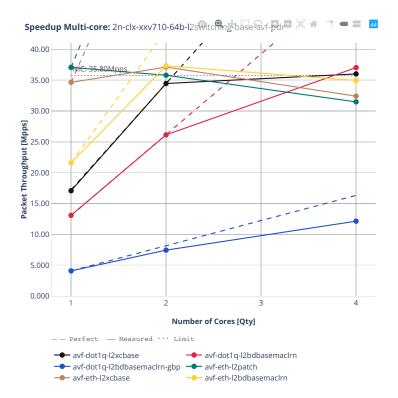

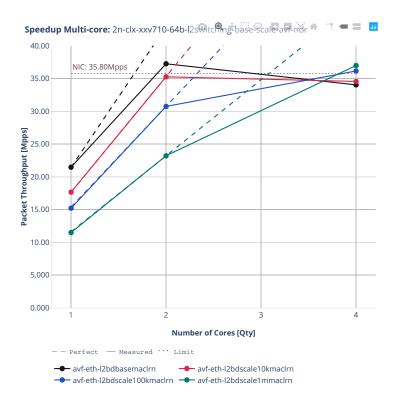

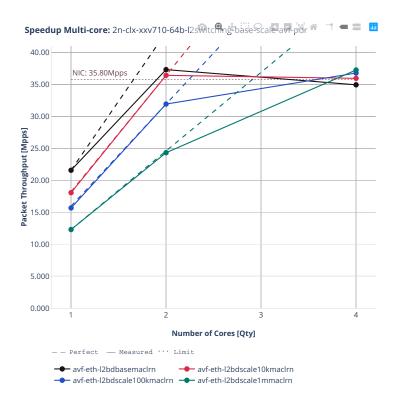

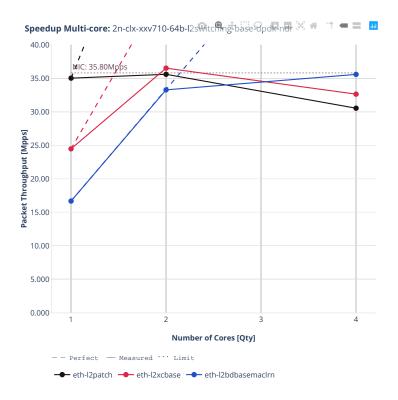

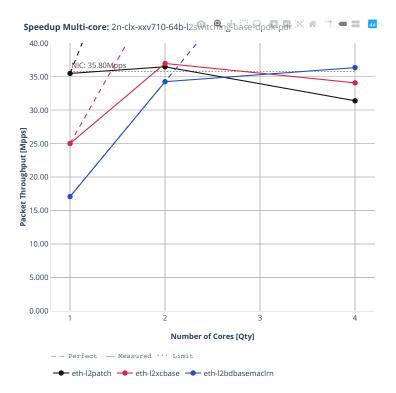

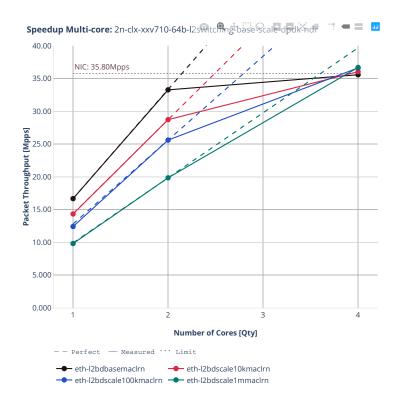

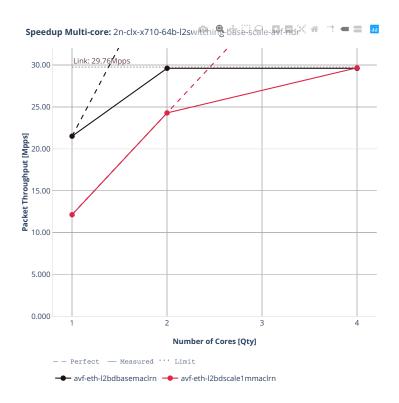

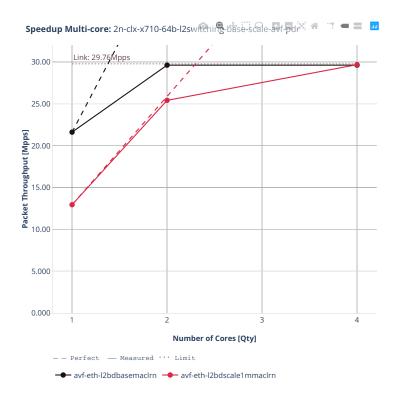

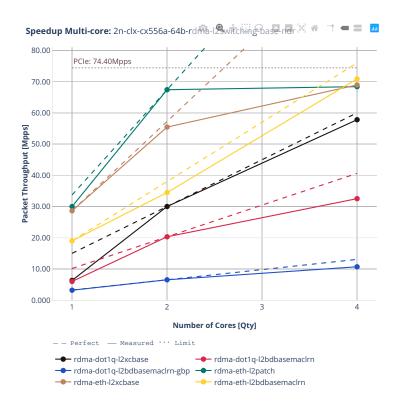

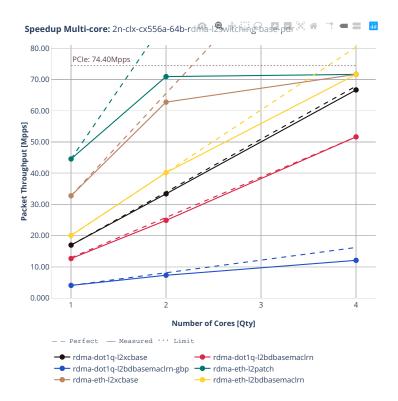

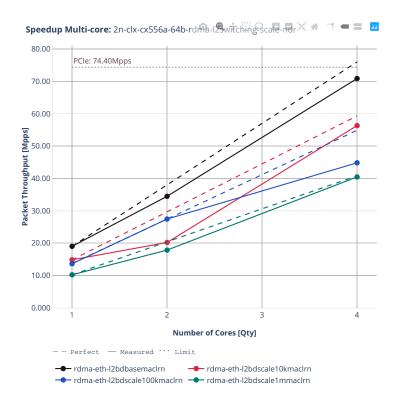

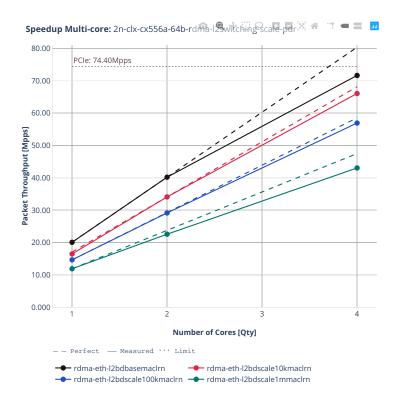

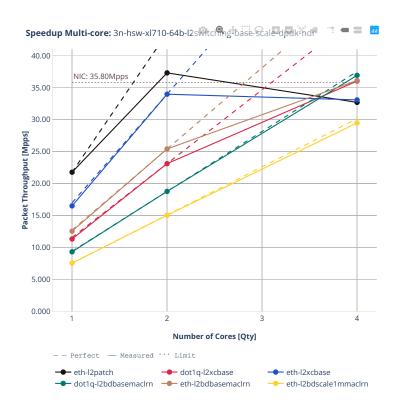

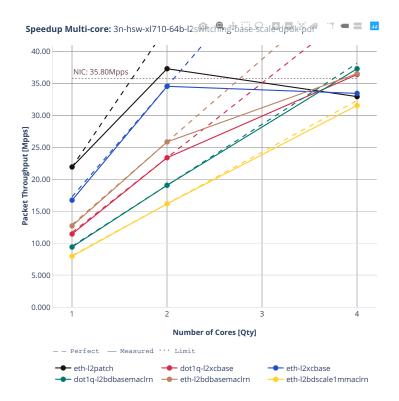

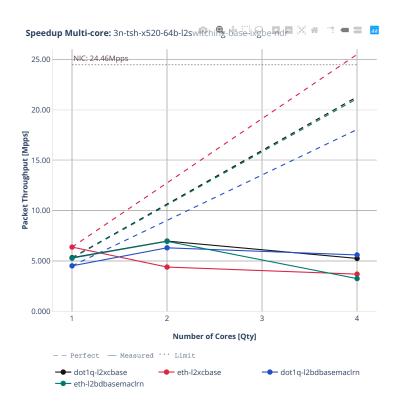

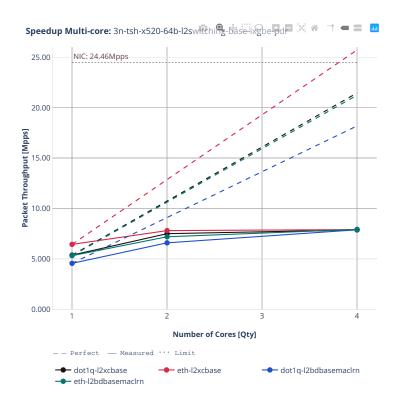

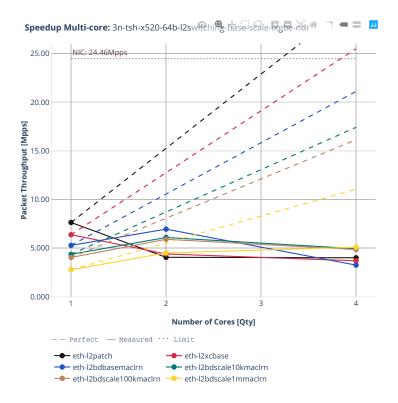

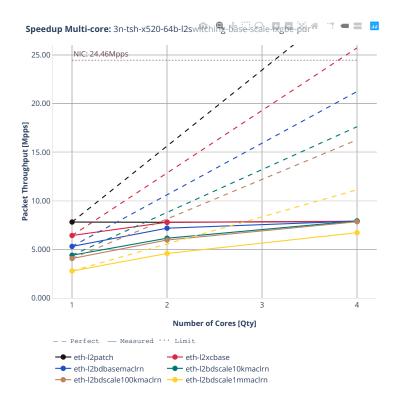

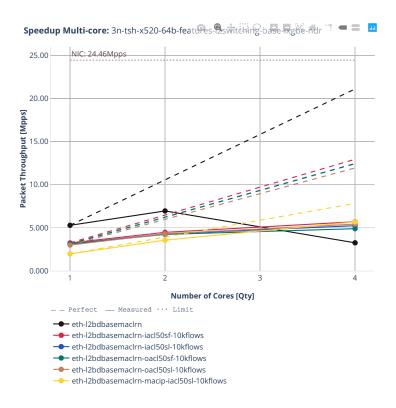

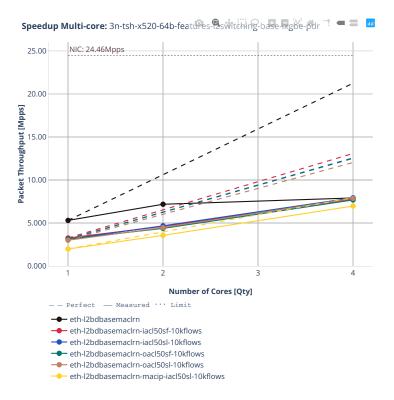

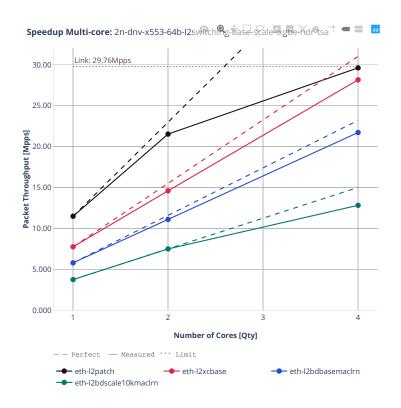

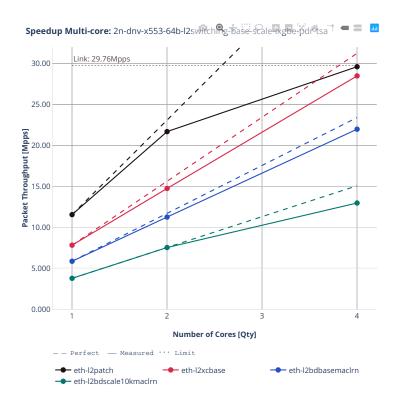

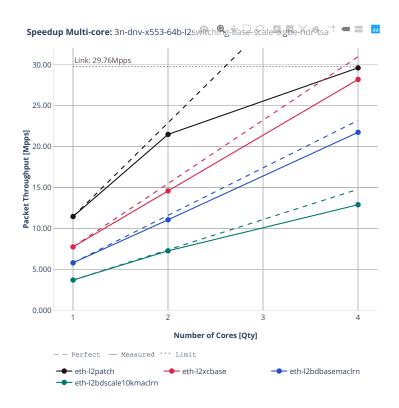

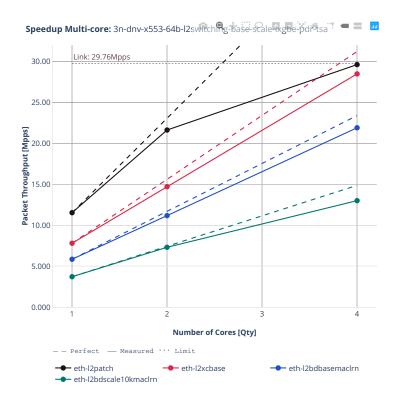

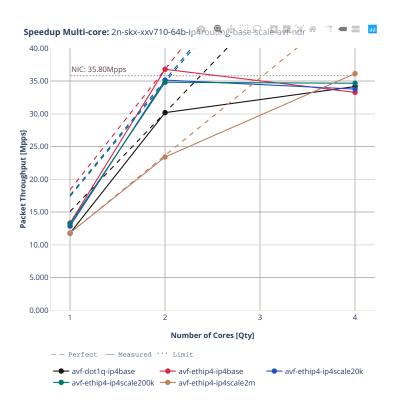

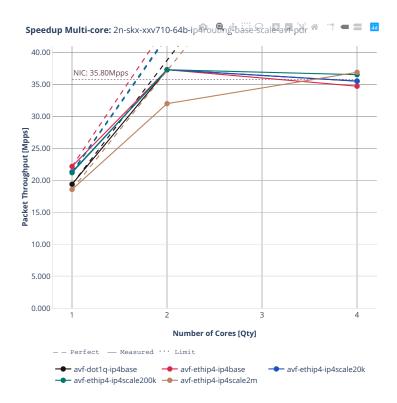

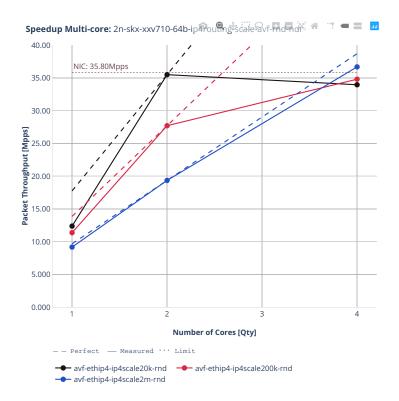

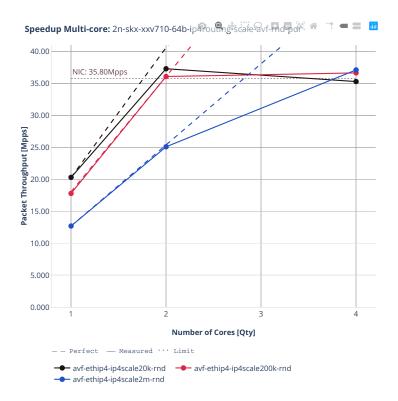

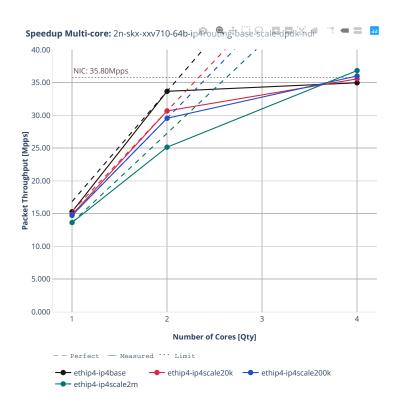

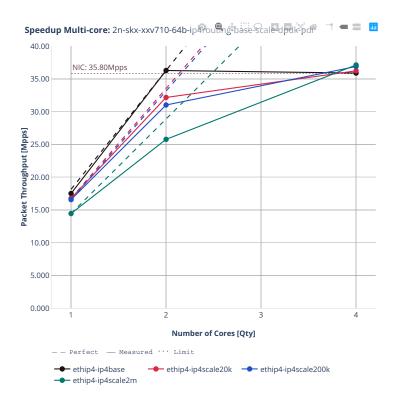

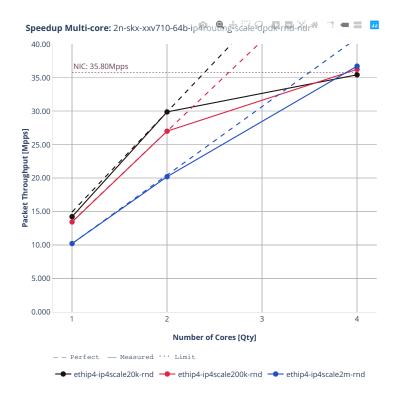

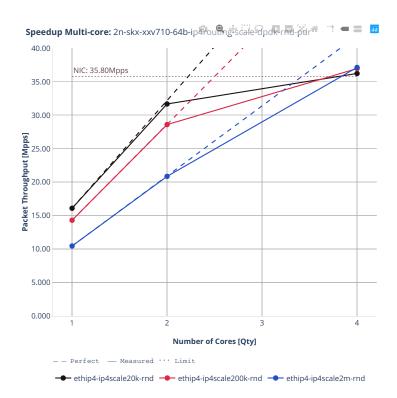

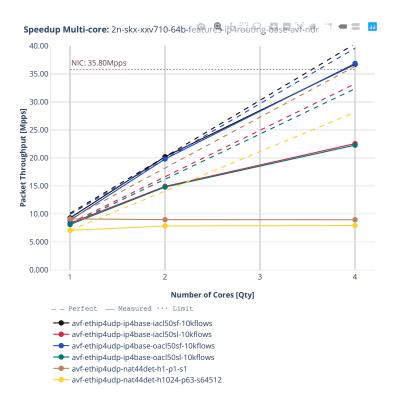

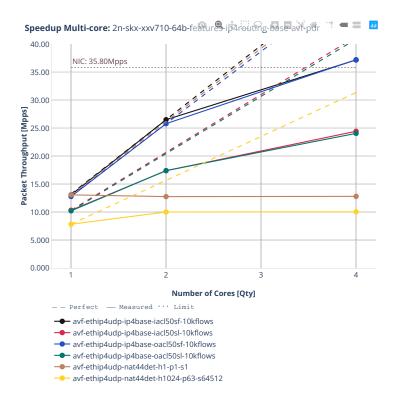

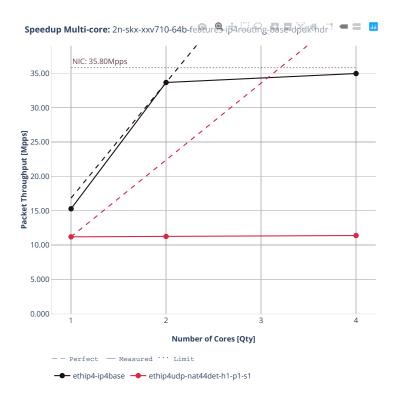

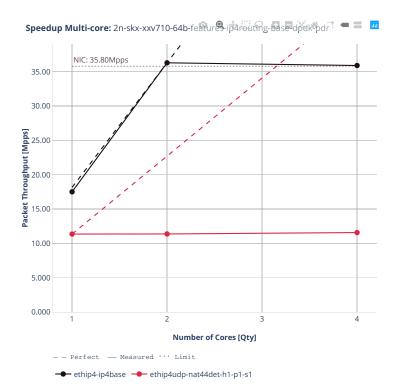

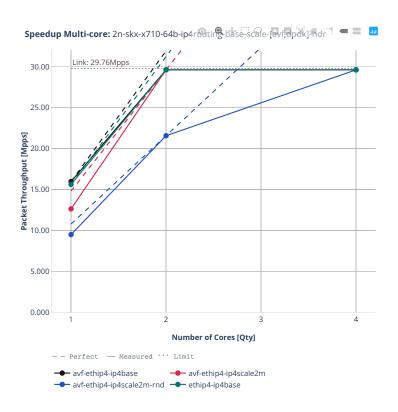

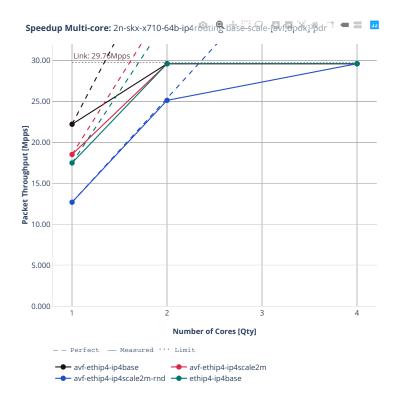

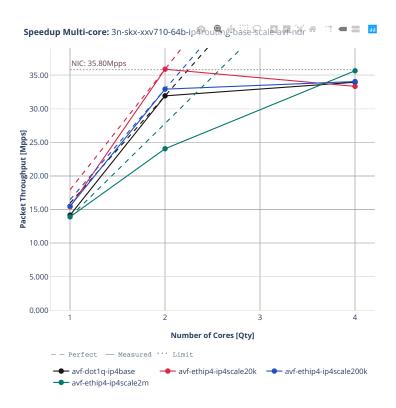

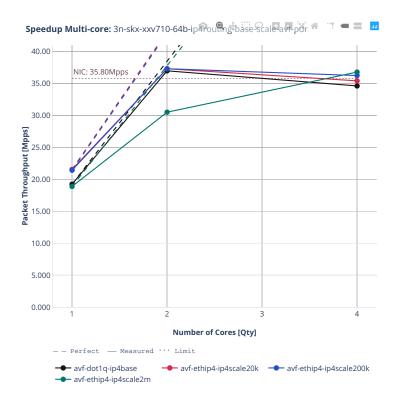

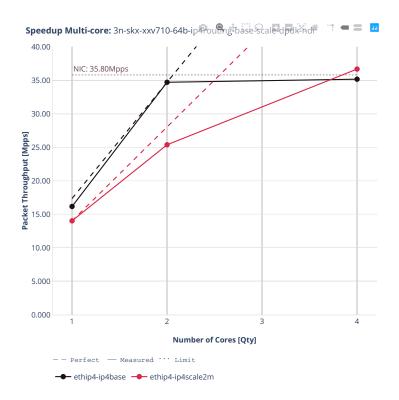

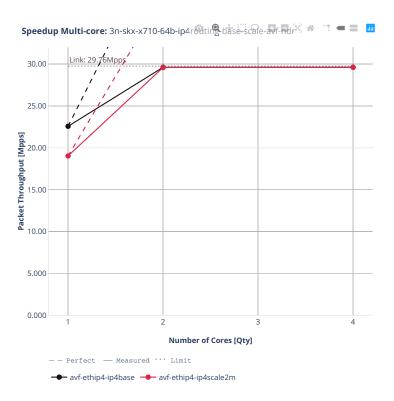

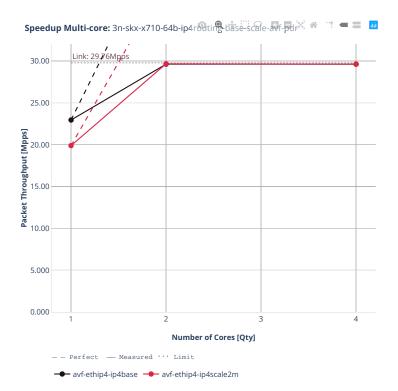

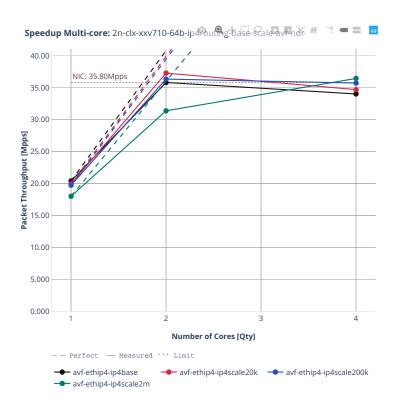

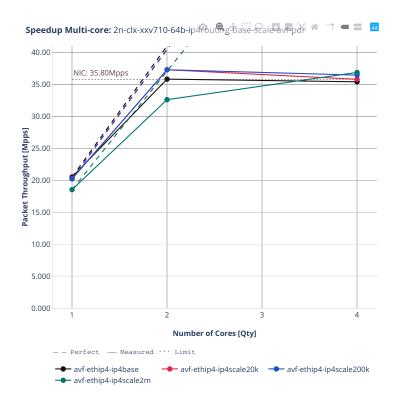

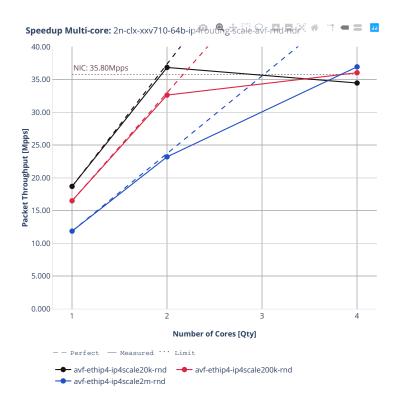

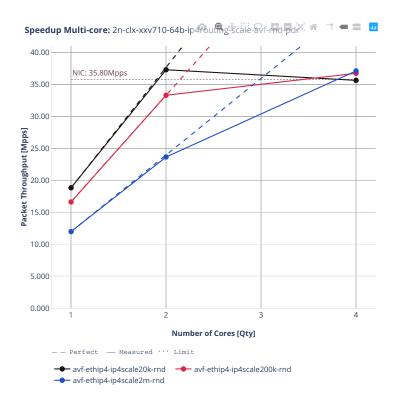

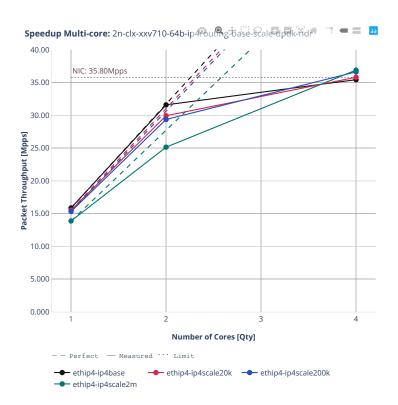

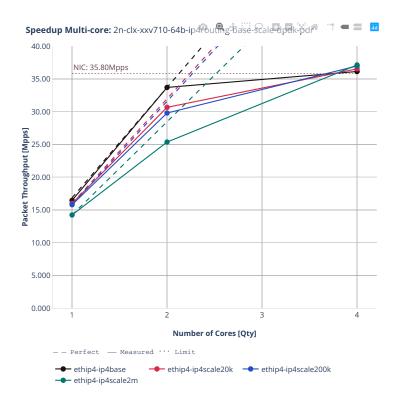

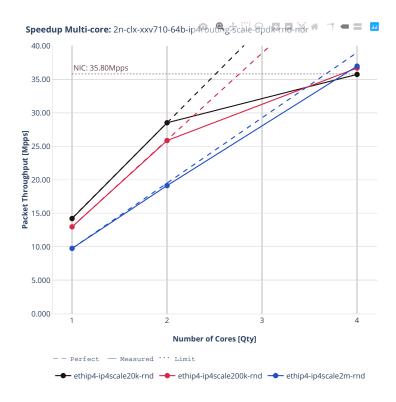

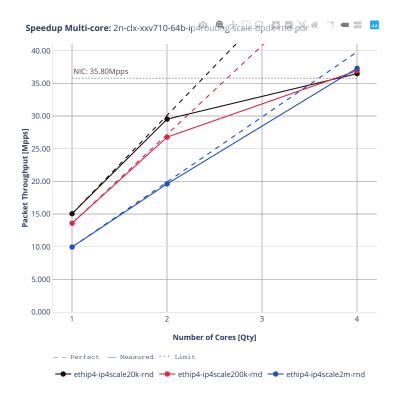

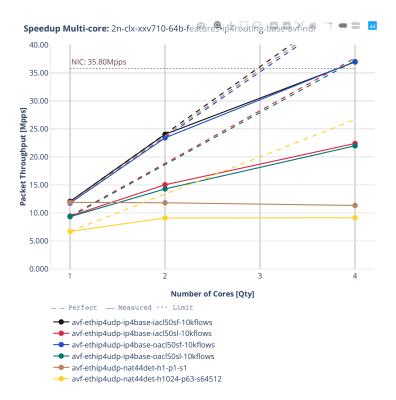

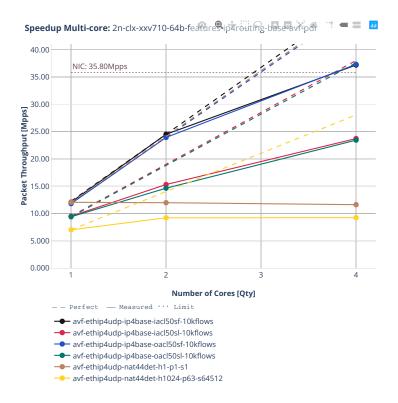

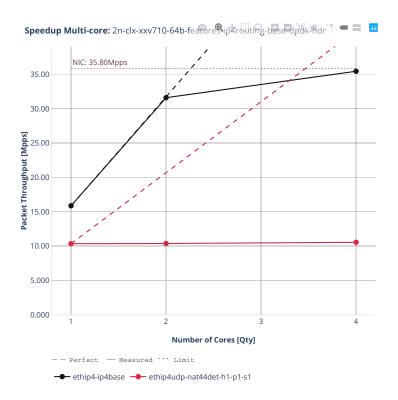

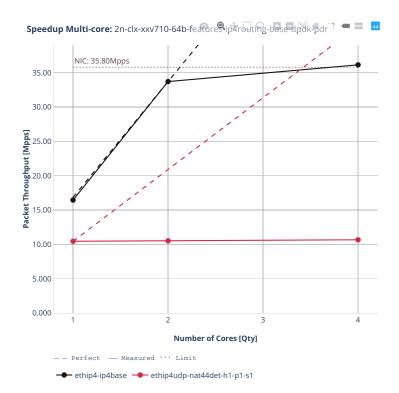

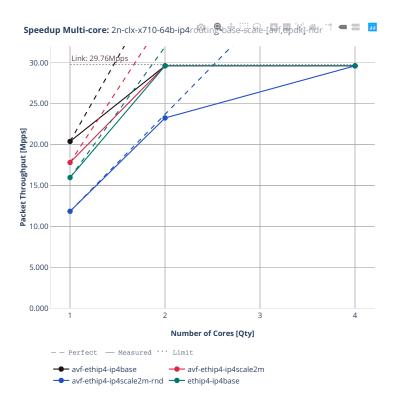

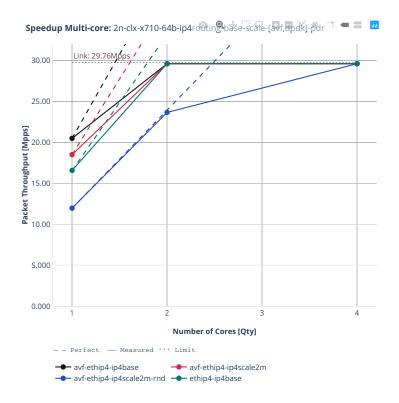

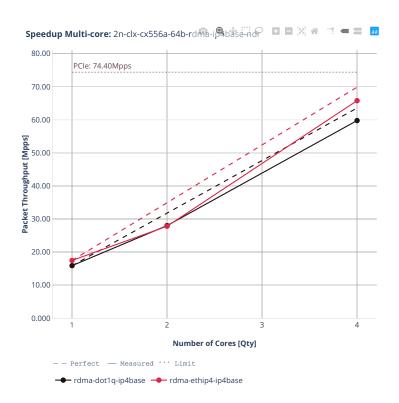

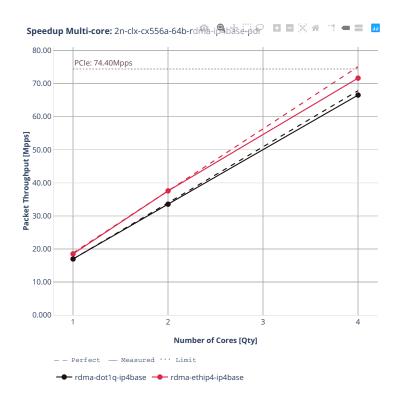

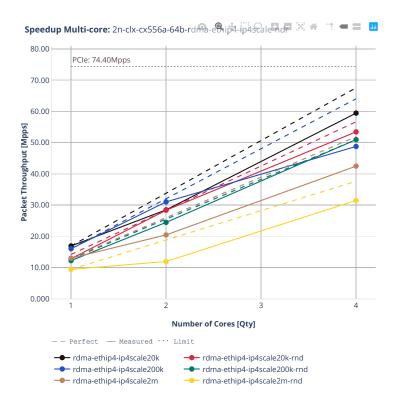

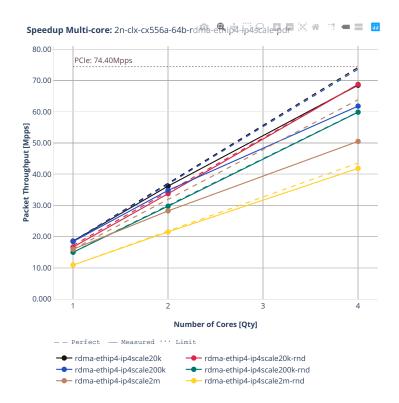

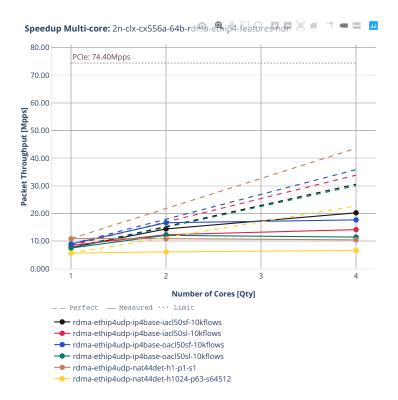

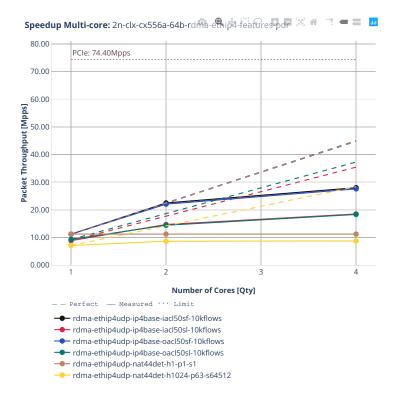

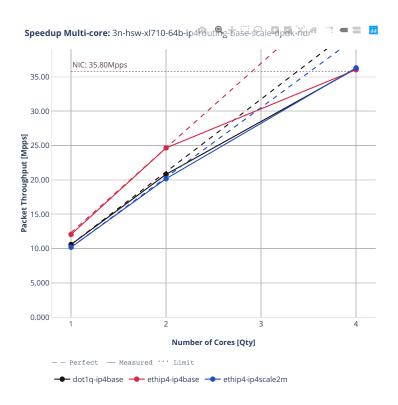

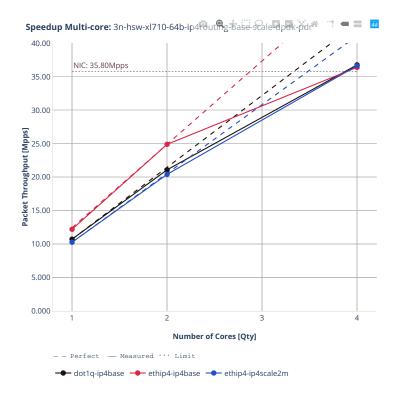

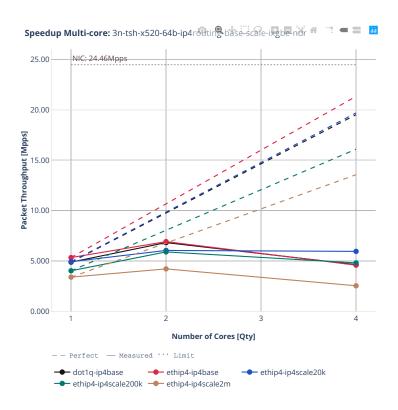

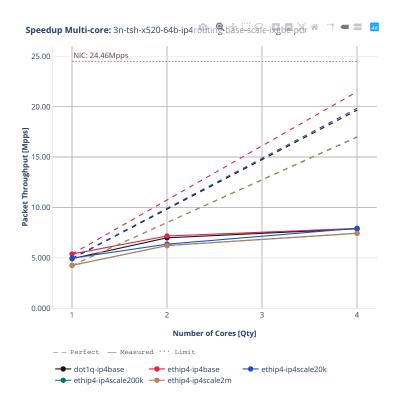

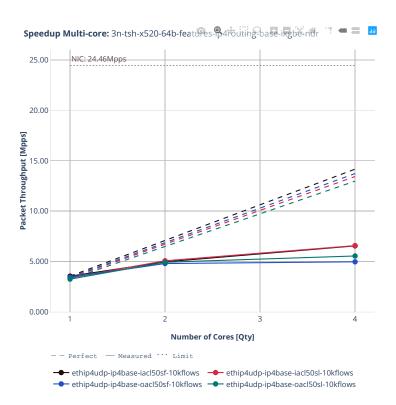

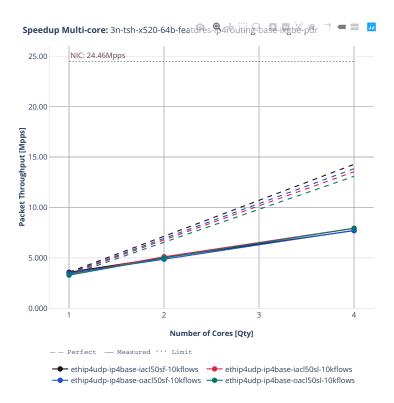

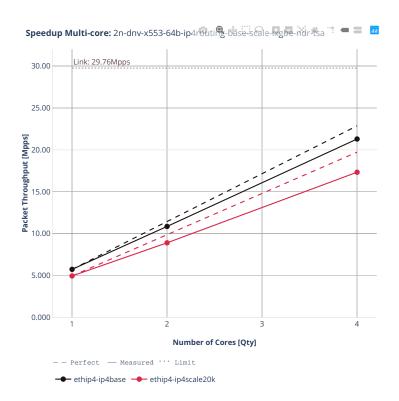

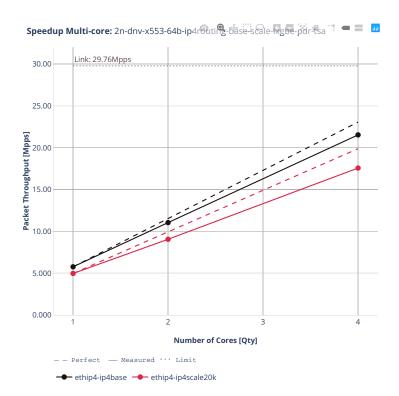

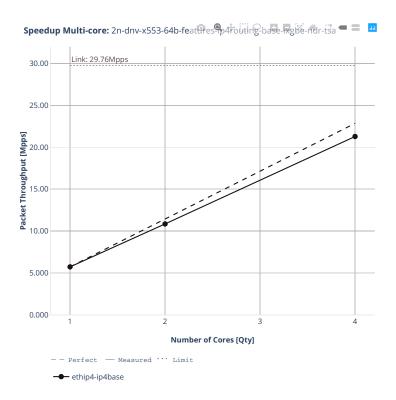

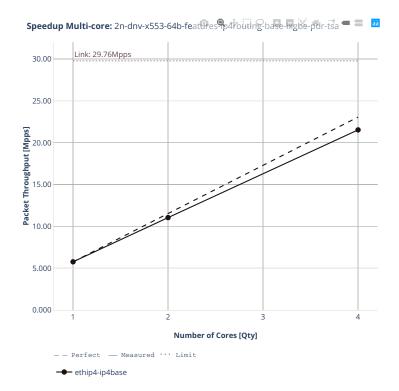

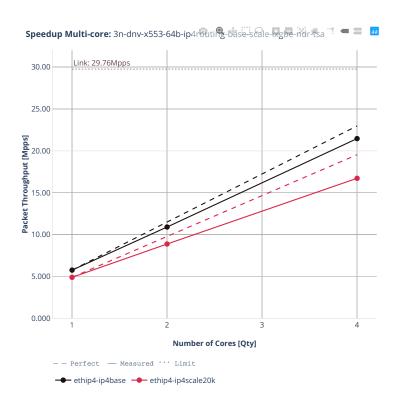

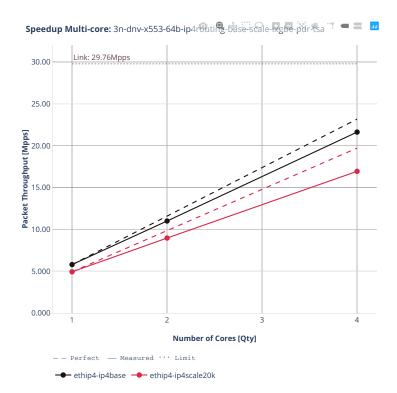

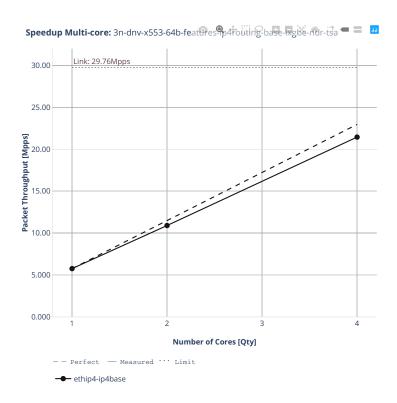

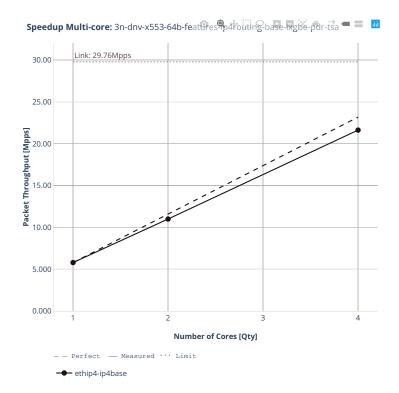

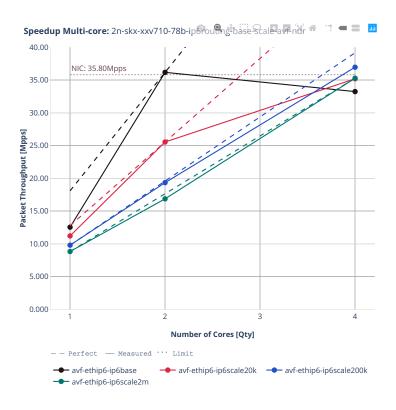

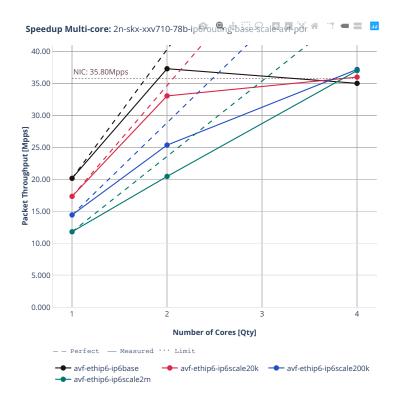

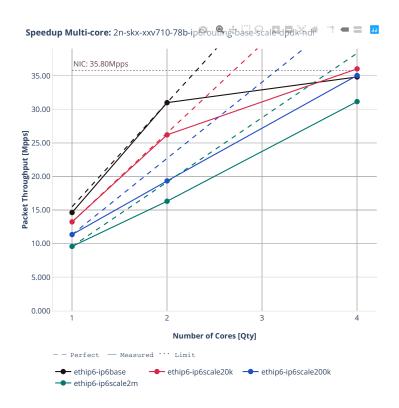

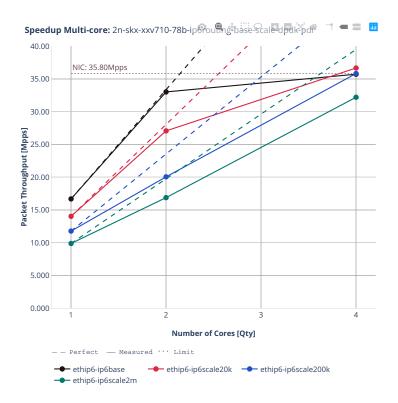

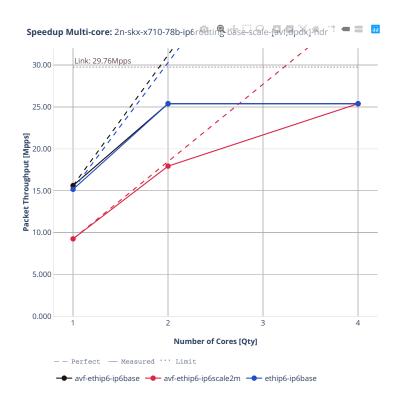

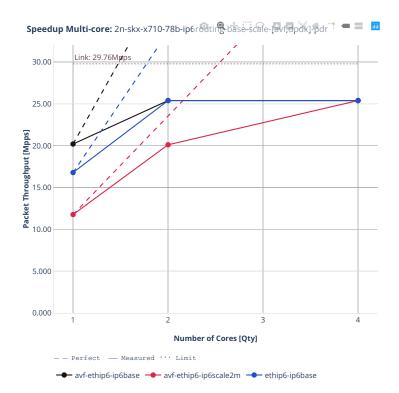

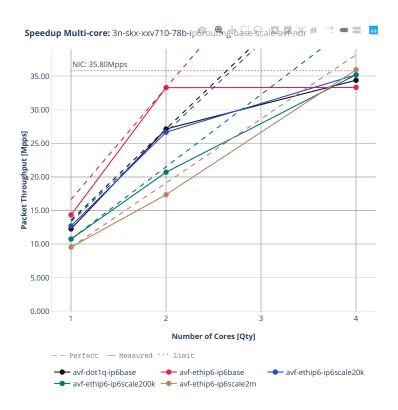

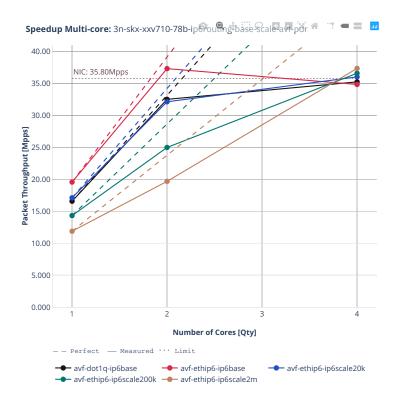

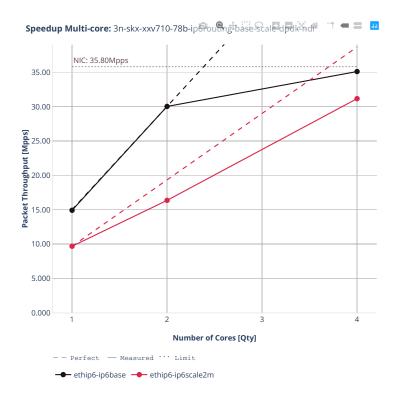

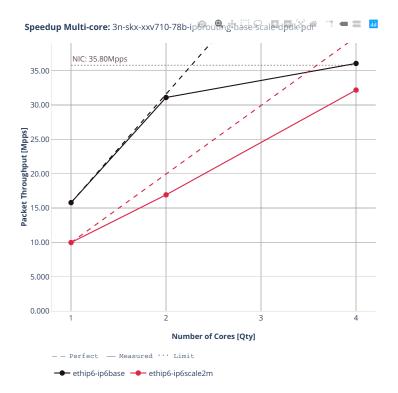

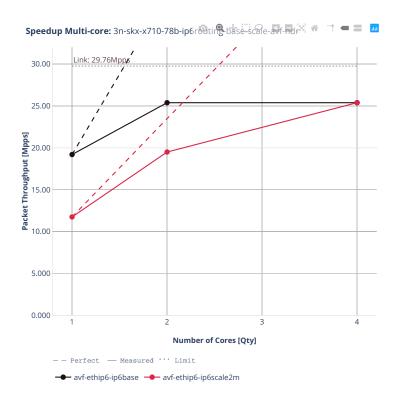

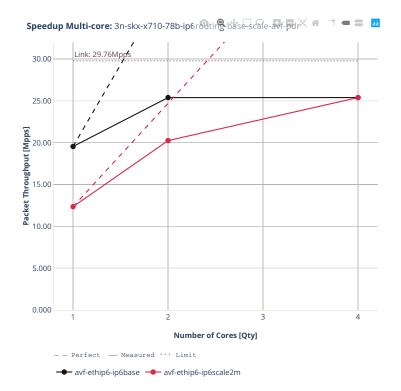

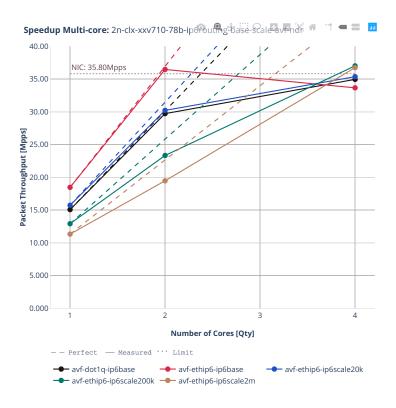

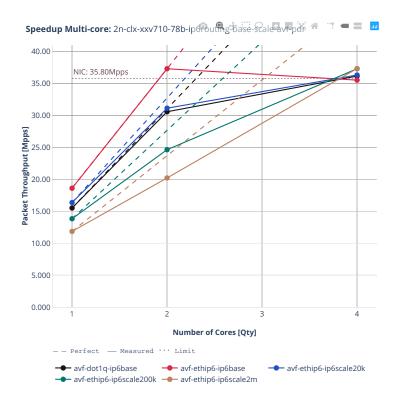

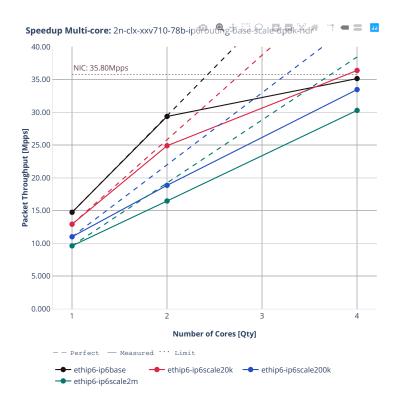

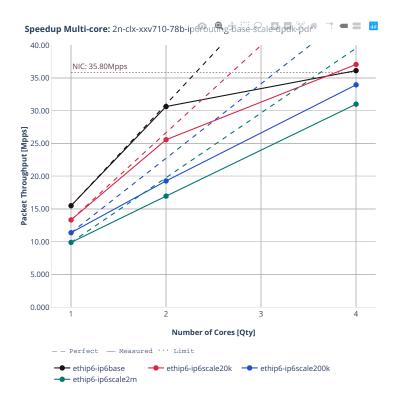

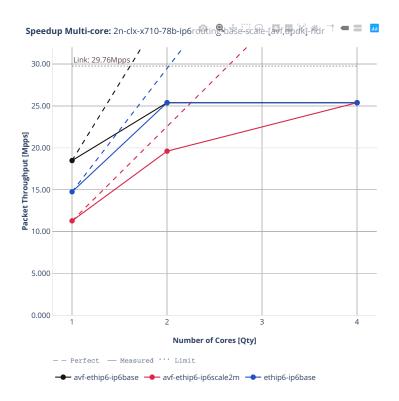

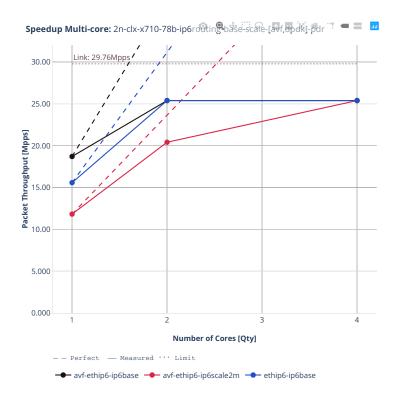

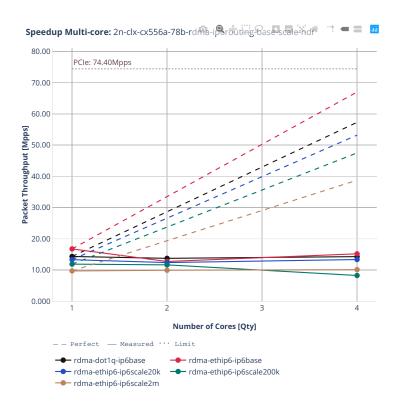

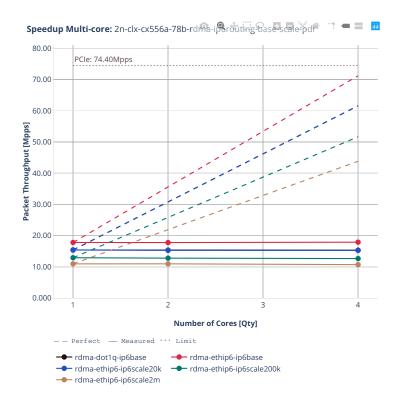

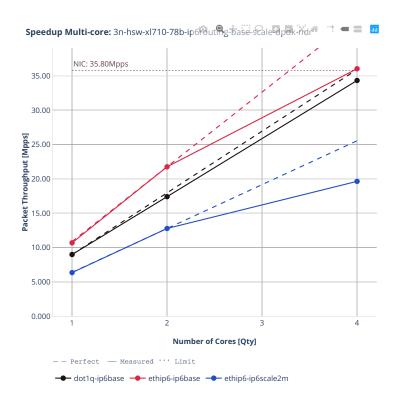

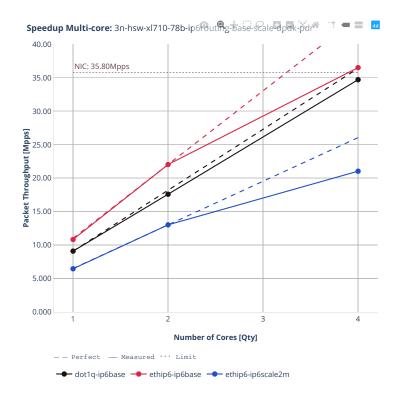

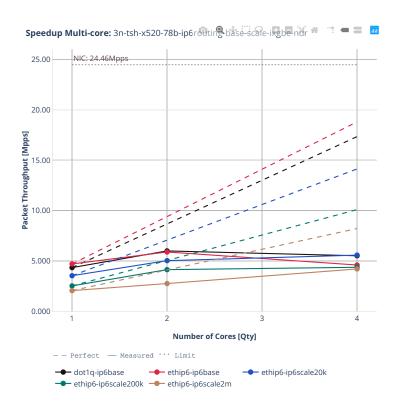

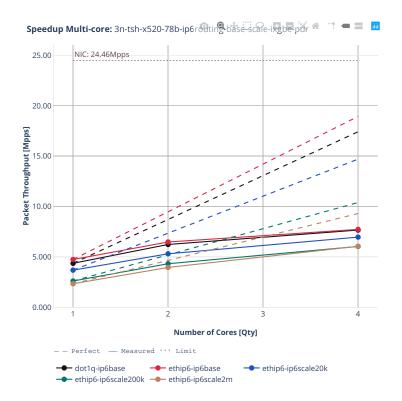

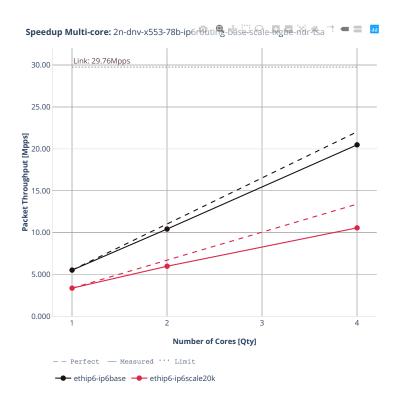

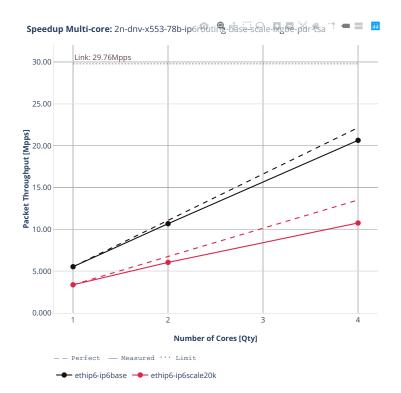

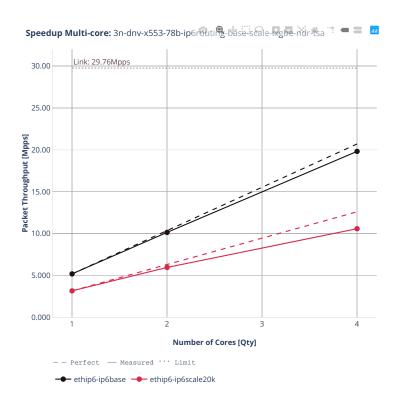

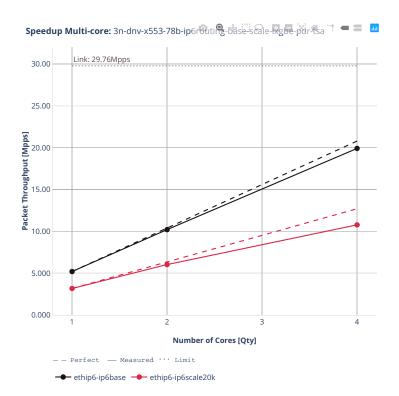

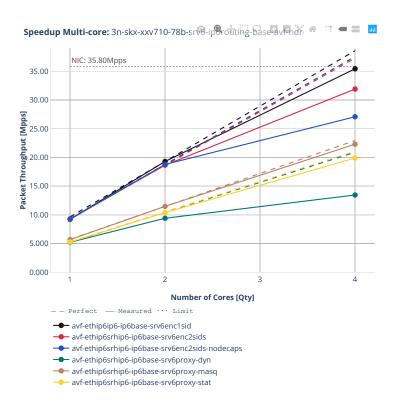

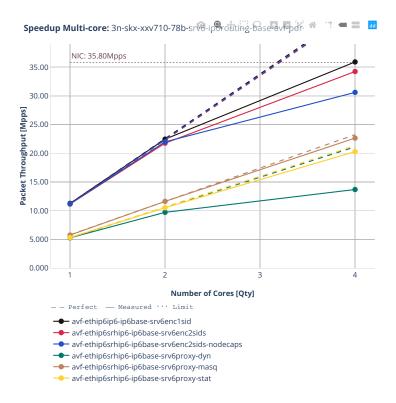

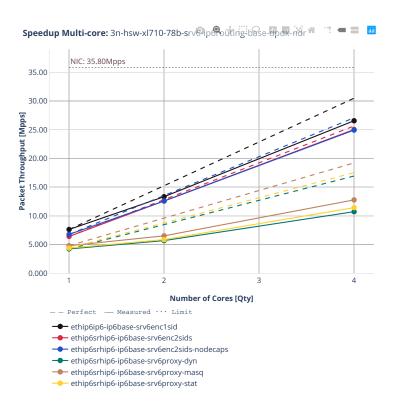

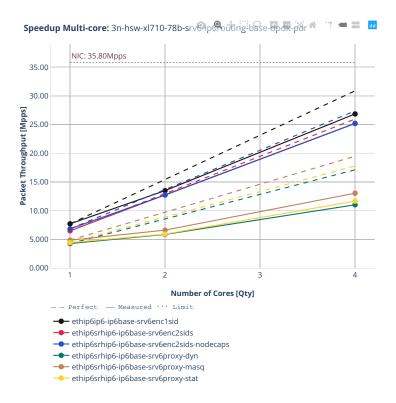

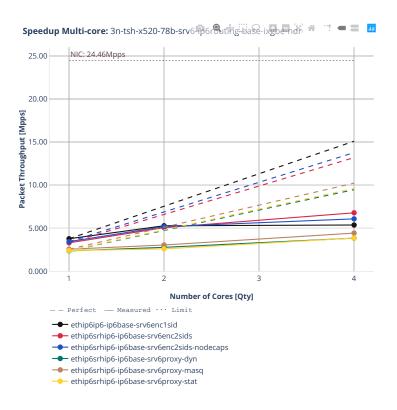

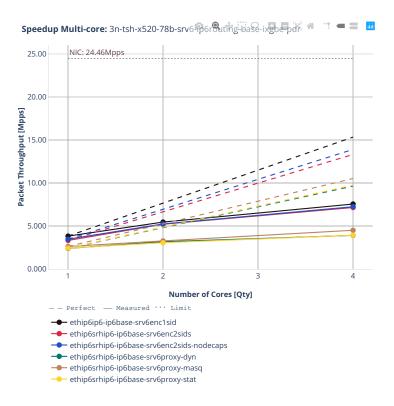

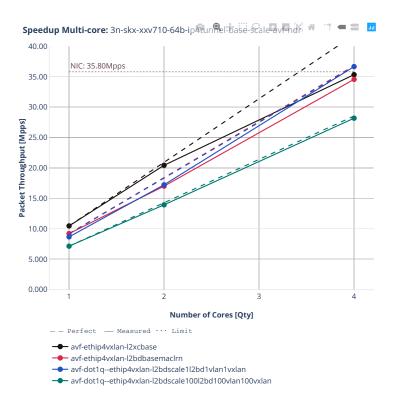

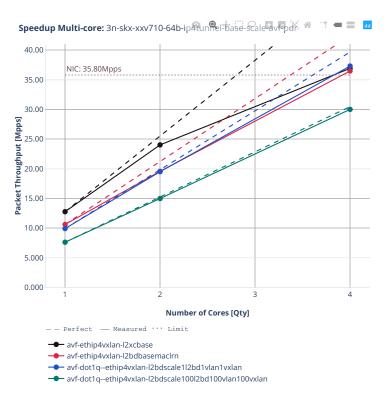

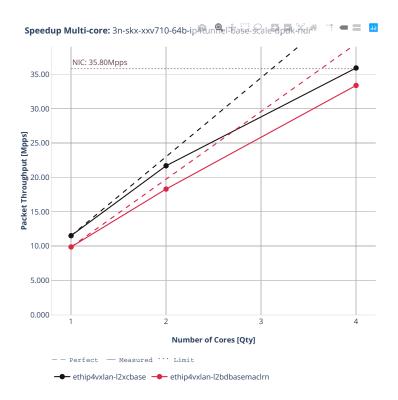

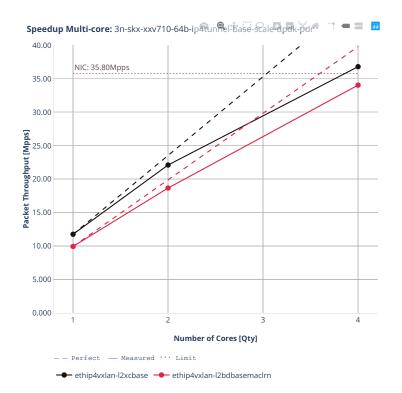

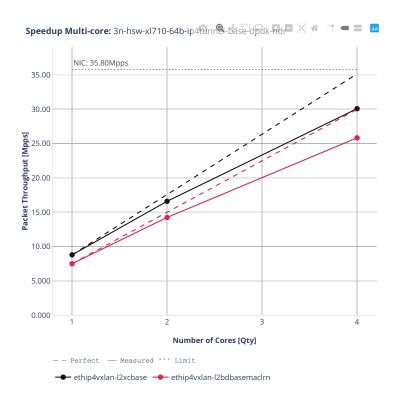

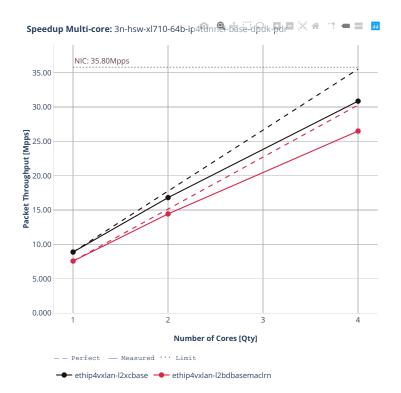

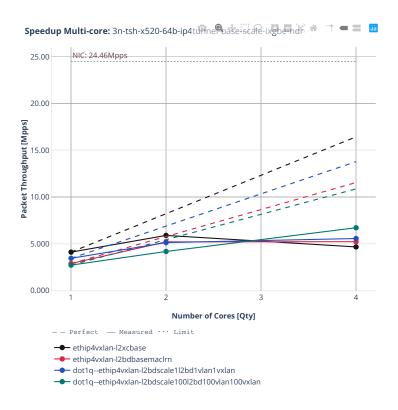

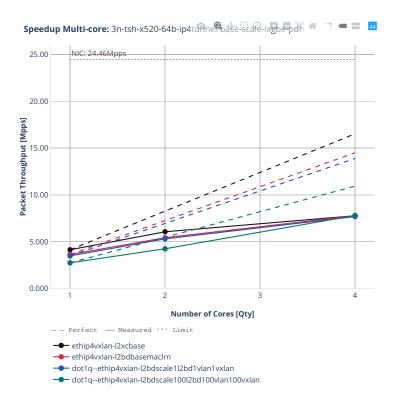

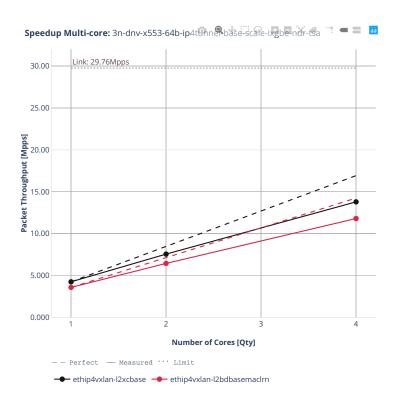

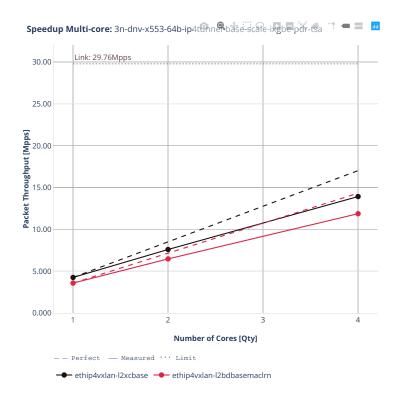

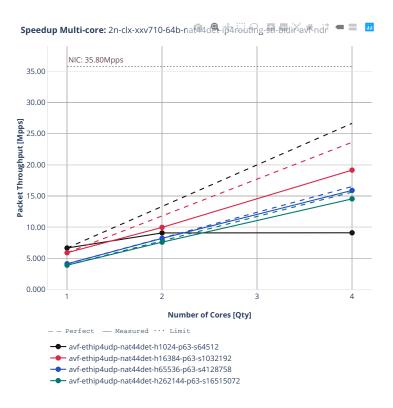

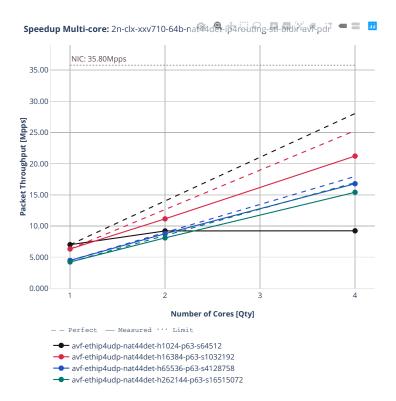

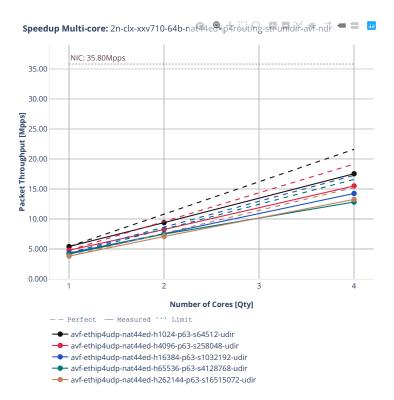

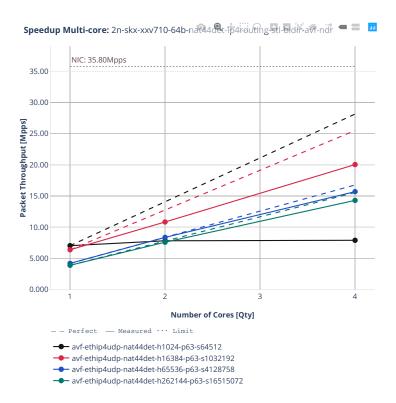

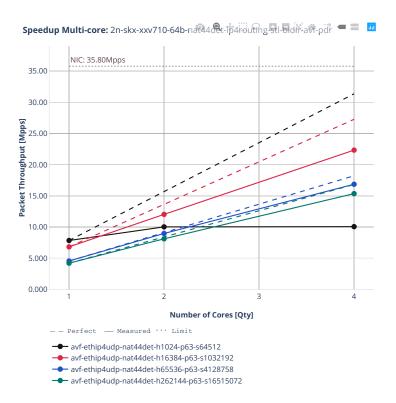

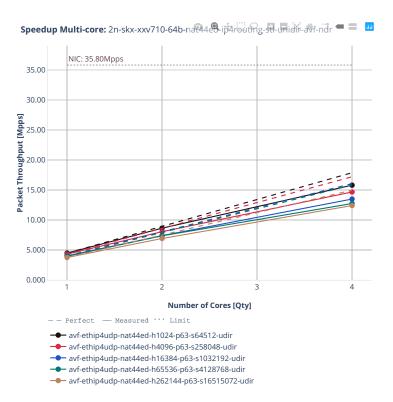

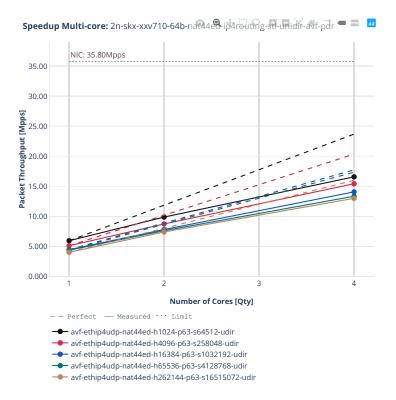

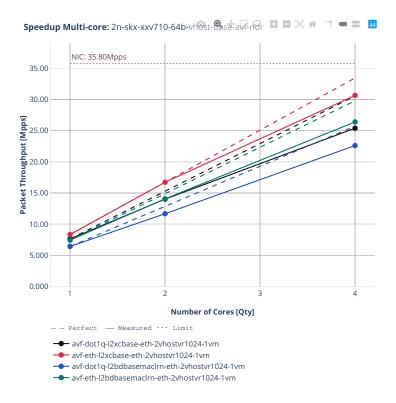

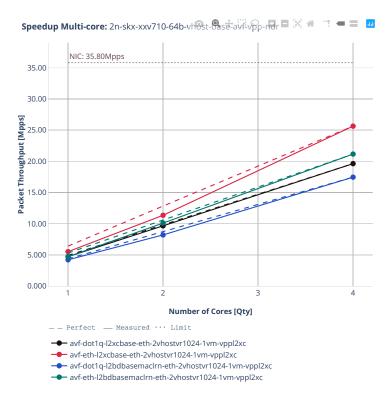

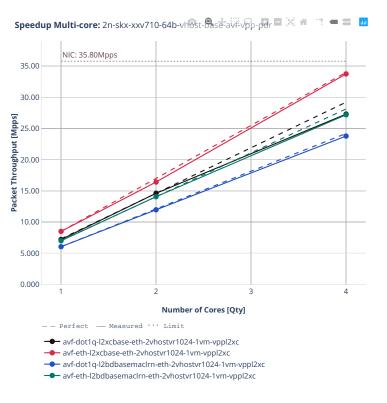

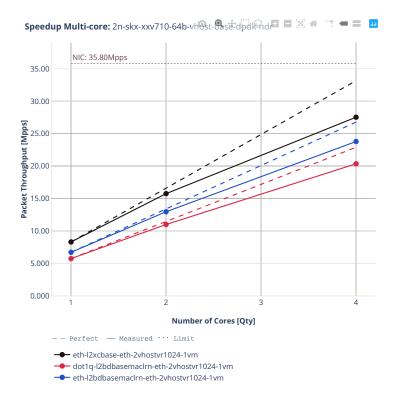

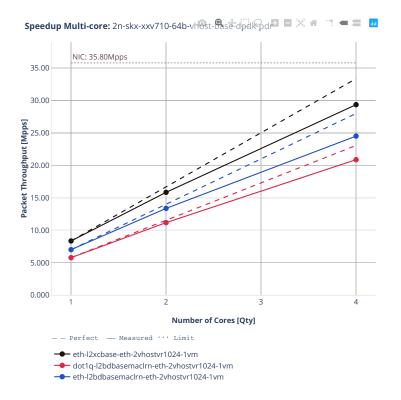

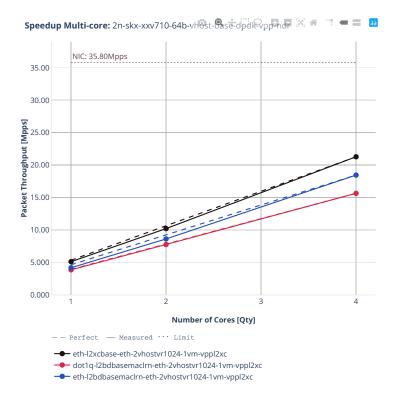

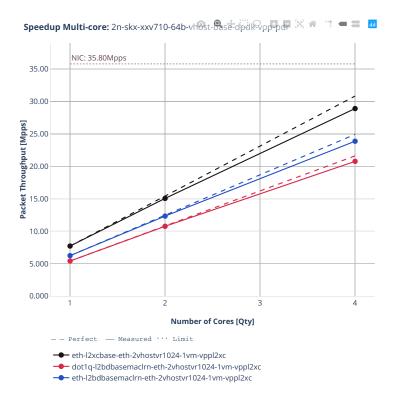

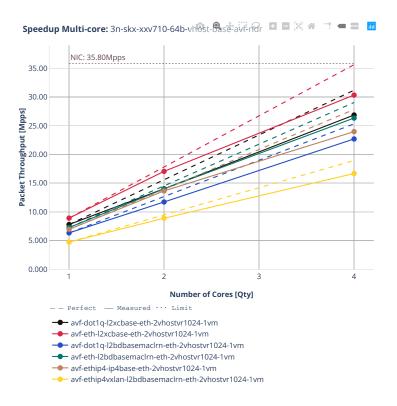

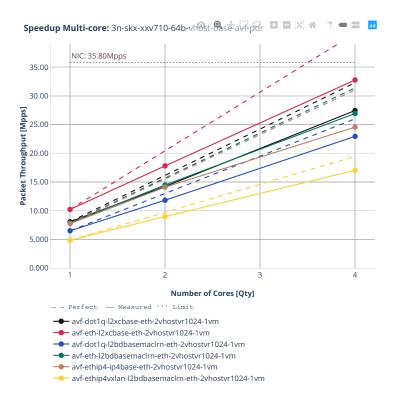

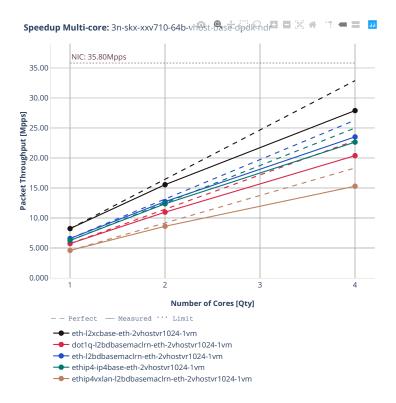

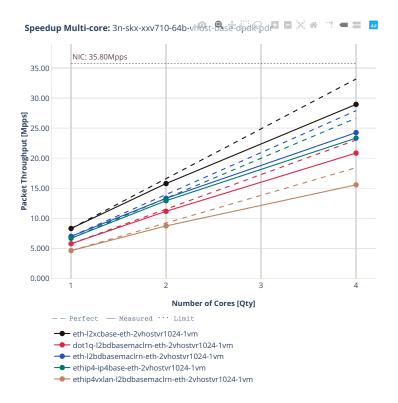

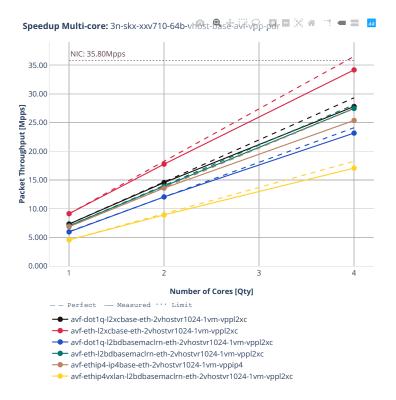

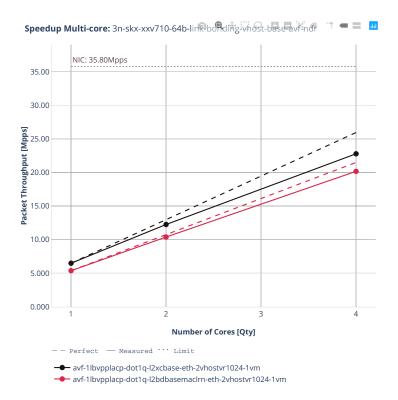

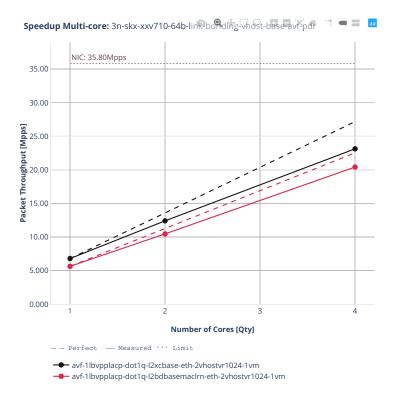

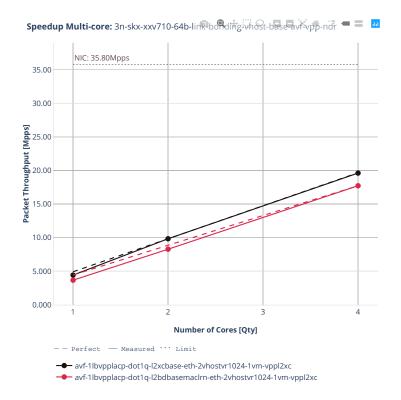

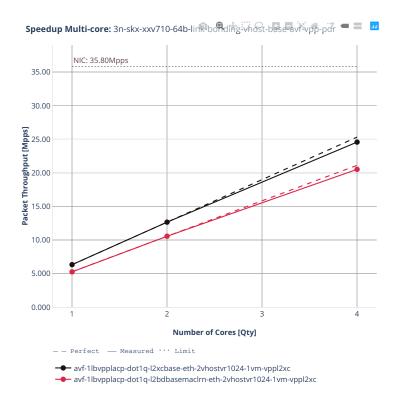

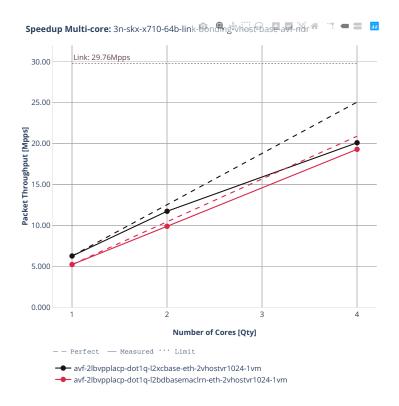

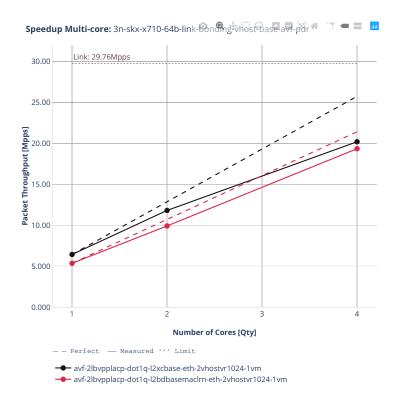

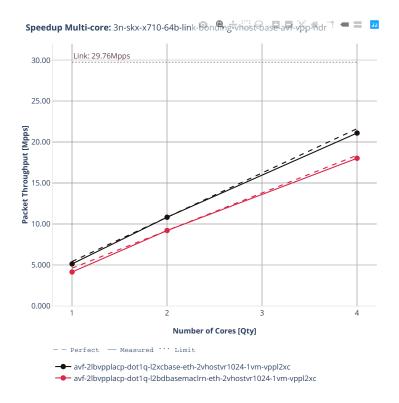

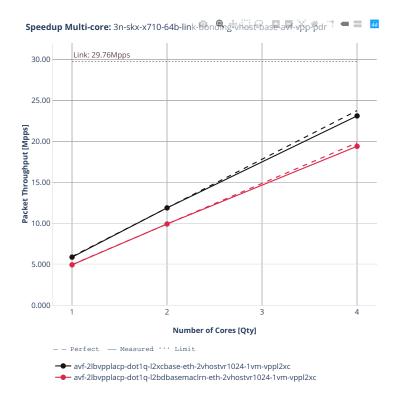

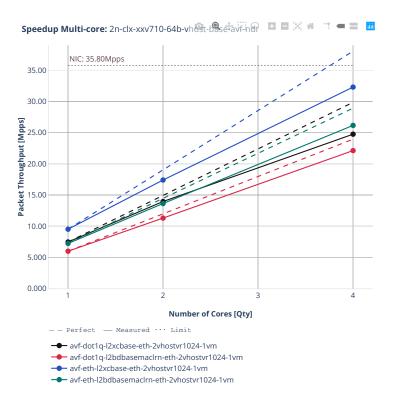

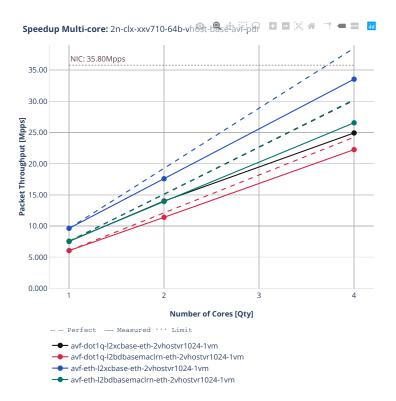

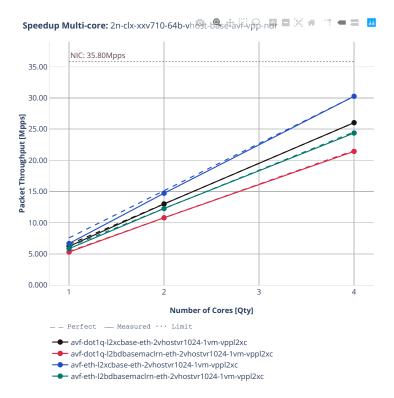

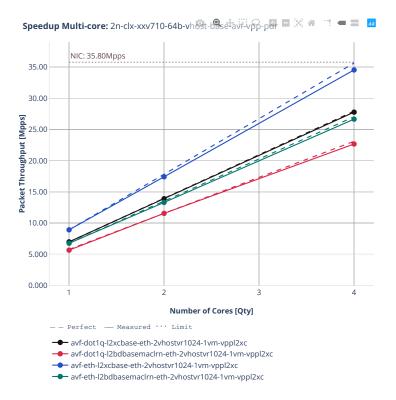

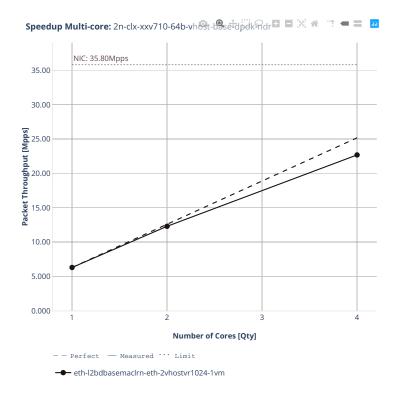

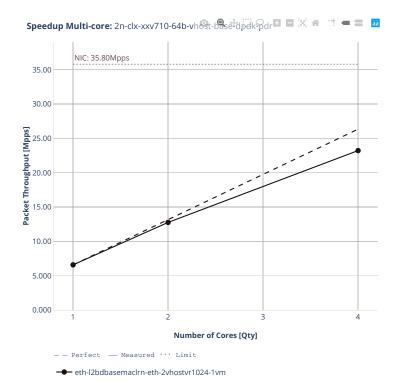

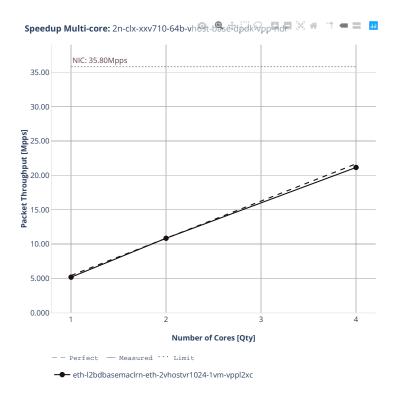

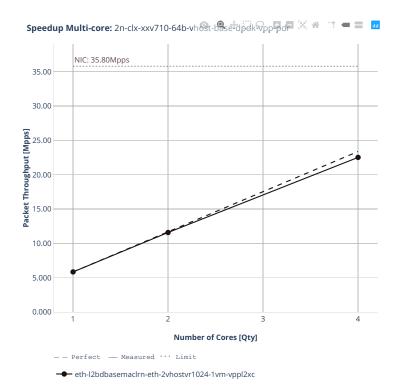

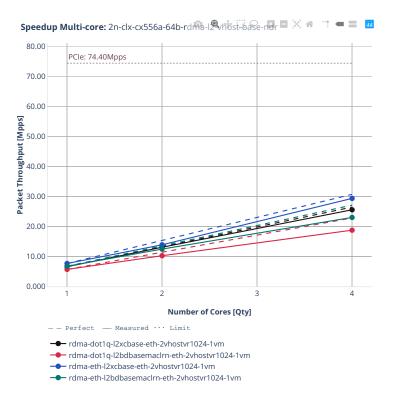

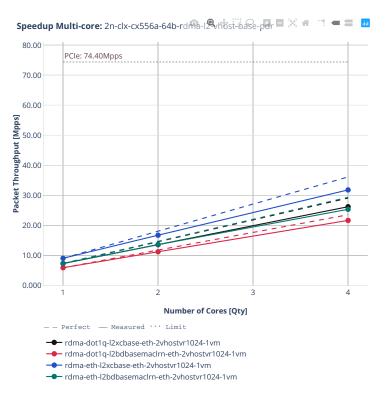

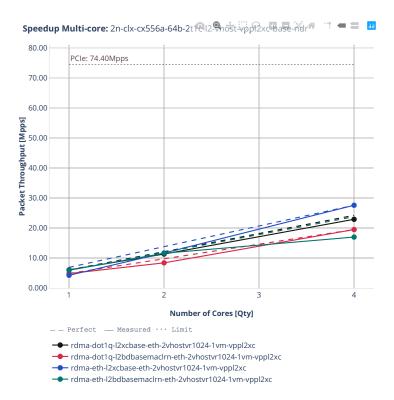

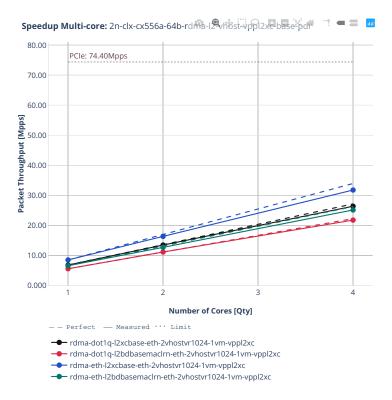

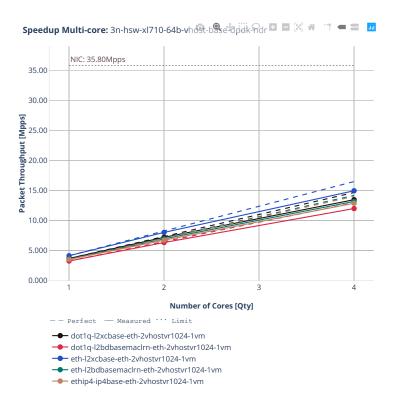

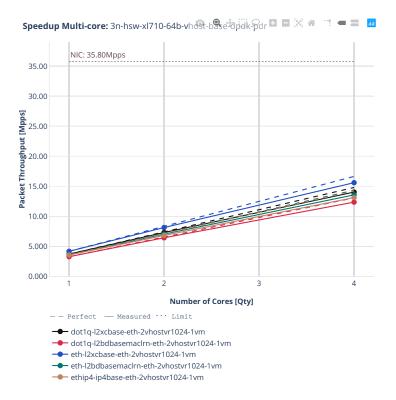

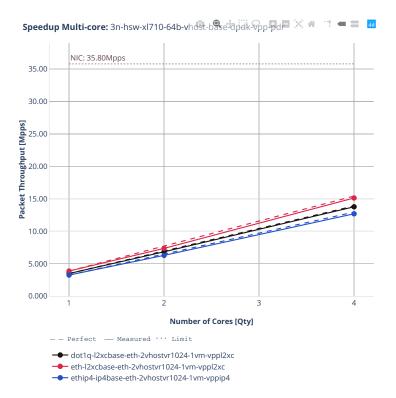

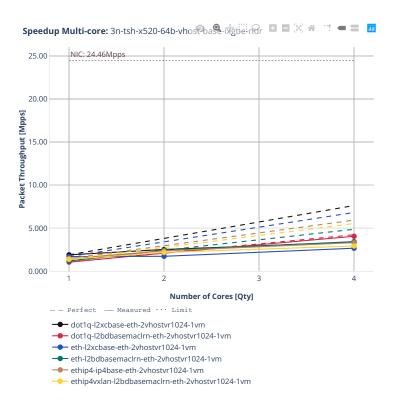

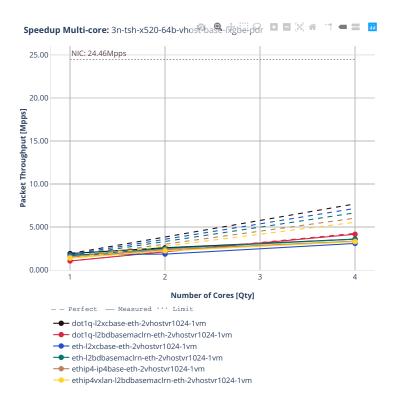

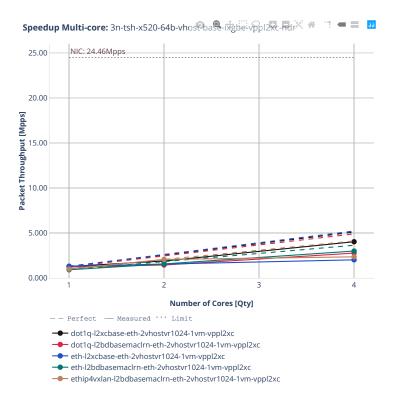

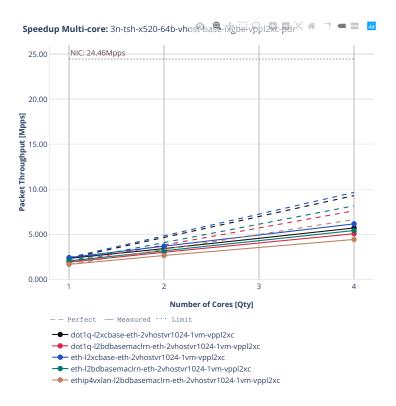

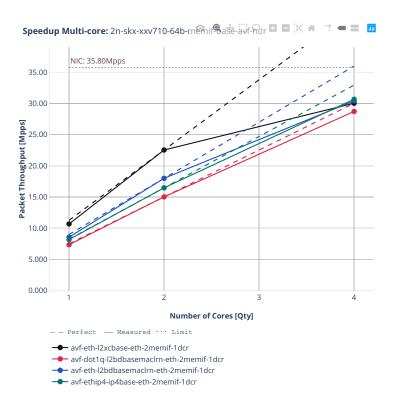

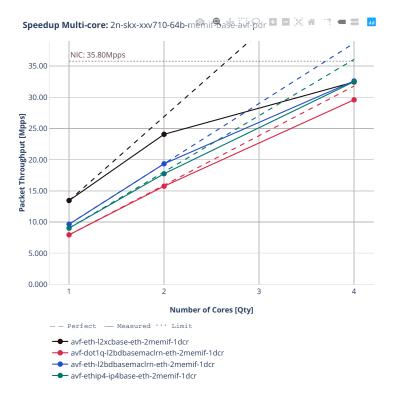

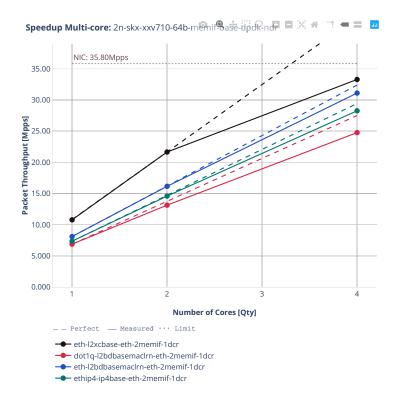

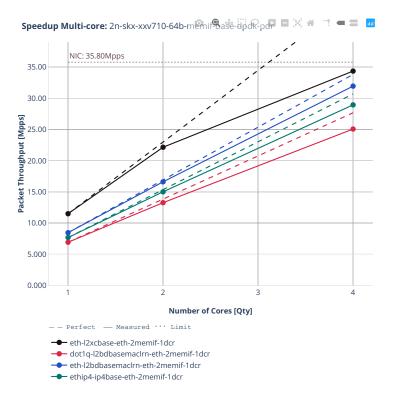

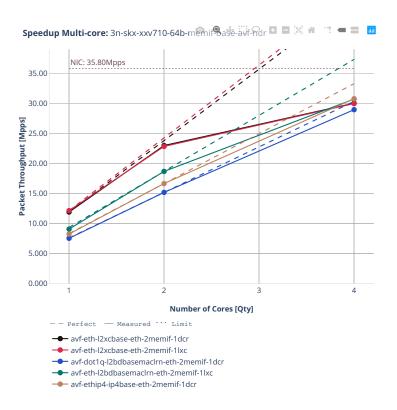

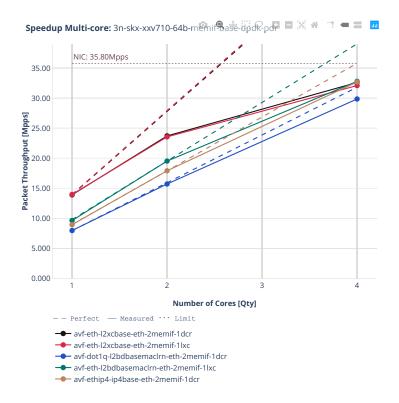

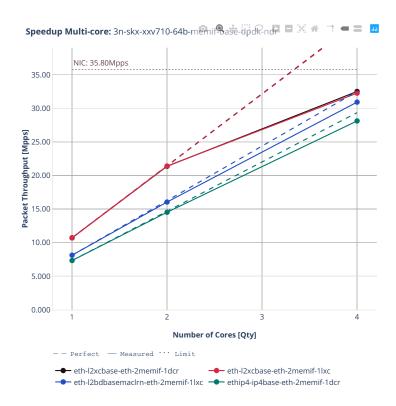

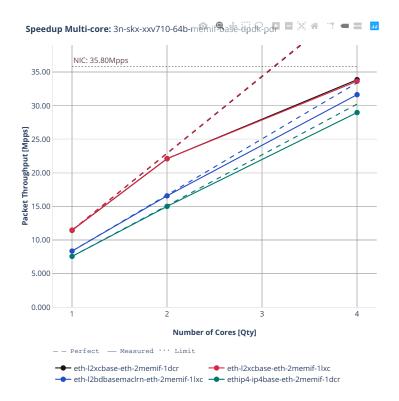

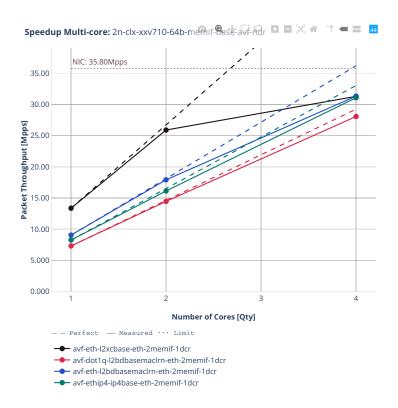

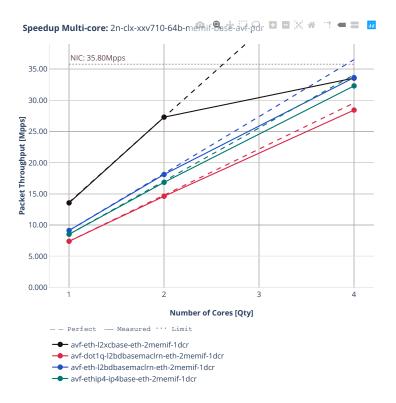

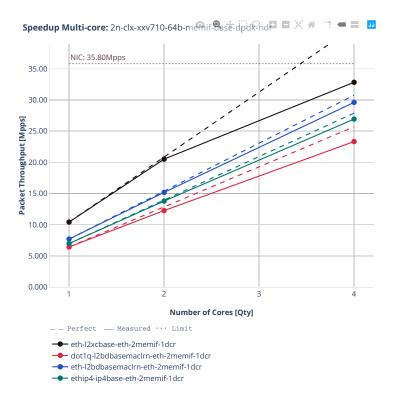

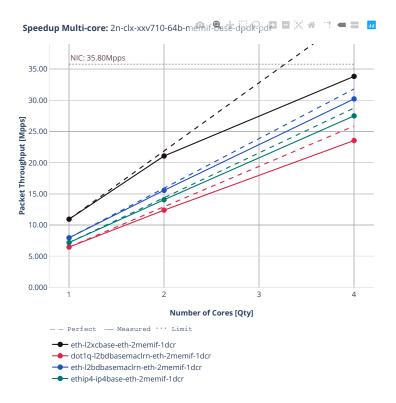

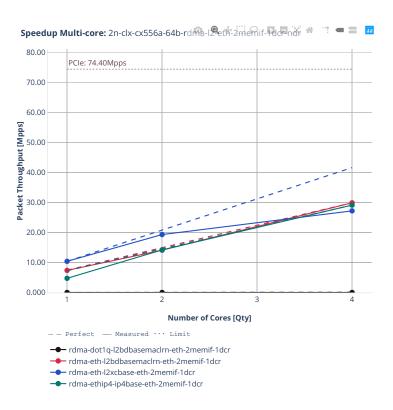

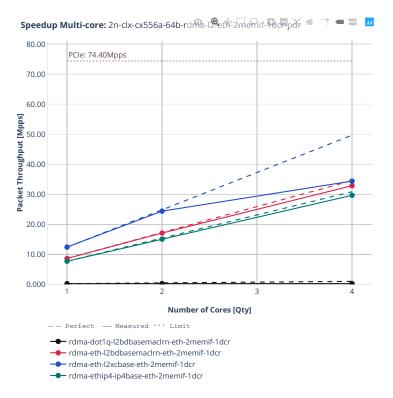

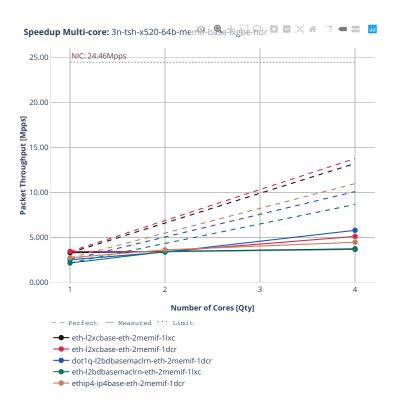

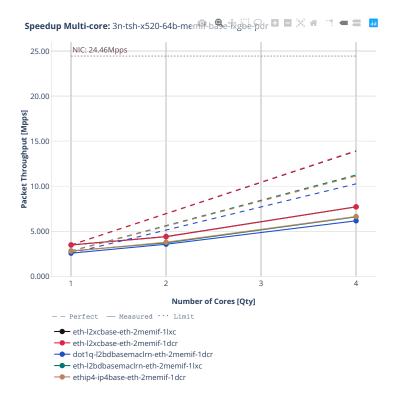

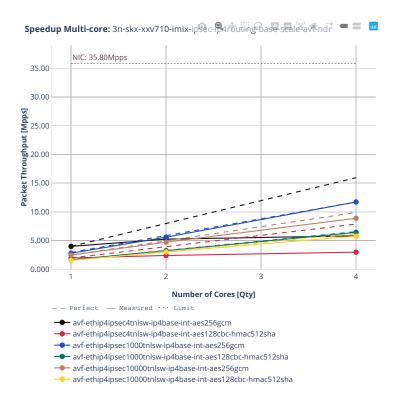

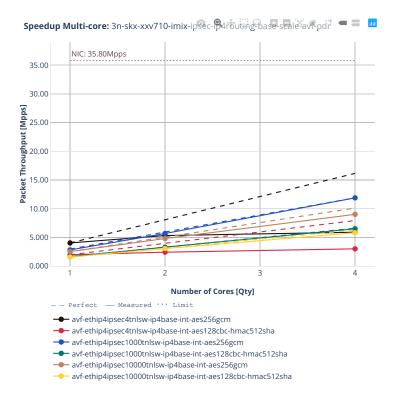

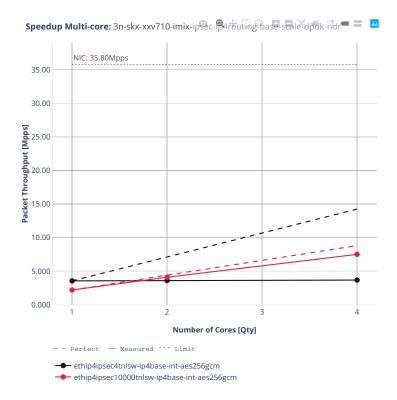

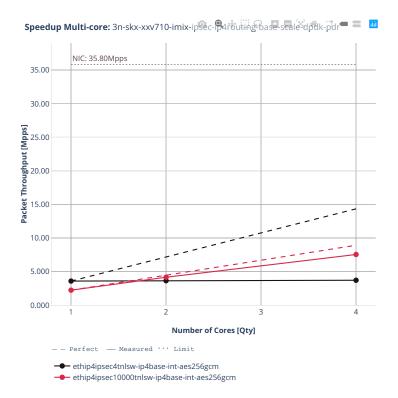

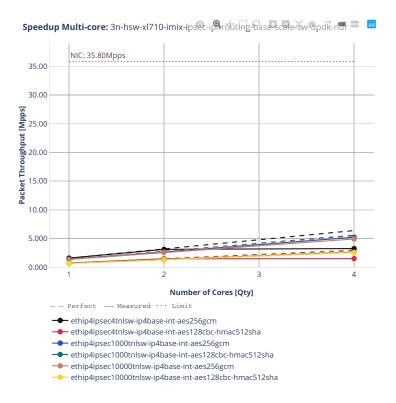

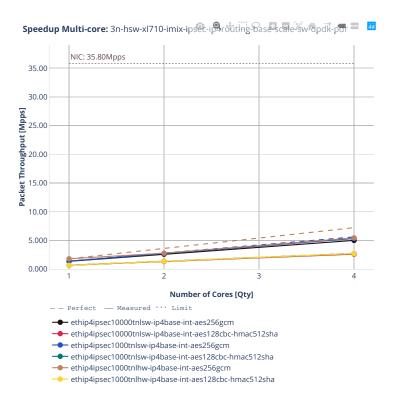

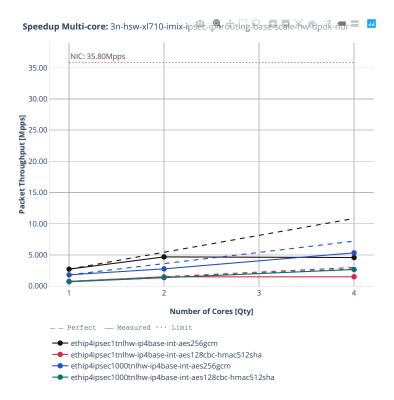

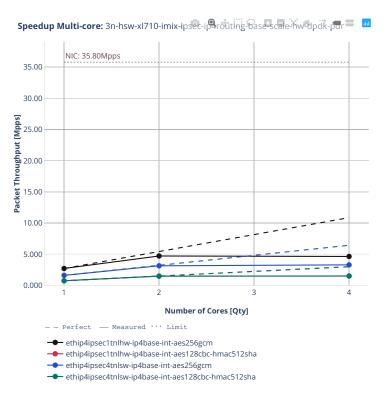

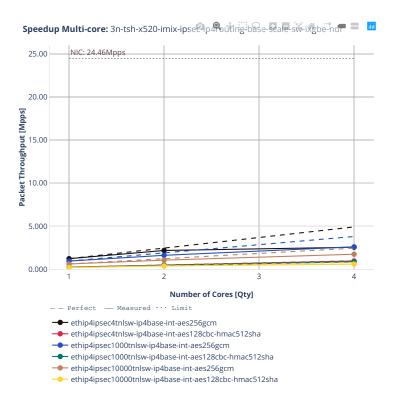

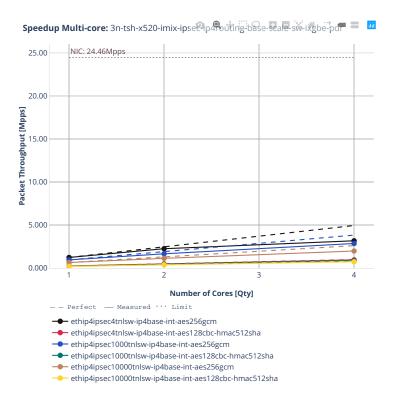

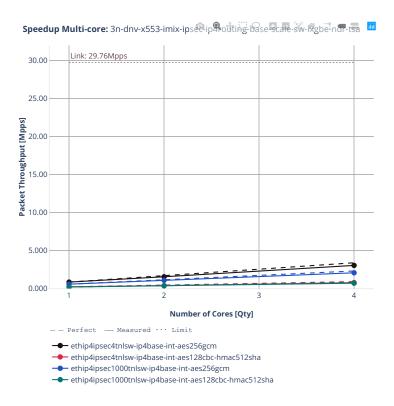

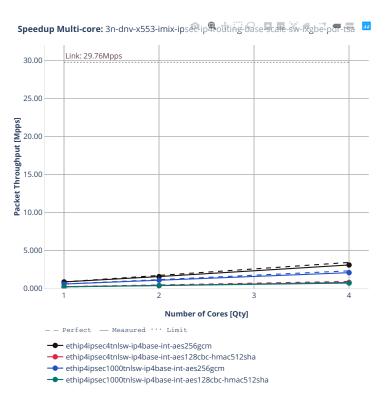

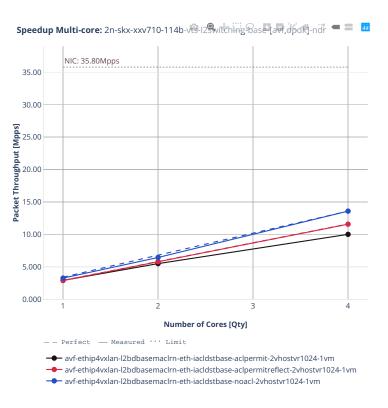

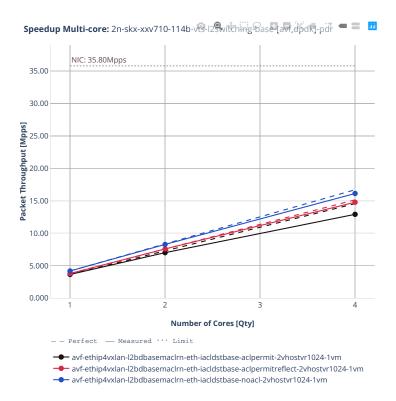

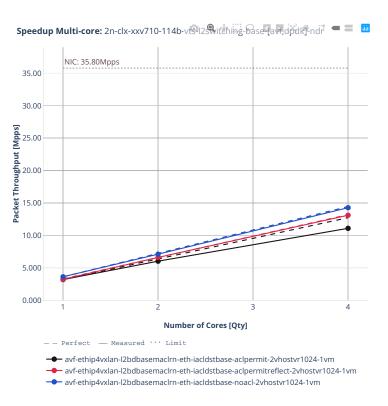

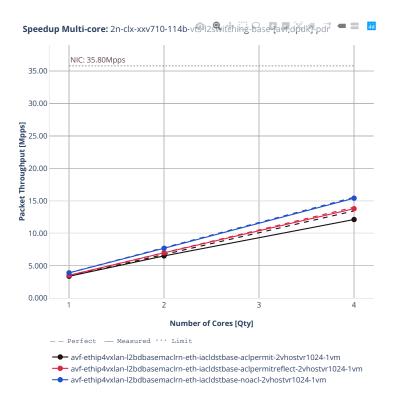

- **Speedup Multi-Core**: NDR, PDR throughput multi-core speedup graphs based on results from test job executions.

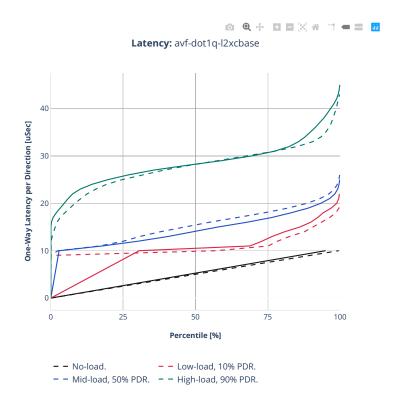

- Packet Latency: Latency graphs based on results from test job executions.

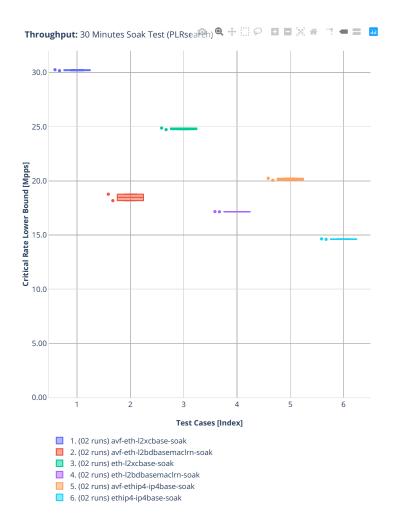

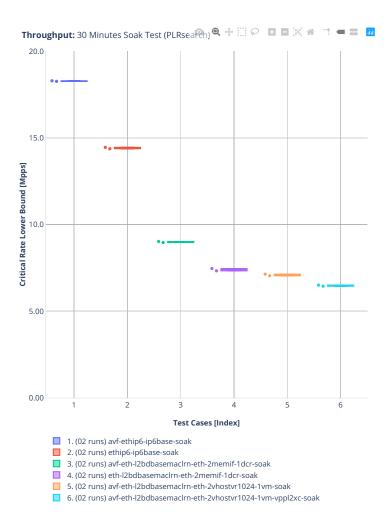

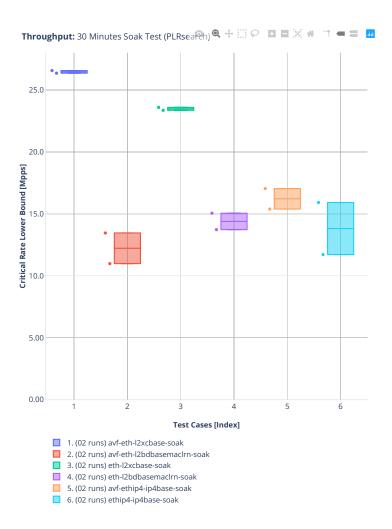

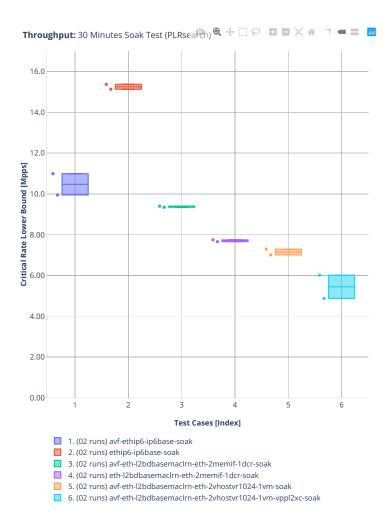

- Soak Tests: Long duration soak tests are executed using PLRsearch algorithm.

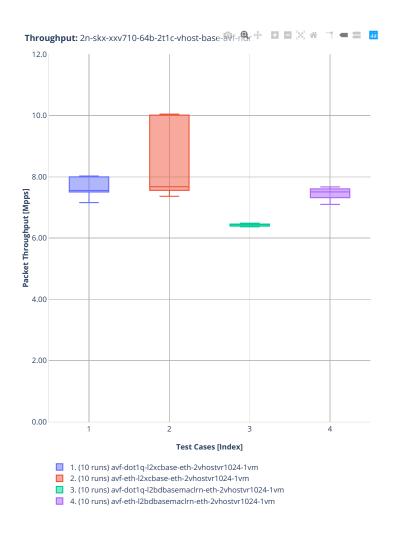

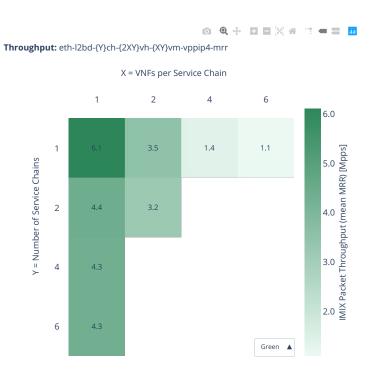

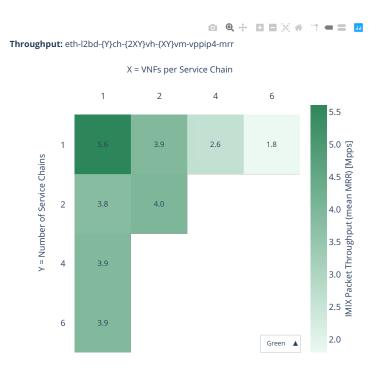

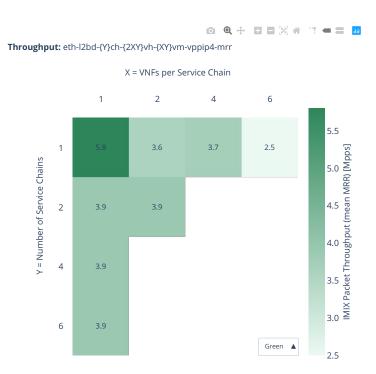

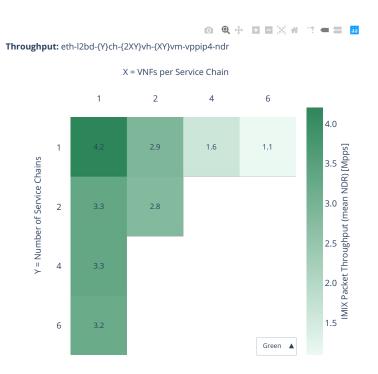

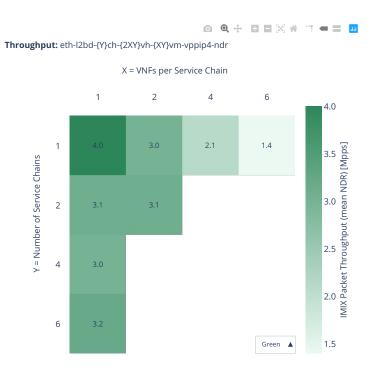

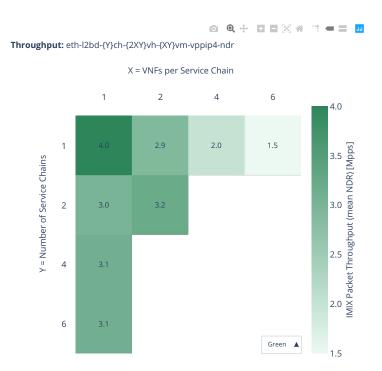

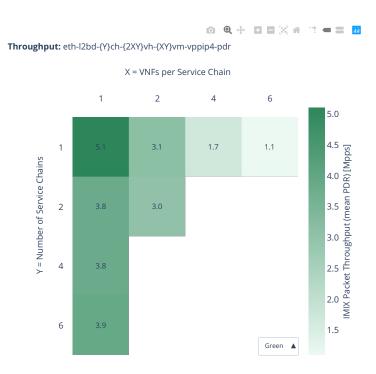

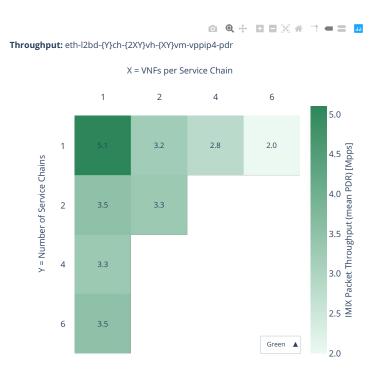

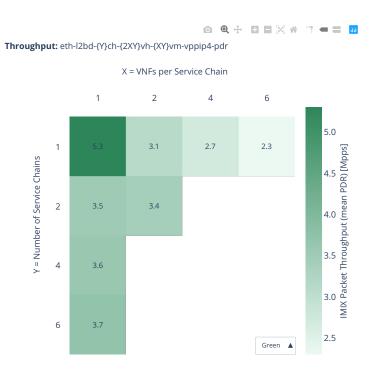

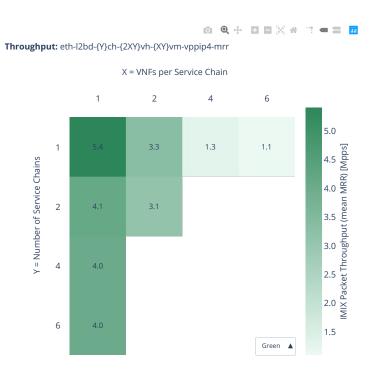

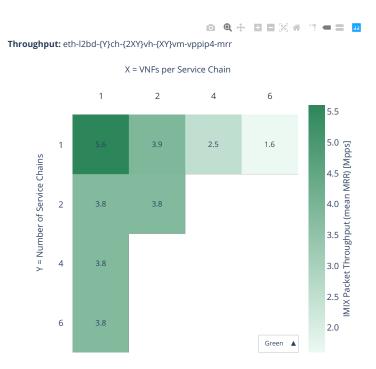

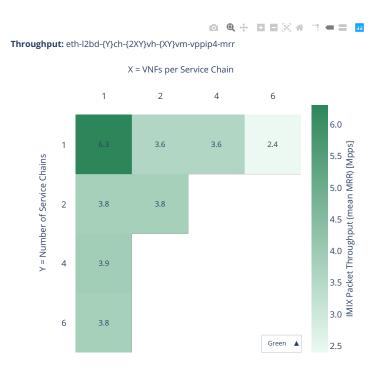

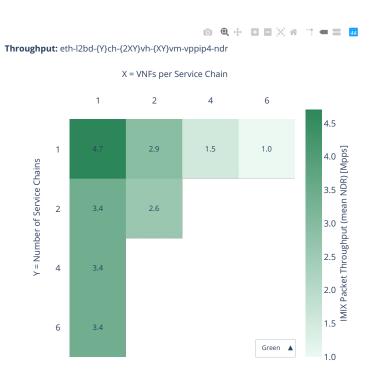

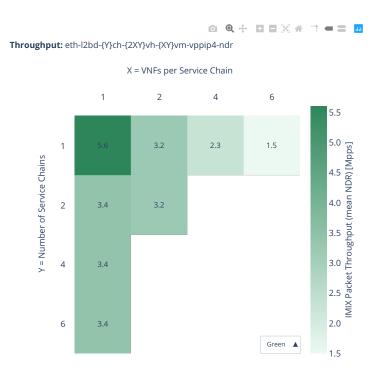

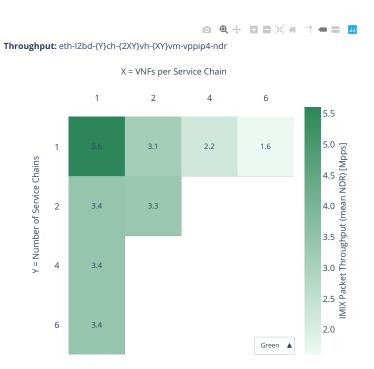

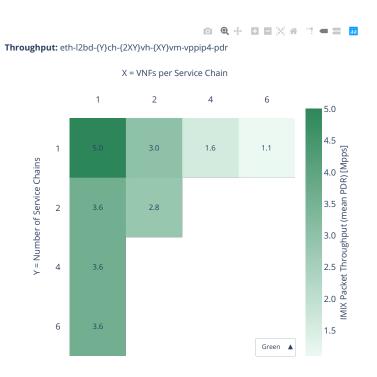

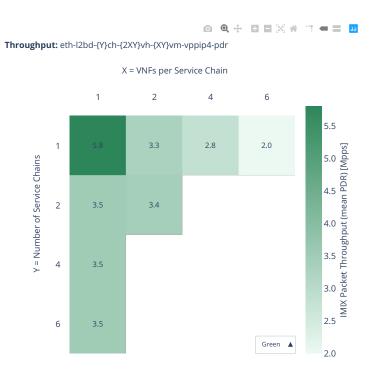

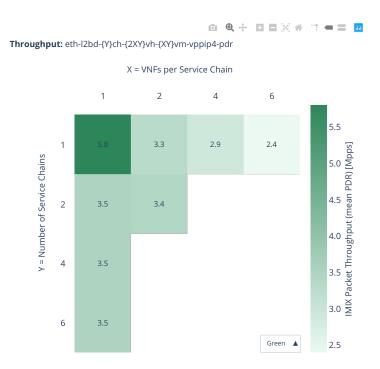

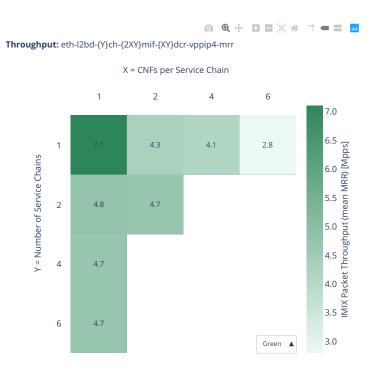

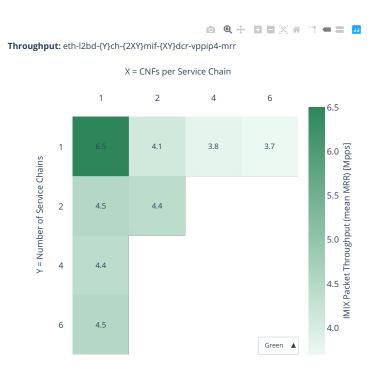

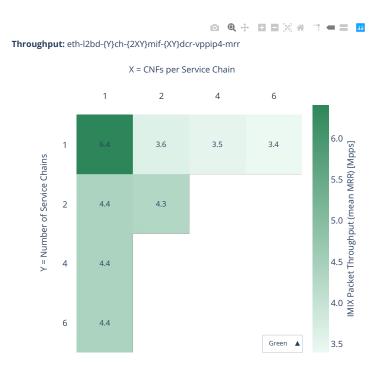

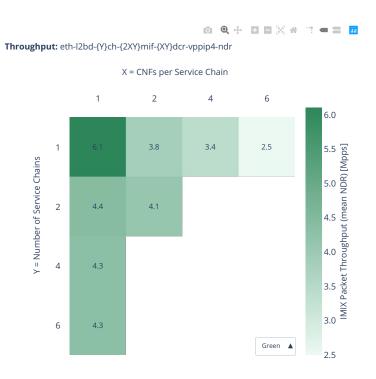

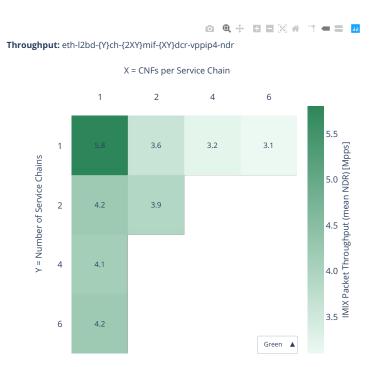

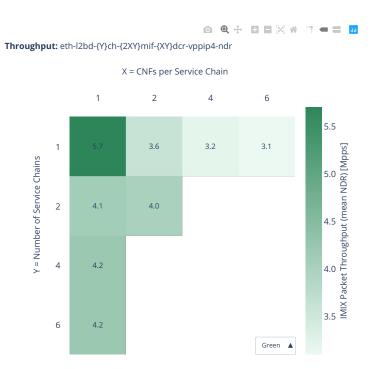

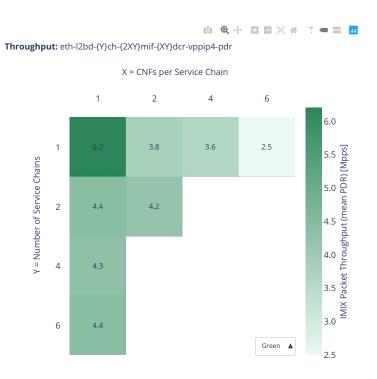

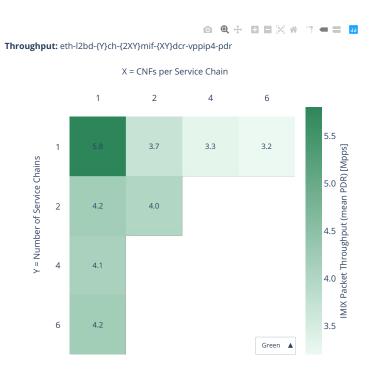

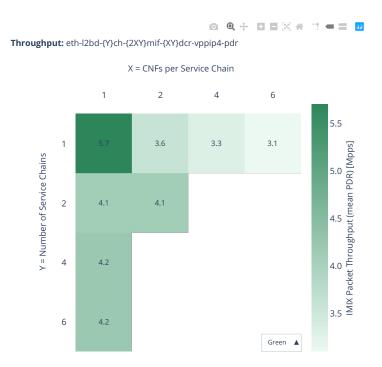

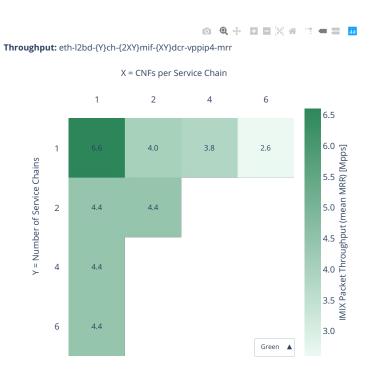

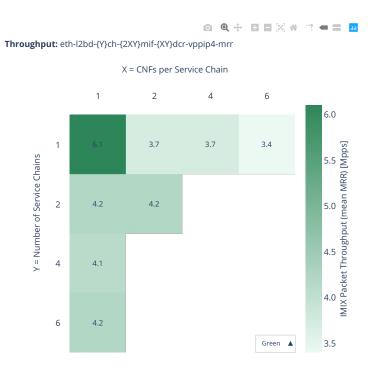

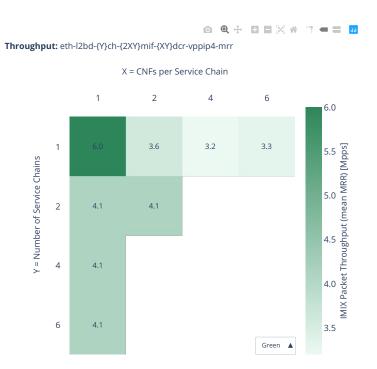

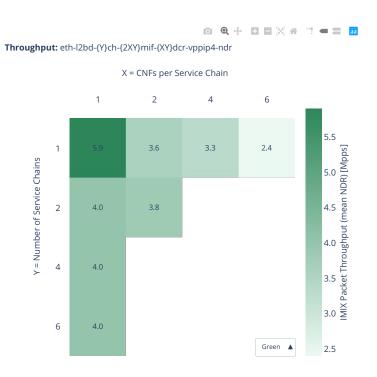

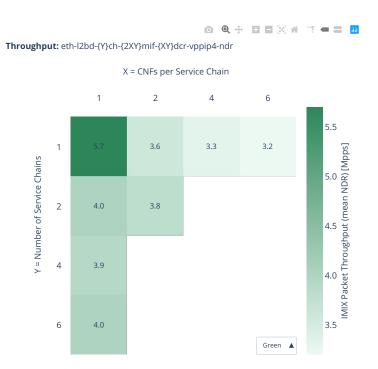

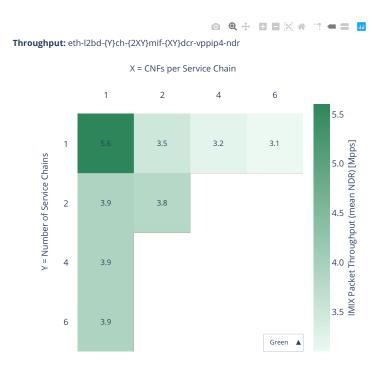

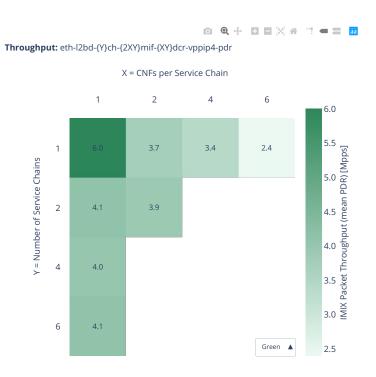

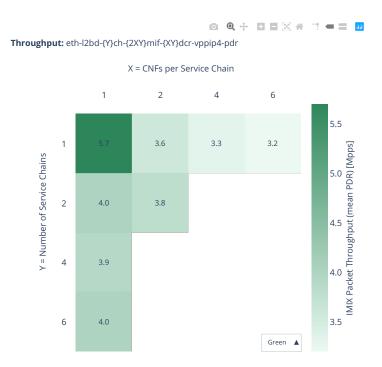

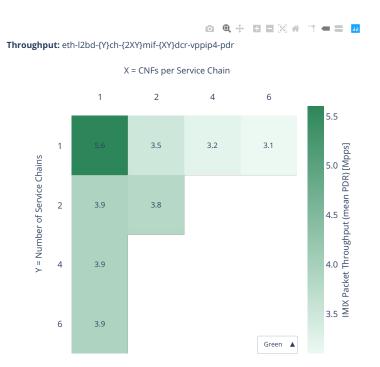

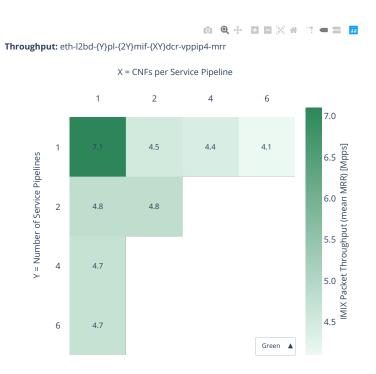

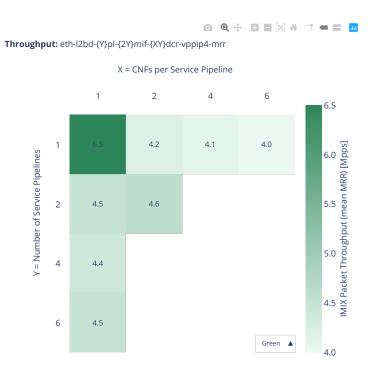

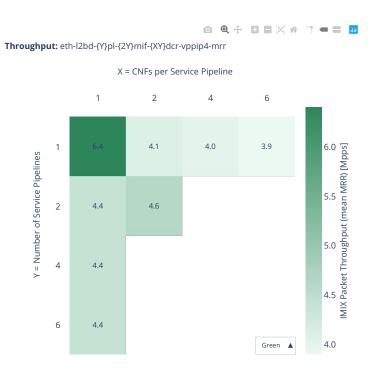

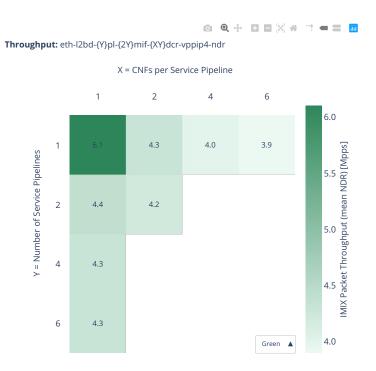

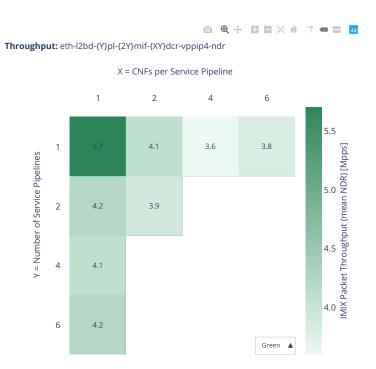

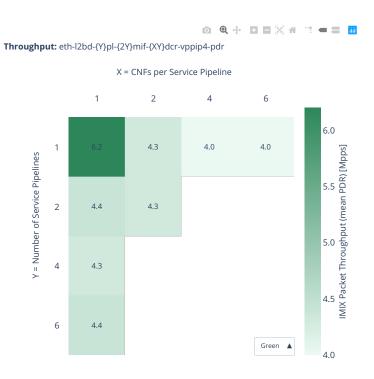

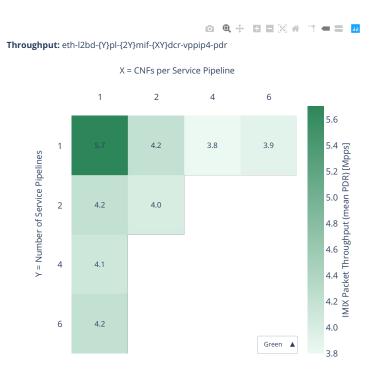

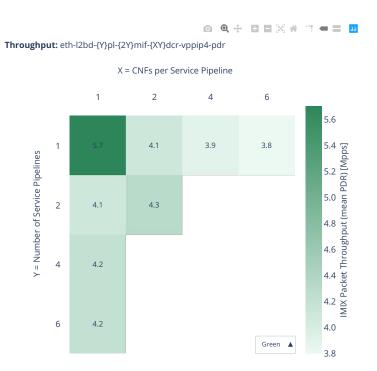

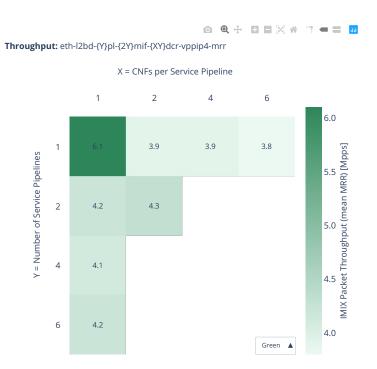

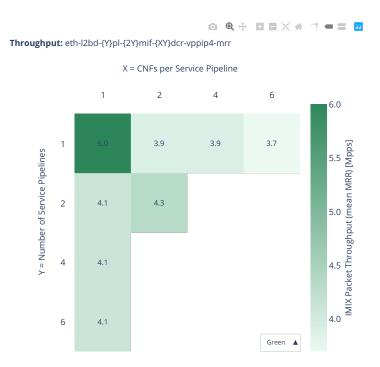

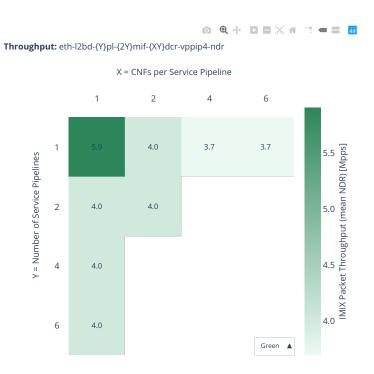

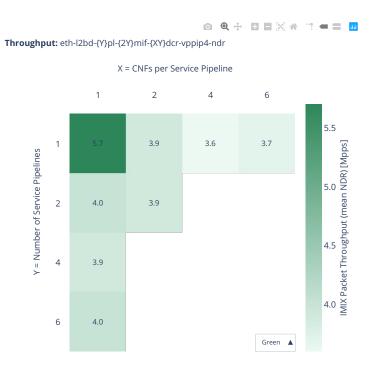

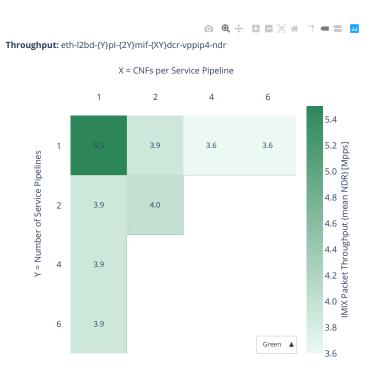

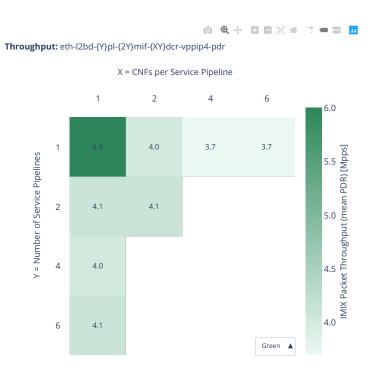

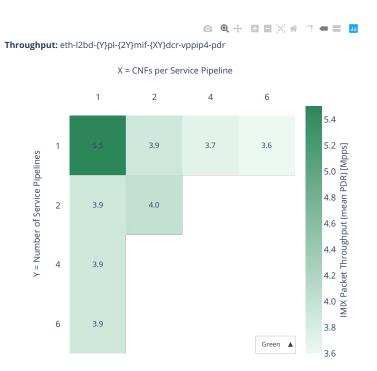

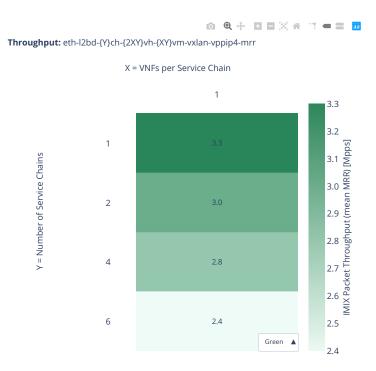

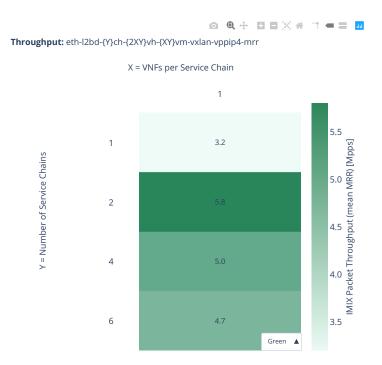

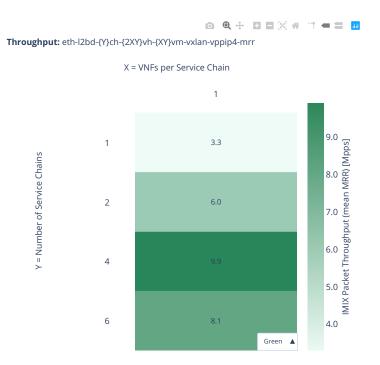

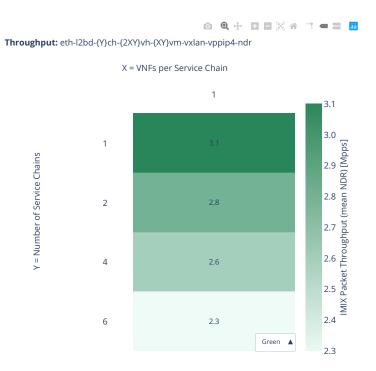

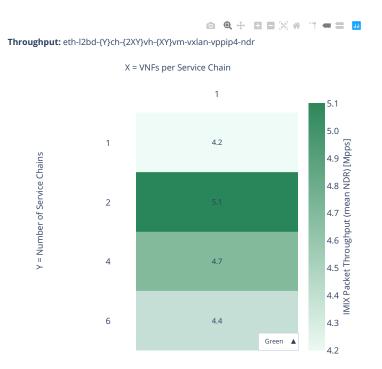

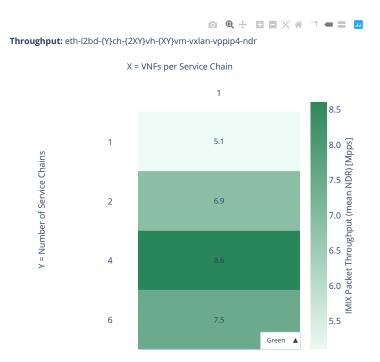

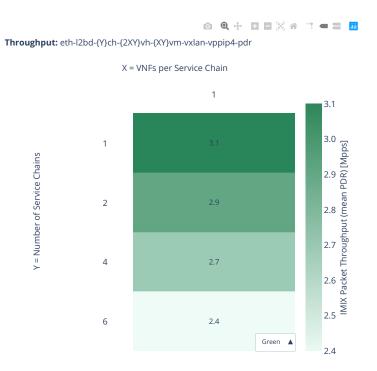

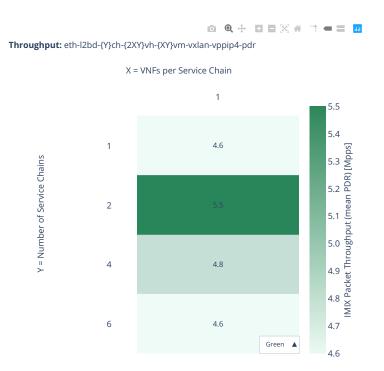

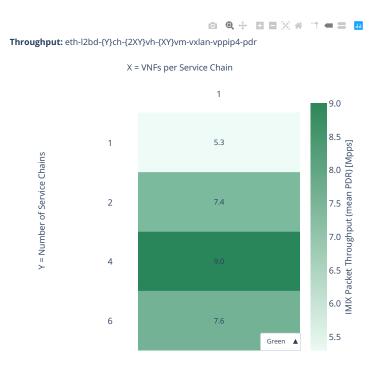

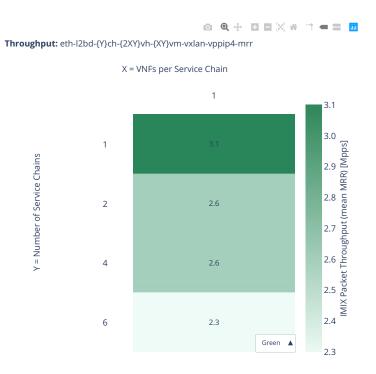

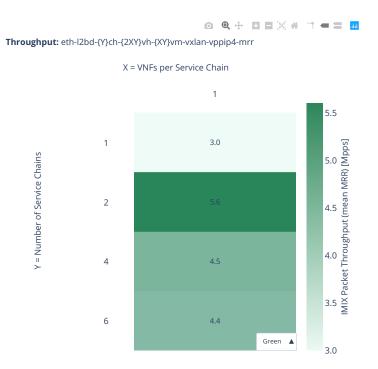

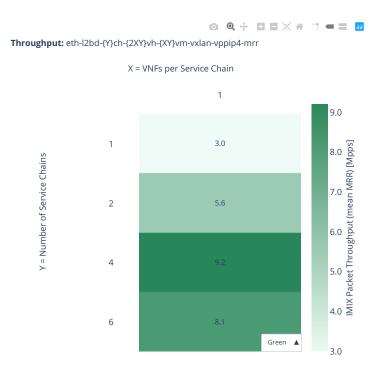

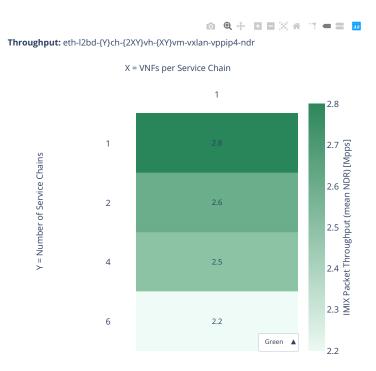

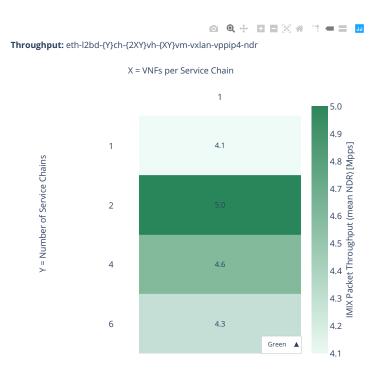

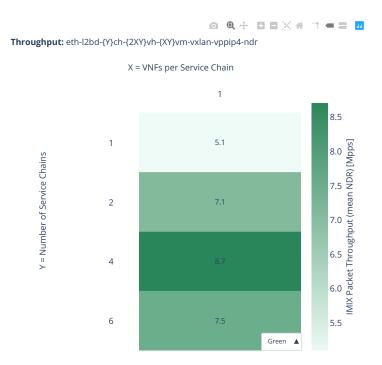

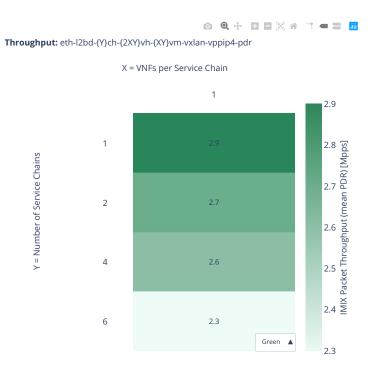

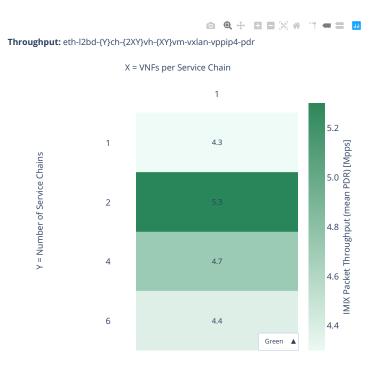

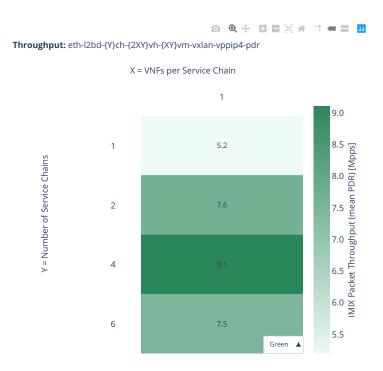

- NFV Service Density: Network Function Virtualization (NFV) service density tests focus on measuring total per server throughput at varied NFV service "packing" densities with vswitch providing host dataplane.

- **Comparisons**: Performance comparisons between VPP releases and between different testbed types.

- Throughput Trending: References to continuous VPP performance trending.

- Test Environment: Performance test environment configuration.

- **Documentation**: Pointers to CSIT source code documentation for VPP performance tests.

- 3. DPDK PERFORMANCE: DPDK performance tests executed in physical FD.io testbeds.

- Overview: Tested logical topologies, test coverage.

- Release Notes: Changes in CSIT-2009, known issues.

- Packet Throughput: NDR, PDR throughput graphs based on results from repeated same test job executions to verify repeatibility of measurements.

- Packet Latency: Latency graphs based on results from test job executions.

- **Comparisons**: Performance comparisons between DPDK releases and between different testbed types.

- Throughput Trending: References to regular DPDK performance trending.

- **Test Environment**: Performance test environment configuration.

- Documentation: Pointers to CSIT source code documentation for DPDK performance tests.

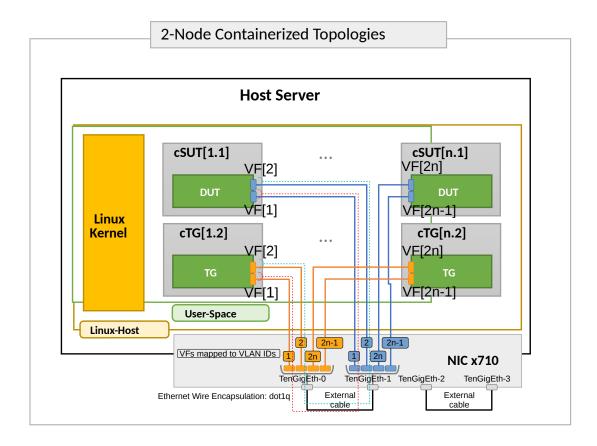

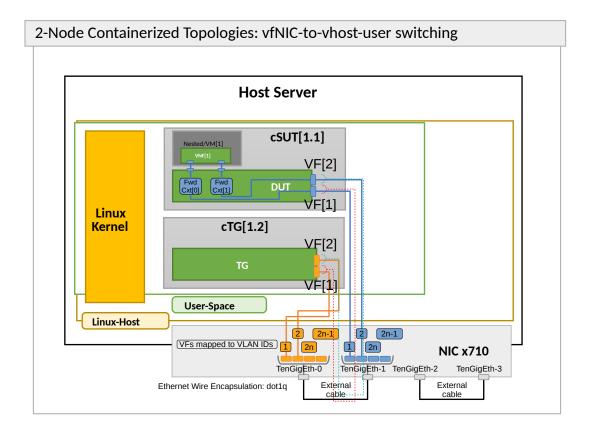

- 4. VPP DEVICE: VPP functional tests executed in physical FD.io testbeds using containers.

- Overview: Tested virtual topologies, test coverage and naming specifics;

- Release Notes: Changes in CSIT-2009, added tests, environment or methodology changes, known issues.

- Integration Tests: Functional test environment configuration.

- Documentation: Pointers to CSIT source code documentation for VPP functional tests.

- 5. DETAILED RESULTS: Detailed result tables auto-generated from CSIT test job executions using RF (Robot Framework) output files as sources.

- **VPP Performance NDR/PDR**: VPP NDR/PDR throughput and latency.

- VPP Performance MRR: VPP MRR throughput.

- DPDK Performance: DPDK Testpmd and L3fwd NDR/PDR throughput and latency.

- 6. TEST CONFIGURATION: VPP DUT configuration data based on VPP API Test (VAT) Commands History auto-generated from CSIT test job executions using RF output files as sources.

- VPP Performance NDR/PDR: Configuration data.

- VPP Performance MRR: Configuration data.

- 7. TEST OPERATIONAL DATA: VPP DUT operational data auto-generated from CSIT test job executions using RFoutput files as sources.

- VPP Performance NDR/PDR: VPP show run outputs under test load.

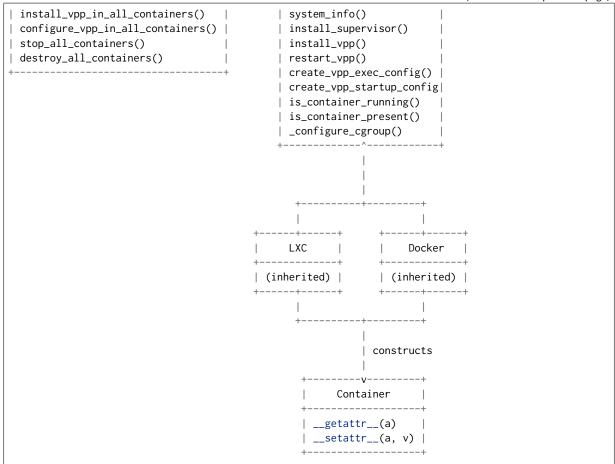

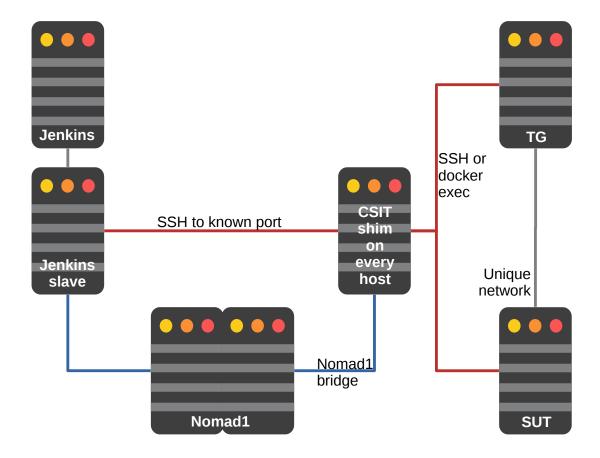

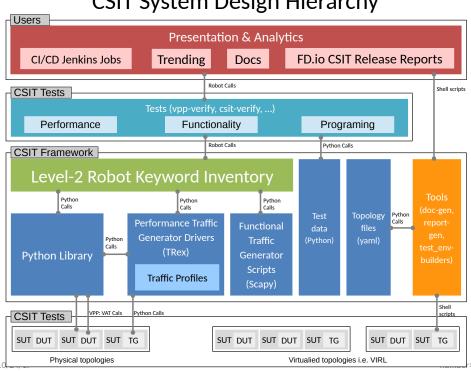

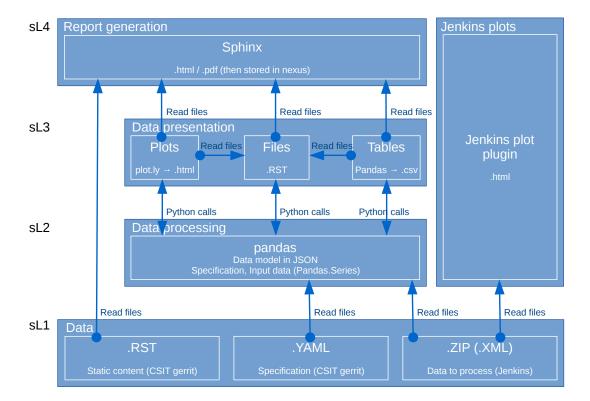

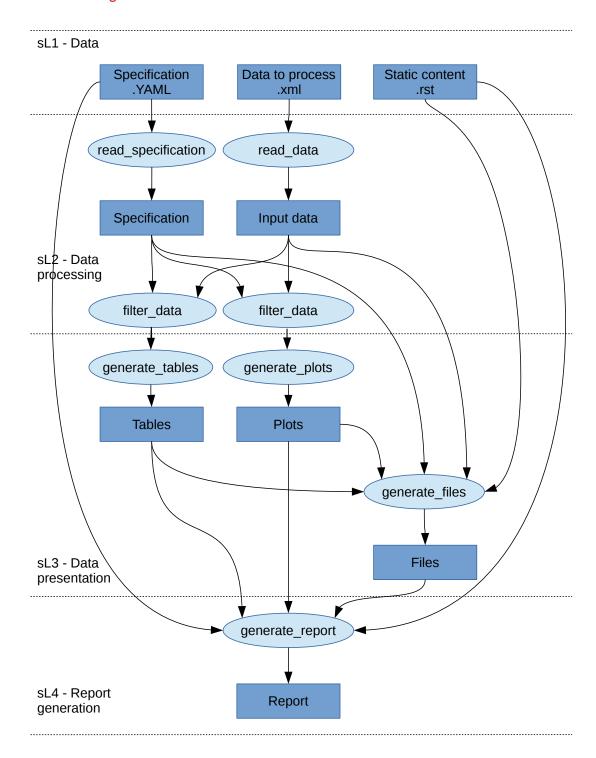

- 8. CSIT FRAMEWORK DOCUMENTATION: Description of the overall FD.io CSIT framework.

- Design: Framework modular design hierarchy.

- Test naming: Test naming convention.

- Presentation and Analytics Layer: Description of PAL CSIT analytics module.

- CSIT RF Tags Descriptions: CSIT RF Tags used for test suite and test case grouping and selection.

# 1.3 Test Scenarios

FD.io CSIT-2009 report includes multiple test scenarios of VPP centric applications, topologies and use cases. In addition it also covers baseline tests of DPDK sample applications. Tests are executed in physical (performance tests) and virtual environments (functional tests).

Brief overview of test scenarios covered in this report:

- 1. **VPP Performance**: VPP performance tests are executed in physical FD.io testbeds, focusing on VPP network data plane performance in NIC-to-NIC switching topologies. Tested across Intel Xeon Haswell and Skylake servers, ARM, Denverton, range of NICs (10GE, 25GE, 40GE) and multi-thread/multi-core configurations. VPP application runs in bare-metal host user-mode handling NICs. TRex is used as a traffic generator.

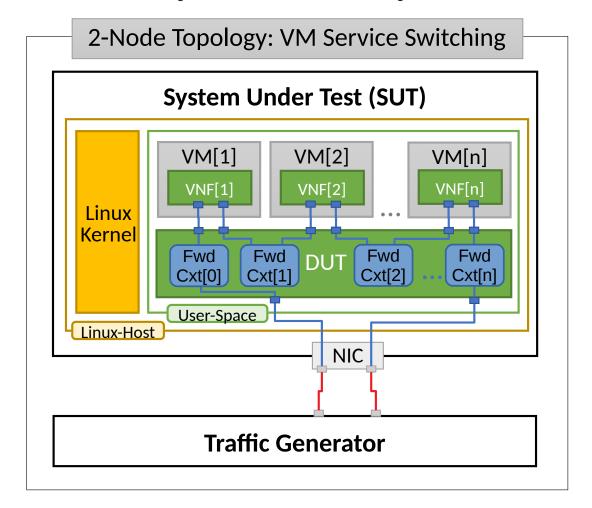

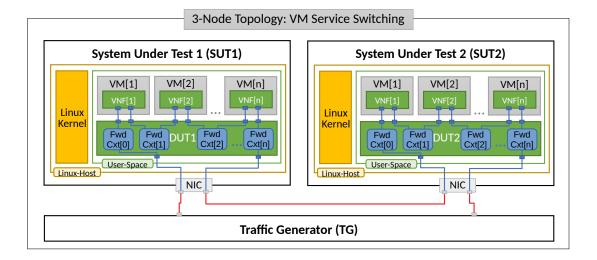

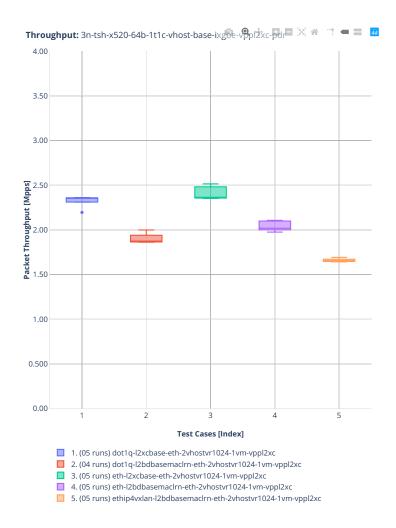

- 2. **VPP Vhostuser Performance with KVM VMs**: VPP VM service switching performance tests using vhostuser virtual interface for interconnecting multiple NF-in-VM instances. VPP vswitch instance runs in bare-metal user-mode handling NICs and connecting over vhost-user interfaces to VM instances each running VPP with virtio virtual interfaces. Similarly to VPP Performance, tests are run across a range of configurations. TRex is used as a traffic generator.

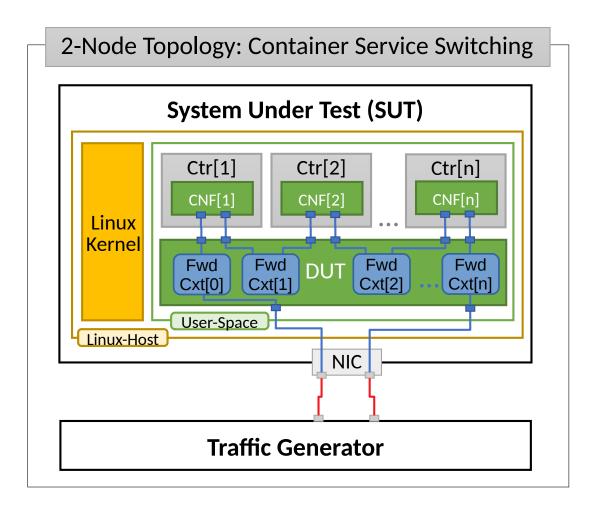

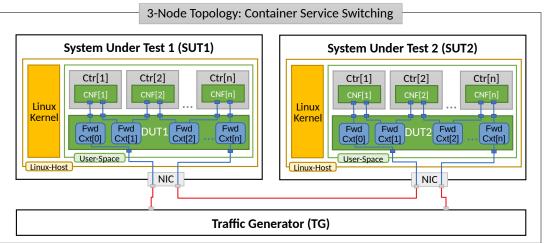

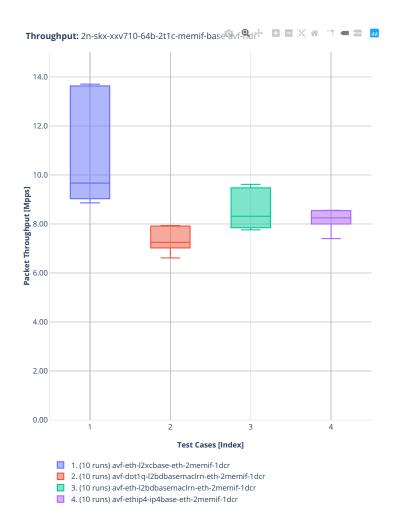

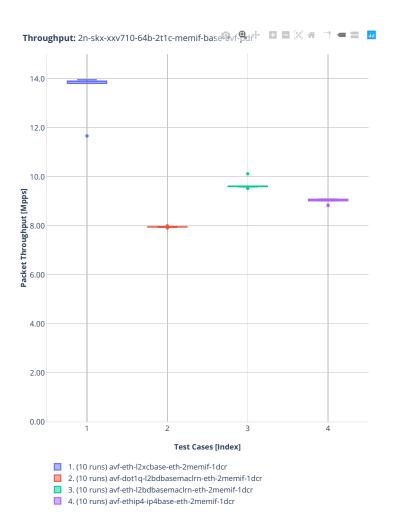

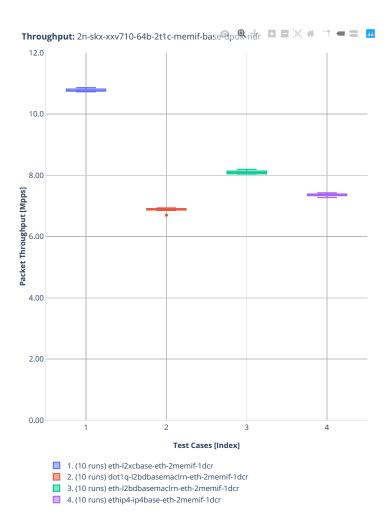

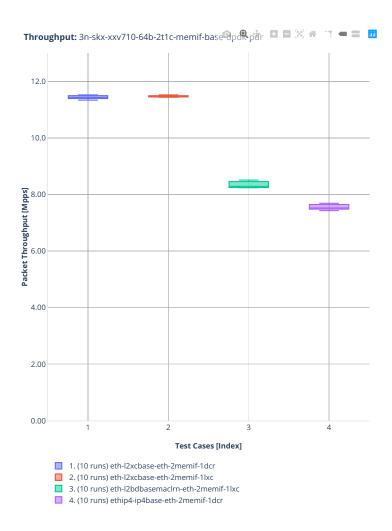

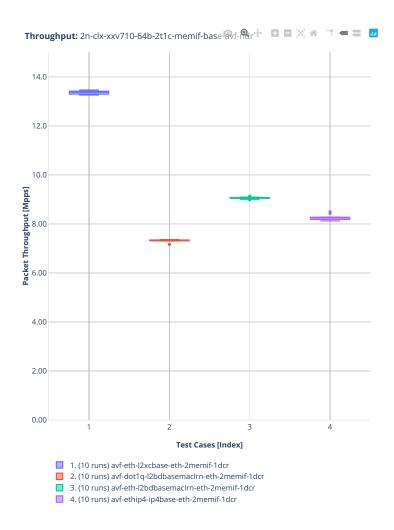

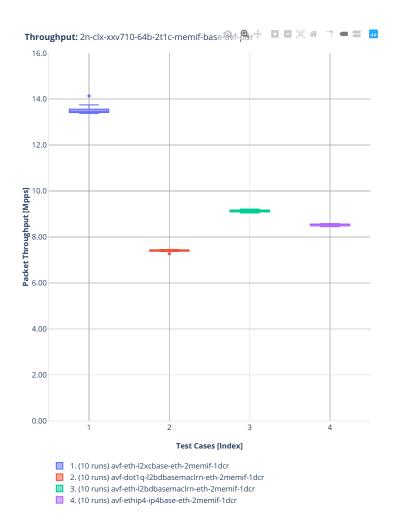

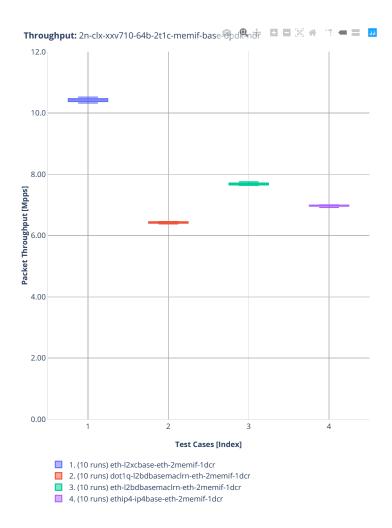

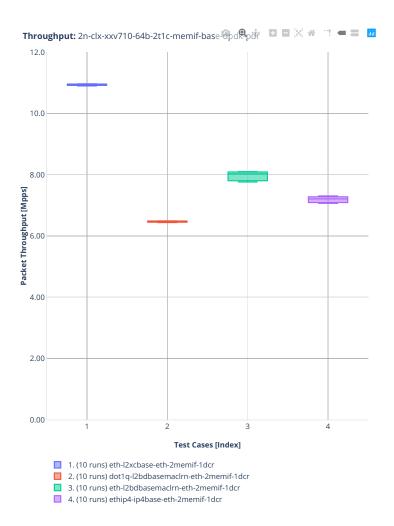

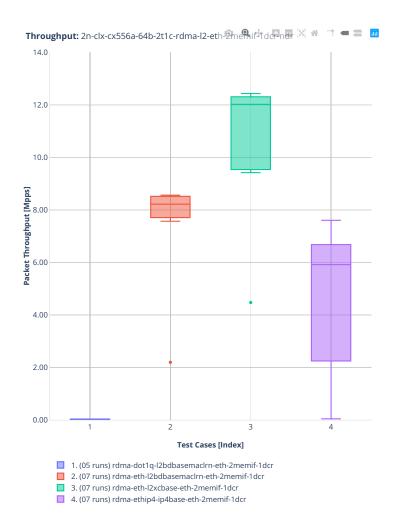

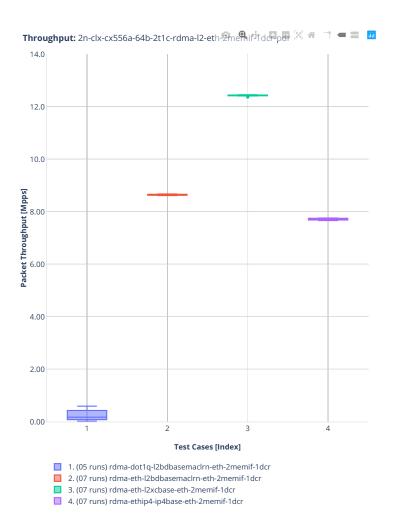

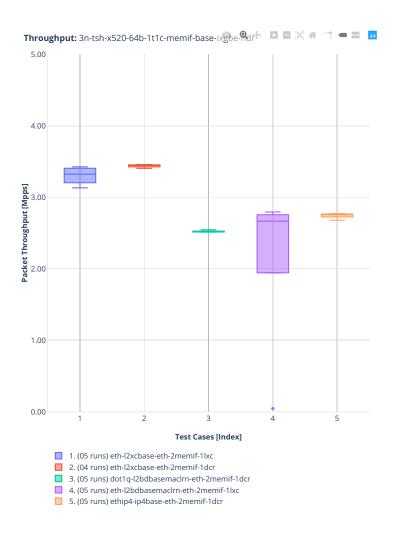

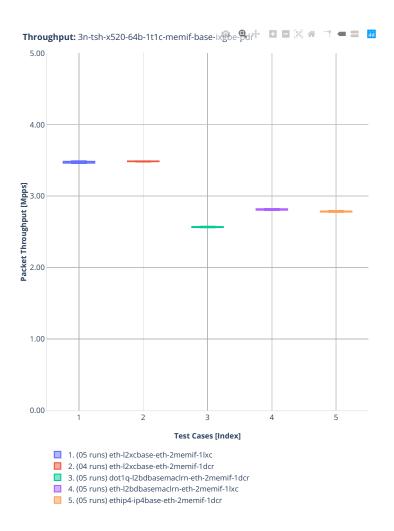

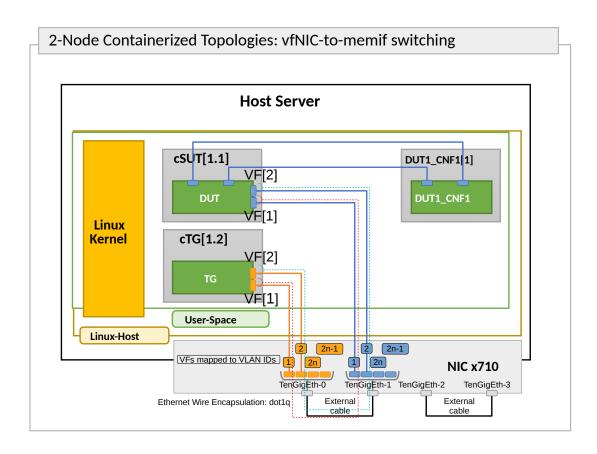

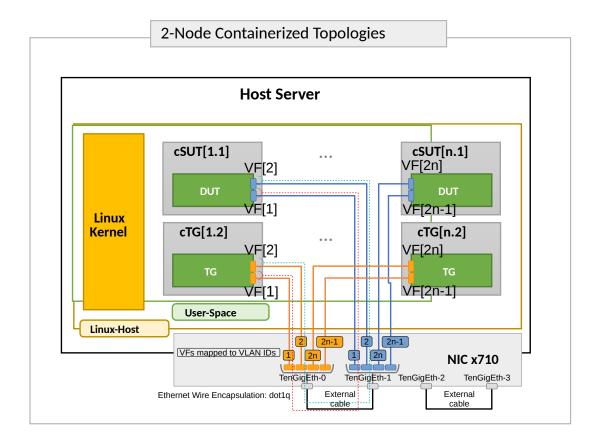

- 3. VPP Memif Performance with LXC and Docker Containers: VPP Container service switching performance tests using memif virtual interface for interconnecting multiple VPP-in-container instances. VPP vswitch instance runs in bare-metal user-mode handling NICs and connecting over memif (Slave side) interfaces to more instances of VPP running in LXC or in Docker Containers, both with memif interfaces (Master side). Similarly to VPP Performance, tests are run across a range of configurations. TRex is used as a traffic generator.

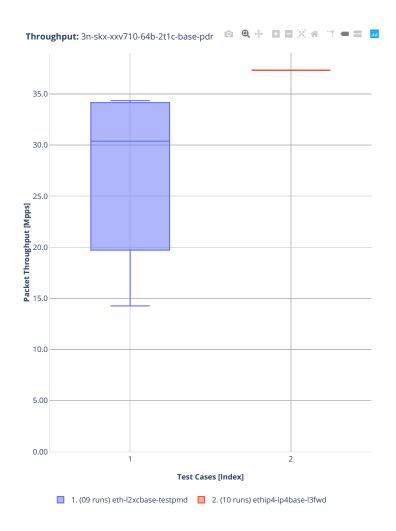

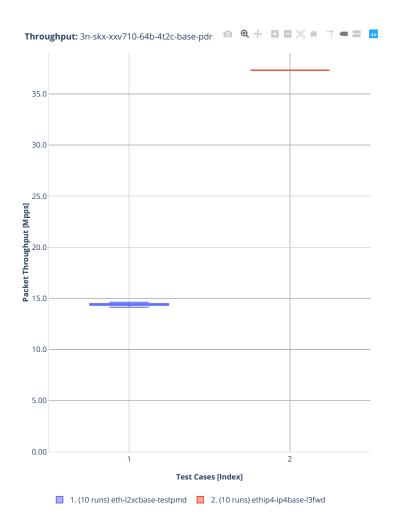

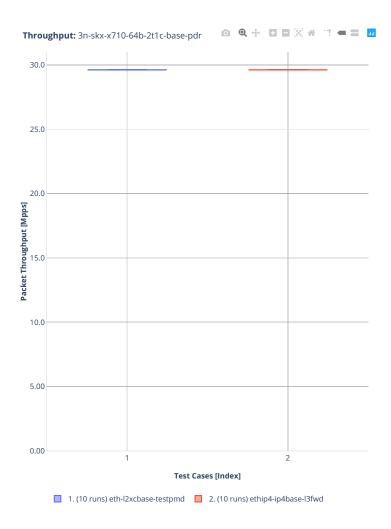

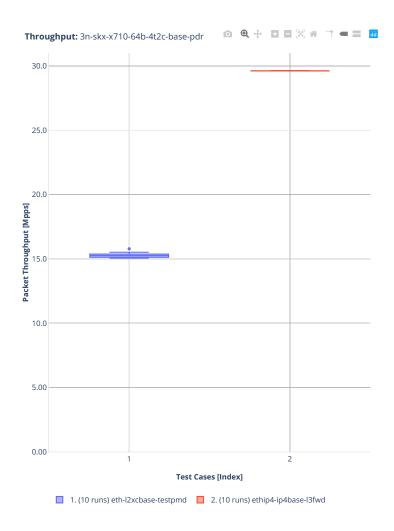

- 4. **DPDK Performance**: VPP uses DPDK to drive the NICs and physical interfaces. DPDK performance tests are used as a baseline to profile performance of the DPDK sub-system. Two DPDK applications are tested: Testpmd and L3fwd. DPDK tests are executed in the same testing environment as VPP tests. DPDK Testpmd and L3fwd applications run in host user-mode. TRex is used as a traffic generator.

- 5. **VPP Functional**: VPP functional tests are executed in virtual FD.io testbeds, focusing on VPP packet processing functionality, including both network data plane and in-line control plane. Tests cover vNIC-to-vNIC vNIC-to-nestedVM-to-vNIC forwarding topologies. Scapy is used as a traffic generator.

All CSIT test data included in this report is auto- generated from RF (Robot Framework) output.xml files produced by LF (Linux Foundation) FD.io Jenkins jobs executed against VPP-20.09 release artifacts. References are provided to the original FD.io Jenkins job results and all archived source files.

FD.io CSIT system is developed using two main coding platforms: RF and Python2.7. CSIT-2009 source code for the executed test suites is available in CSIT branch rls2009 in the directory ./tests/<name\_of\_the\_test\_suite>. A local copy of CSIT source code can be obtained by cloning CSIT git repository - git clone https://gerrit.fd.io/r/csit.

1.3. Test Scenarios 3

# 1.4 Physical Testbeds

All FD.io (Fast Data Input/Ouput) CSIT (Continuous System Integration and Testing) performance test results included in this report are executed on the physical testbeds hosted by LF FD.io project, unless otherwise noted.

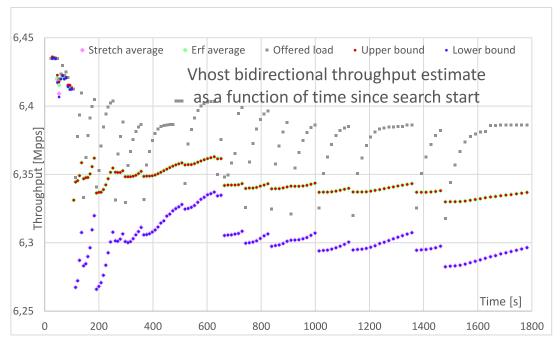

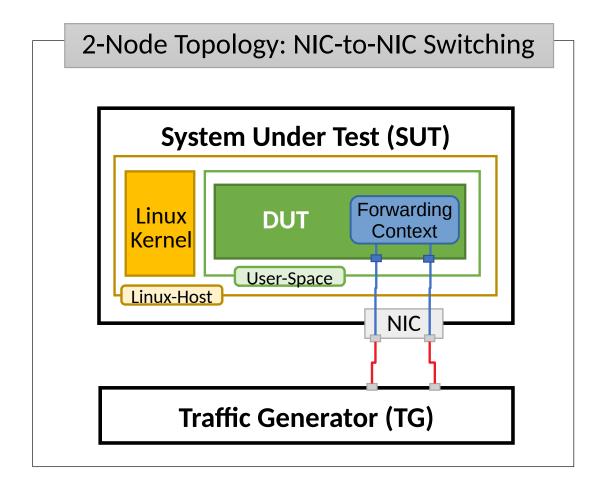

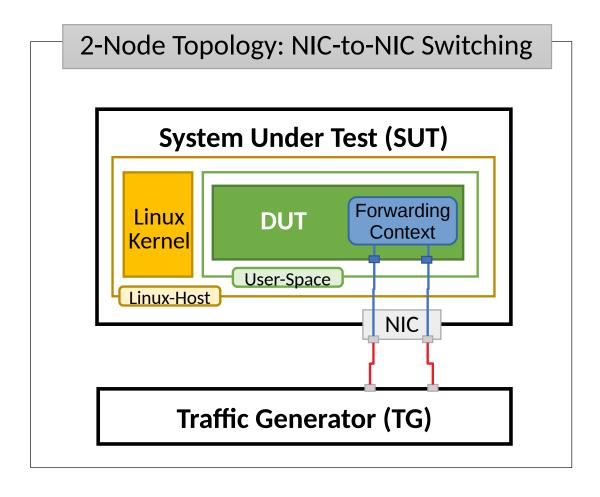

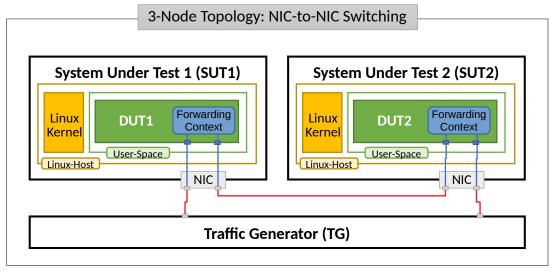

Two physical server topology types are used:

- 2-Node Topology: Consists of one server acting as a System Under Test (SUT) and one server acting as a Traffic Generator (TG), with both servers connected into a ring topology. Used for executing tests that require frame encapsulations supported by TG.

- 3-Node Topology: Consists of two servers acting as a Systems Under Test (SUTs) and one server acting as a Traffic Generator (TG), with all servers connected into a ring topology. Used for executing tests that require frame encapsulations not supported by TG e.g. certain overlay tunnel encapsulations and IPsec. Number of native Ethernet, IPv4 and IPv6 encapsulation tests are also executed on these testbeds, for comparison with 2-Node Topology.

Current FD.io production testbeds are built with SUT servers based on the following processor architectures:

- Intel Xeon: Skylake Platinum 8180, Haswell-SP E5-2699v3, Cascade Lake Platinum 8280, Cascade Lake 6252N.

- Intel Atom: Denverton C3858.

- ARM: TaiShan 2280, hip07-d05.

Server SUT performance depends on server and processor type, hence results for testbeds based on different servers must be reported separately, and compared if appropriate.

Complete technical specifications of compute servers used in CSIT physical testbeds are maintained in FD.io CSIT repository: <a href="https://git.fd.io/csit/tree/docs/lab/testbed\_specifications.md">https://git.fd.io/csit/tree/docs/lab/testbed\_specifications.md</a>.

Following is the description of existing production testbeds.

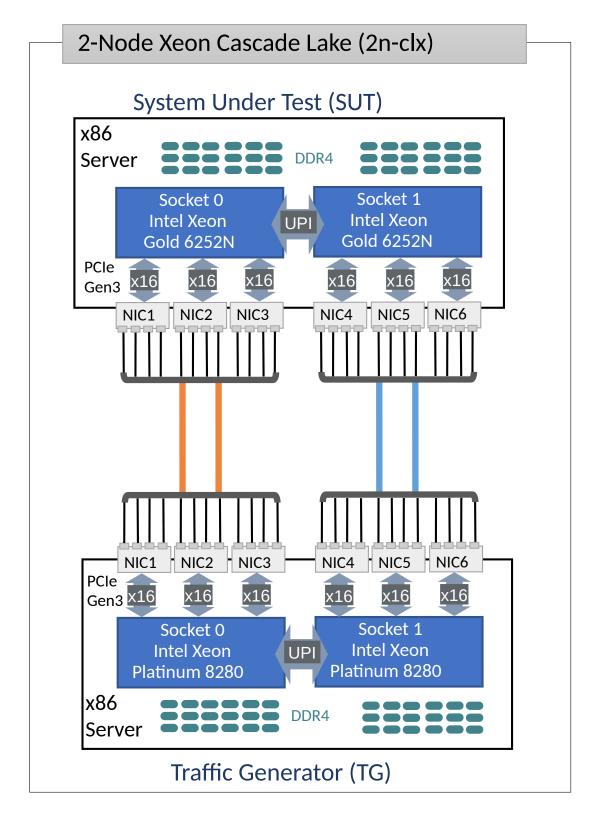

# 1.4.1 2-Node Xeon Cascade Lake (2n-clx)

Three 2n-clx testbeds are in operation in FD.io labs. Each 2n-clx testbed is built with two SuperMicro SYS-7049GP-TRT servers, SUTs are equipped with two Intel Xeon Gold 6252N processors (35.75 MB Cache, 2.30 GHz, 24 cores). TGs are equiped with Intel Xeon Cascade Lake Platinum 8280 processors (38.5 MB Cache, 2.70 GHz, 28 cores). 2n-clx physical topology is shown below.

SUT servers are populated with the following NIC models:

- 1. NIC-1: x710-DA4 4p10GE Intel.

- 2. NIC-2: xxv710-DA2 2p25GE Intel.

- 3. NIC-3: cx556a-edat ConnectX5 2p100GE Mellanox.

- 4. NIC-4: empty, future expansion.

- 5. NIC-5: empty, future expansion.

6. NIC-6: empty, future expansion.

TG servers run T-Rex application and are populated with the following NIC models:

- 1. NIC-1: x710-DA4 4p10GE Intel.

- 2. NIC-2: xxv710-DA2 2p25GE Intel.

- 3. NIC-3: cx556a-edat ConnectX5 2p100GE Mellanox.

- 4. NIC-4: empty, future expansion.

- 5. NIC-5: empty, future expansion.

- 6. NIC-6: x710-DA4 4p10GE Intel. (For self-tests.)

All Intel Xeon Cascade Lake servers run with Intel Hyper-Threading enabled, doubling the number of logical cores exposed to Linux.

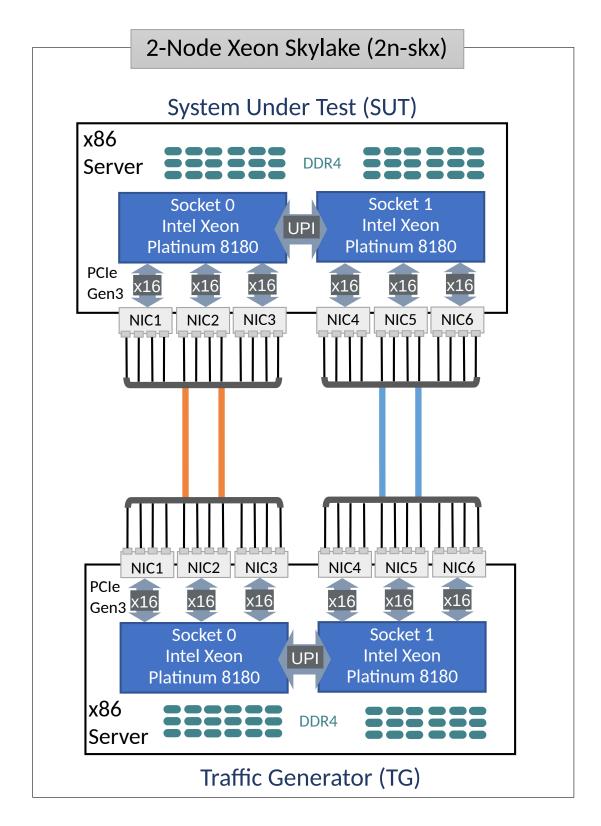

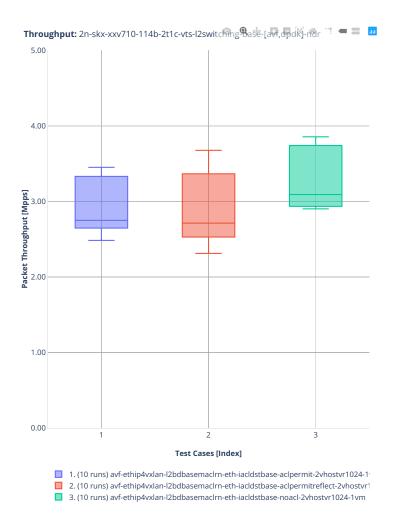

# 1.4.2 2-Node Xeon Skylake (2n-skx)

Four 2n-skx testbeds are in operation in FD.io labs. Each 2n-skx testbed is built with two SuperMicro SYS-7049GP-TRT servers, each in turn equipped with two Intel Xeon Skylake Platinum 8180 processors (38.5 MB Cache, 2.50 GHz, 28 cores). 2n-skx physical topology is shown below.

SUT servers are populated with the following NIC models:

- 1. NIC-1: x710-DA4 4p10GE Intel.

- 2. NIC-2: xxv710-DA2 2p25GE Intel.

- 3. NIC-3: empty, future expansion.

- 4. NIC-4: empty, future expansion.

- 5. NIC-5: empty, future expansion.

6. NIC-6: empty, future expansion.

TG servers run T-Rex application and are populated with the following NIC models:

- 1. NIC-1: x710-DA4 4p10GE Intel.

- 2. NIC-2: xxv710-DA2 2p25GE Intel.

- 3. NIC-3: empty, future expansion.

- 4. NIC-4: empty, future expansion.

- 5. NIC-5: empty, future expansion.

- 6. NIC-6: x710-DA4 4p10GE Intel. (For self-tests.)

All Intel Xeon Skylake servers run with Intel Hyper-Threading enabled, doubling the number of logical cores exposed to Linux, with 56 logical cores and 28 physical cores per processor socket.

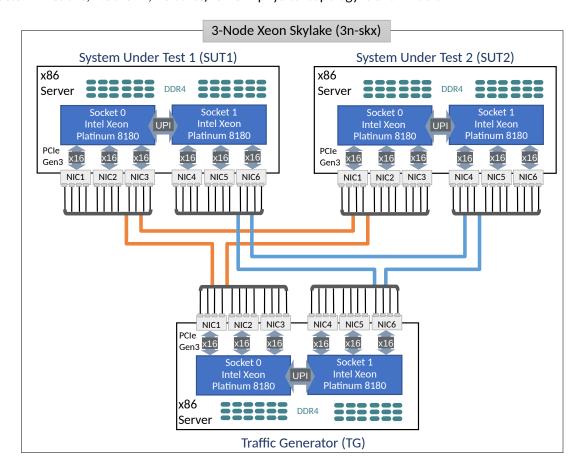

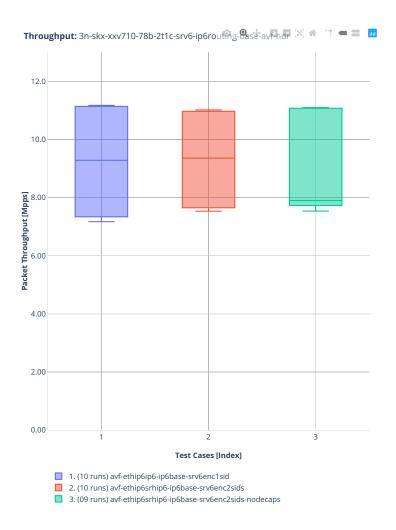

# 1.4.3 3-Node Xeon Skylake (3n-skx)

Two 3n-skx testbeds are in operation in FD.io labs. Each 3n-skx testbed is built with three SuperMicro SYS-7049GP-TRT servers, each in turn equipped with two Intel Xeon Skylake Platinum 8180 processors (38.5 MB Cache, 2.50 GHz, 28 cores). 3n-skx physical topology is shown below.

SUT1 and SUT2 servers are populated with the following NIC models:

- 1. NIC-1: x710-DA4 4p10GE Intel.

- 2. NIC-2: xxv710-DA2 2p25GE Intel.

- 3. NIC-3: empty, future expansion.

- 4. NIC-4: empty, future expansion.

- 5. NIC-5: empty, future expansion.

- 6. NIC-6: empty, future expansion.

TG servers run T-Rex application and are populated with the following NIC models:

- 1. NIC-1: x710-DA4 4p10GE Intel.

- 2. NIC-2: xxv710-DA2 2p25GE Intel.

- 3. NIC-3: empty, future expansion.

- 4. NIC-4: empty, future expansion.

- 5. NIC-5: empty, future expansion.

- 6. NIC-6: x710-DA4 4p10GE Intel. (For self-tests.)

All Intel Xeon Skylake servers run with Intel Hyper-Threading enabled, doubling the number of logical cores exposed to Linux, with 56 logical cores and 28 physical cores per processor socket.

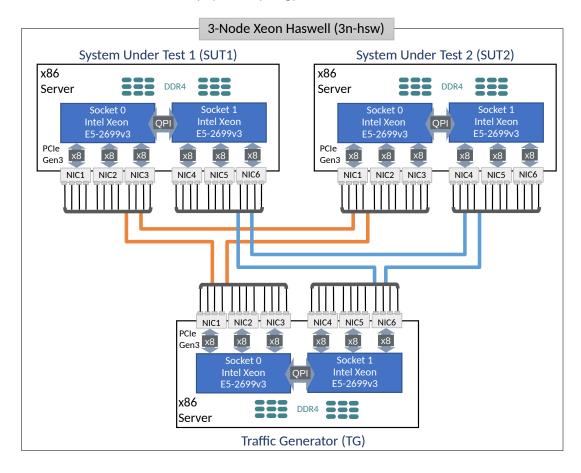

# 1.4.4 3-Node Xeon Haswell (3n-hsw)

Three 3n-hsw testbeds are in operation in FD.io labs. Each 3n-hsw testbed is built with three Cisco UCS-c240m3 servers, each in turn equipped with two Intel Xeon Haswell-SP E5-2699v3 processors (45 MB Cache, 2.3 GHz, 18 cores). 3n-hsw physical topology is shown below.

SUT1 and SUT2 servers are populated with the following NIC models:

- 1. NIC-1: VIC 1385 2p40GE Cisco.

- 2. NIC-2: NIC x520 2p10GE Intel.

- 3. NIC-3: empty.

- 4. NIC-4: NIC xl710-QDA2 2p40GE Intel.

- 5. NIC-5: NIC x710-DA2 2p10GE Intel.

- 6. NIC-6: QAT 8950 50G (Walnut Hill) Intel.

TG servers run T-Rex application and are populated with the following NIC models:

- 1. NIC-1: NIC xl710-QDA2 2p40GE Intel.

- 2. NIC-2: NIC x710-DA2 2p10GE Intel.

- 3. NIC-3: empty.

- 4. NIC-4: NIC xI710-QDA2 2p40GE Intel.

- 5. NIC-5: NIC x710-DA2 2p10GE Intel.

- 6. NIC-6: NIC x710-DA2 2p10GE Intel. (For self-tests.)

All Intel Xeon Haswell servers run with Intel Hyper-Threading disabled, making the number of logical cores exposed to Linux match the number of 18 physical cores per processor socket.

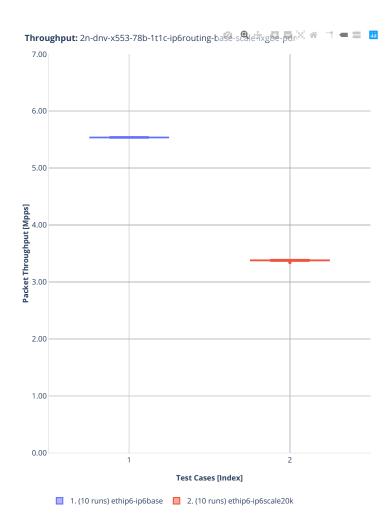

# 1.4.5 2-Node Atom Denverton (2n-dnv)

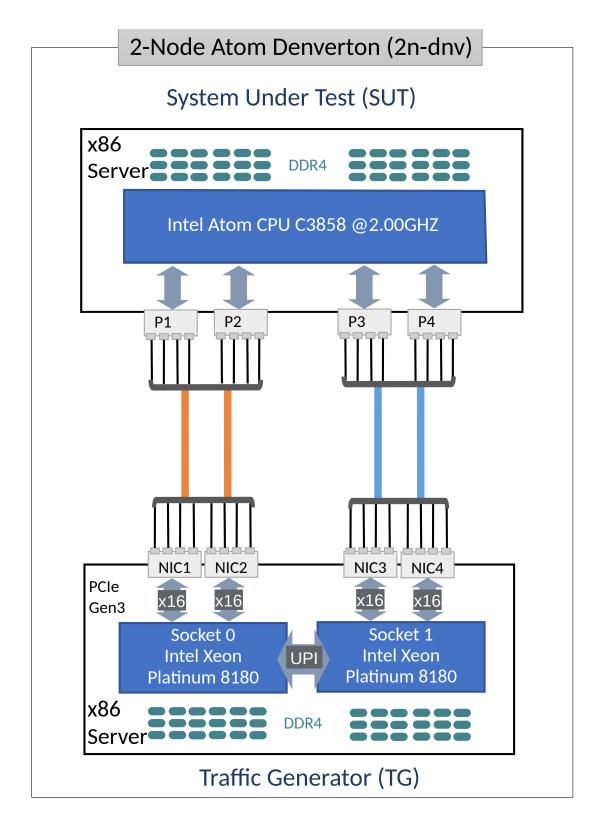

2n-dnv testbed is built with: i) one Intel S2600WFT server acting as TG and equipped with two Intel Xeon Skylake Platinum 8180 processors (38.5 MB Cache, 2.50 GHz, 28 cores), and ii) one SuperMicro SYS-E300-9A server acting as SUT and equipped with one Intel Atom C3858 processor (12 MB Cache, 2.00 GHz, 12 cores). 2n-dnv physical topology is shown below.

SUT server have four internal 10G NIC port:

- 1. P-1: x553 copper port.

- 2. P-2: x553 copper port.

- 3. P-3: x553 fiber port.

- 4. P-4: x553 fiber port.

TG server run T-Rex software traffic generator and are populated with the following NIC models:

- 1. NIC-1: x550-T2 2p10GE Intel.

- 2. NIC-2: x550-T2 2p10GE Intel.

- 3. NIC-3: x520-DA2 2p10GE Intel.

- 4. NIC-4: x520-DA2 2p10GE Intel.

The 2n-dnv testbed is in operation in Intel SH labs.

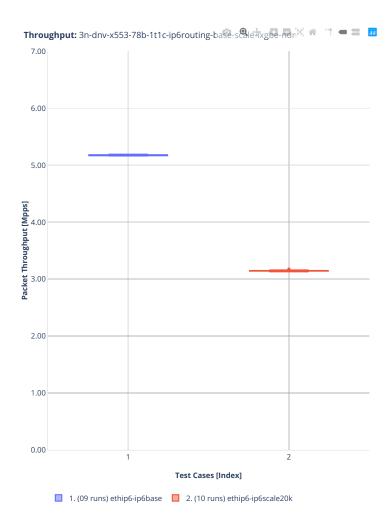

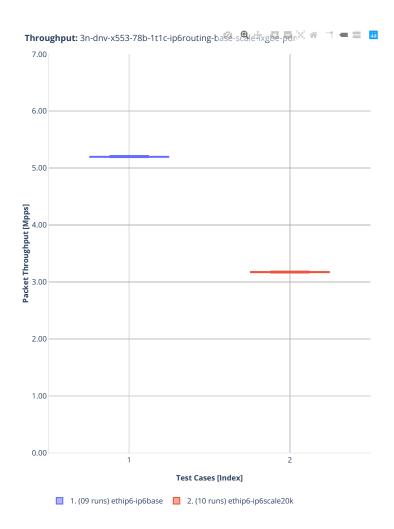

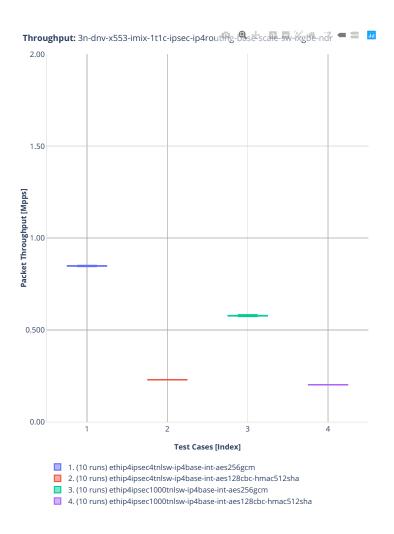

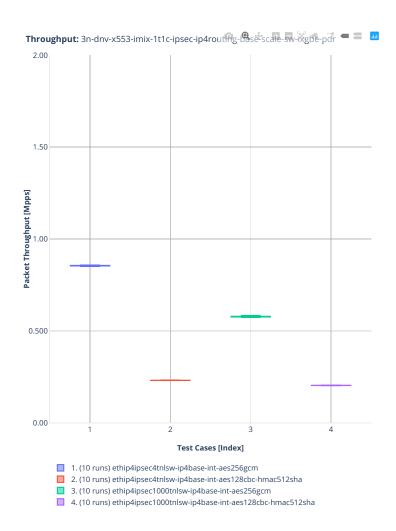

# 1.4.6 3-Node Atom Denverton (3n-dnv)

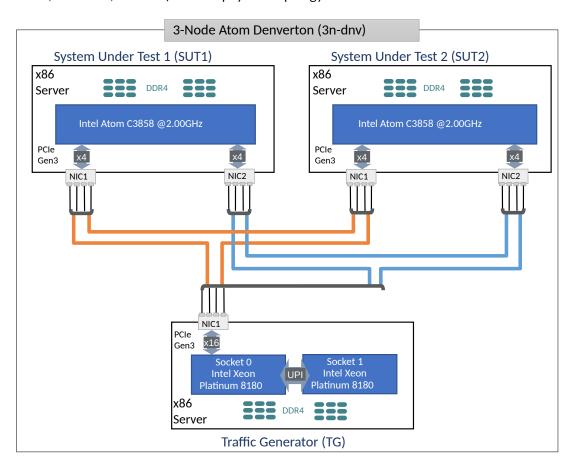

One 3n-dnv testbed is built with: i) one SuperMicro SYS-7049GP-TRT server acting as TG and equipped with two Intel Xeon Skylake Platinum 8180 processors (38.5 MB Cache, 2.50 GHz, 28 cores), and ii) one SuperMicro SYS-E300-9A server acting as SUT and equipped with one Intel Atom C3858 processor (12 MB Cache, 2.00 GHz, 12 cores). 3n-dnv physical topology is shown below.

SUT1 and SUT2 servers are populated with the following NIC models:

- 1. NIC-1: x553 2p10GE fiber Intel.

- 2. NIC-2: x553 2p10GE copper Intel.

TG servers run T-Rex application and are populated with the following NIC models:

1. NIC-1: x710-DA4 4p10GE Intel.

# 1.4.7 3-Node ARM TaiShan (3n-tsh)

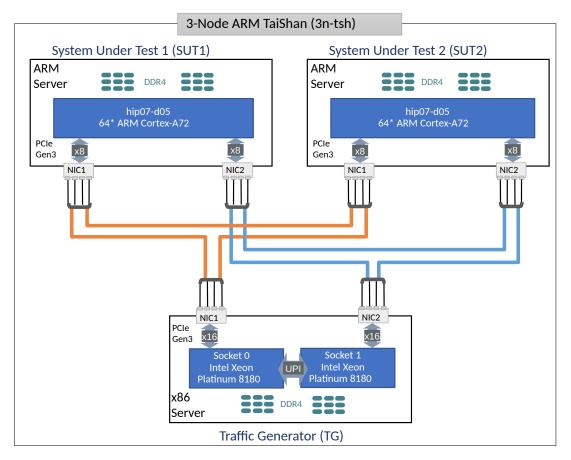

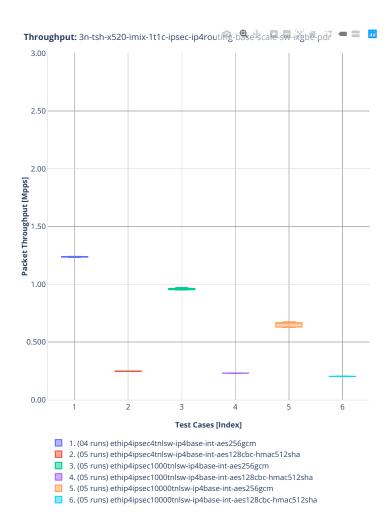

One 3n-tsh testbed is built with: i) one SuperMicro SYS-7049GP-TRT server acting as TG and equipped with two Intel Xeon Skylake Platinum 8180 processors (38.5 MB Cache, 2.50 GHz, 28 cores), and ii)

one Huawei TaiShan 2280 server acting as SUT and equipped with one hip07-d05 processor (64\* ARM Cortex-A72). 3n-tsh physical topology is shown below.

SUT1 and SUT2 servers are populated with the following NIC models:

- 1. NIC-1: connectx4 2p25GE Mellanox.

- 2. NIC-2: x520 2p10GE Intel.

TG servers run T-Rex application and are populated with the following NIC models:

- 1. NIC-1: x710-DA4 4p10GE Intel.

- 2. NIC-2: xxv710-DA2 2p25GE Intel.

# 1.5 Test Methodology

# 1.5.1 Terminology

- Frame size: size of an Ethernet Layer-2 frame on the wire, including any VLAN tags (dot1q, dot1ad) and Ethernet FCS, but excluding Ethernet preamble and inter-frame gap. Measured in Bytes.

- Packet size: same as frame size, both terms used interchangeably.

- Inner L2 size: for tunneled L2 frames only, size of an encapsulated Ethernet Layer-2 frame, preceded with tunnel header, and followed by tunnel trailer. Measured in Bytes.

- Inner IP size: for tunneled IP packets only, size of an encapsulated IPv4 or IPv6 packet, preceded with tunnel header, and followed by tunnel trailer. Measured in Bytes.

- Device Under Test (DUT): In software networking, "device" denotes a specific piece of software tasked with packet processing. Such device is surrounded with other software components (such

as operating system kernel). It is not possible to run devices without also running the other components, and hardware resources are shared between both. For purposes of testing, the whole set of hardware and software components is called "System Under Test" (SUT). As SUT is the part of the whole test setup performance of which can be measured with RFC 2544<sup>2</sup>, using SUT instead of RFC 2544<sup>3</sup> DUT. Device under test (DUT) can be re-introduced when analyzing test results using whitebox techniques, but this document sticks to blackbox testing.

- System Under Test (SUT): System under test (SUT) is a part of the whole test setup whose performance is to be benchmarked. The complete methodology contains other parts, whose performance is either already established, or not affecting the benchmarking result.

- **Bi-directional throughput tests**: involve packets/frames flowing in both east-west and west-east directions over every tested interface of SUT/DUT. Packet flow metrics are measured per direction, and can be reported as aggregate for both directions (i.e. throughput) and/or separately for each measured direction (i.e. latency). In most cases bi-directional tests use the same (symmetric) load in both directions.

- Uni-directional throughput tests: involve packets/frames flowing in only one direction, i.e. either east-west or west-east direction, over every tested interface of SUT/DUT. Packet flow metrics are measured and are reported for measured direction.

- Packet Loss Ratio (PLR): ratio of packets received relative to packets transmitted over the test trial duration, calculated using formula: PLR = ( pkts\_transmitted pkts\_received ) / pkts\_transmitted. For bi-directional throughput tests aggregate PLR is calculated based on the aggregate number of packets transmitted and received.

- Packet Throughput Rate: maximum packet offered load DUT/SUT forwards within the specified Packet Loss Ratio (PLR). In many cases the rate depends on the frame size processed by DUT/SUT. Hence packet throughput rate MUST be quoted with specific frame size as received by DUT/SUT during the measurement. For bi-directional tests, packet throughput rate should be reported as aggregate for both directions. Measured in packets-per-second (pps) or frames-per-second (fps), equivalent metrics.

- Bandwidth Throughput Rate: a secondary metric calculated from packet throughput rate using formula: bw\_rate = pkt\_rate \* (frame\_size + L1\_overhead) \* 8, where L1\_overhead for Ethernet includes preamble (8 Bytes) and inter-frame gap (12 Bytes). For bi-directional tests, bandwidth throughput rate should be reported as aggregate for both directions. Expressed in bits-per-second (bps).

- Non Drop Rate (NDR): maximum packet/bandwith throughput rate sustained by DUT/SUT at PLR equal zero (zero packet loss) specific to tested frame size(s). MUST be quoted with specific packet size as received by DUT/SUT during the measurement. Packet NDR measured in packets-persecond (or fps), bandwidth NDR expressed in bits-per-second (bps).

- Partial Drop Rate (PDR): maximum packet/bandwith throughput rate sustained by DUT/SUT at PLR greater than zero (non-zero packet loss) specific to tested frame size(s). MUST be quoted with specific packet size as received by DUT/SUT during the measurement. Packet PDR measured in packets-per-second (or fps), bandwidth PDR expressed in bits-per-second (bps).

- Maximum Receive Rate (MRR): packet/bandwidth rate regardless of PLR sustained by DUT/SUT under specified Maximum Transmit Rate (MTR) packet load offered by traffic generator. MUST be quoted with both specific packet size and MTR as received by DUT/SUT during the measurement. Packet MRR measured in packets-per-second (or fps), bandwidth MRR expressed in bits-per-second (bps).

- Trial: a single measurement step.

- Trial duration: amount of time over which packets are transmitted and received in a single measurement step.

<sup>&</sup>lt;sup>2</sup> https://tools.ietf.org/html/rfc2544.html

<sup>&</sup>lt;sup>3</sup> https://tools.ietf.org/html/rfc2544.html

### 1.5.2 VPP Forwarding Modes

VPP is tested in a number of L2 and IP packet lookup and forwarding modes. Within each mode baseline and scale tests are executed, the latter with varying number of lookup entries.

#### **L2 Ethernet Switching**

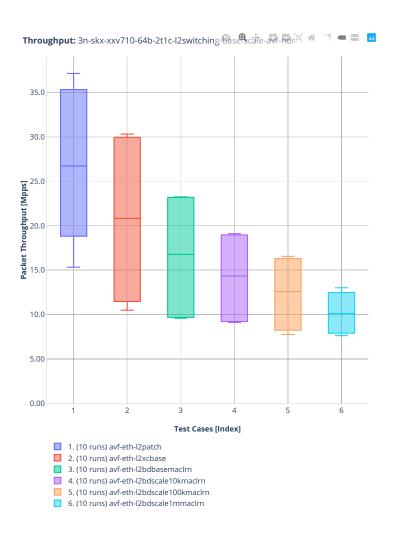

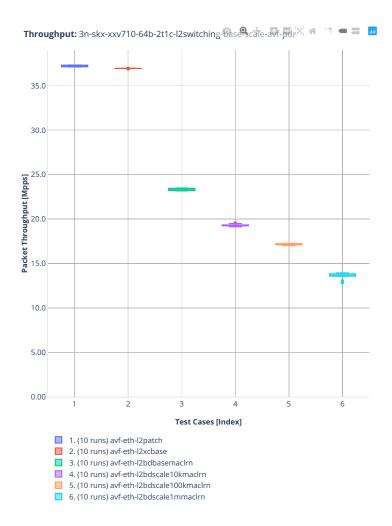

VPP is tested in three L2 forwarding modes:

- *I2patch*: L2 patch, the fastest point-to-point L2 path that loops packets between two interfaces without any Ethernet frame checks or lookups.

- *I2xc*: L2 cross-connect, point-to-point L2 path with all Ethernet frame checks, but no MAC learning and no MAC lookup.

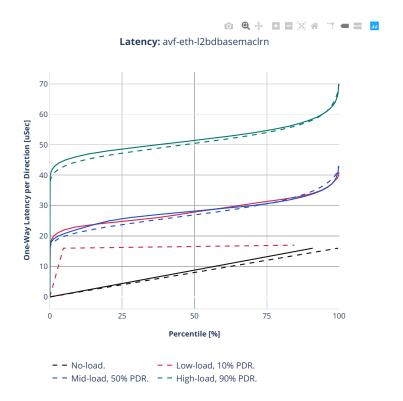

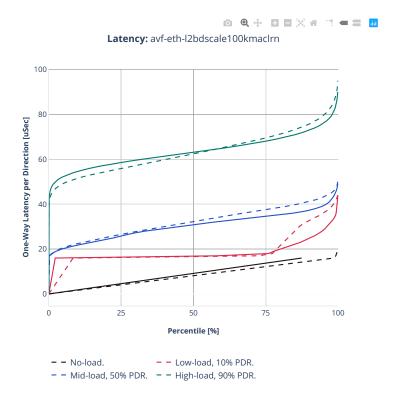

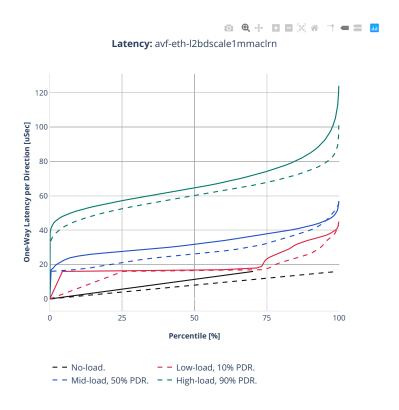

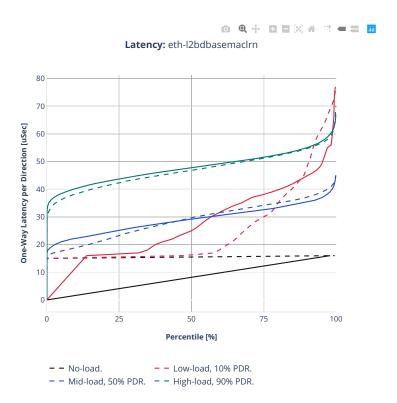

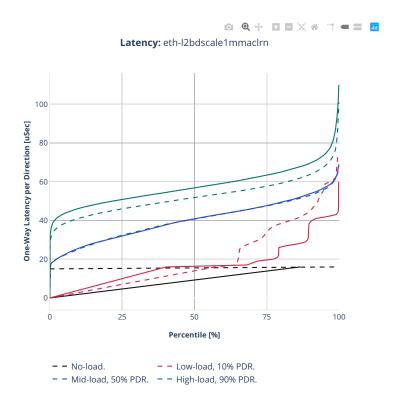

- *12bd*: L2 bridge-domain, multipoint-to-multipoint L2 path with all Ethernet frame checks, with MAC learning (unless static MACs are used) and MAC lookup.

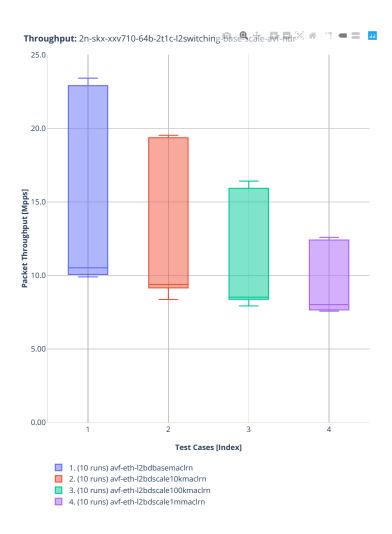

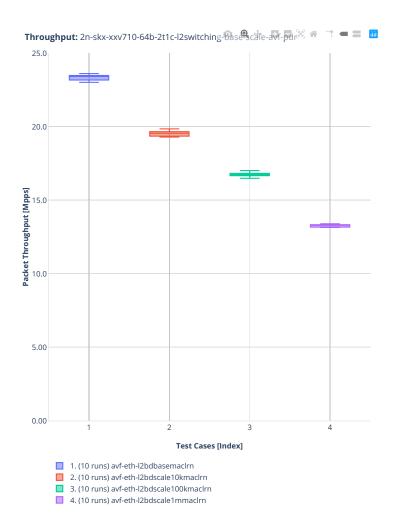

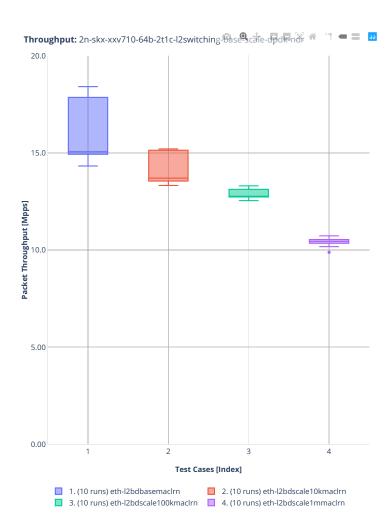

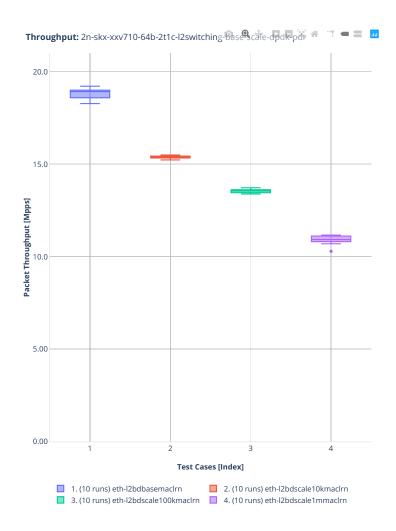

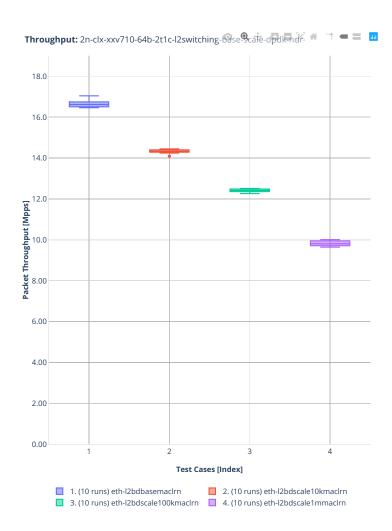

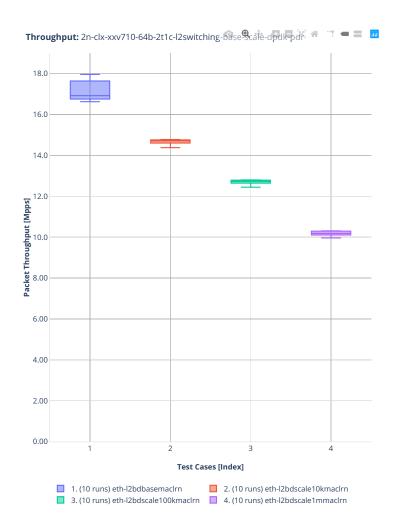

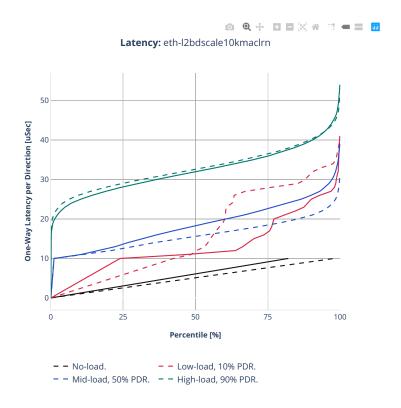

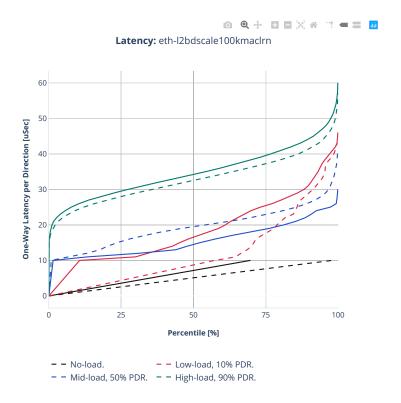

12bd tests are executed in baseline and scale configurations:

- *I2bdbase*: low number of L2 flows (254 per direction) is switched by VPP. They drive the content of MAC FIB size (508 total MAC entries). Both source and destination MAC addresses are incremented on a packet by packet basis.

- *I2bdscale*: high number of L2 flows is switched by VPP. Tested MAC FIB sizes include: i) 10k (5k unique flows per direction), ii) 100k (2x 50k flows) and iii) 1M (2x 500k). Both source and destination MAC addresses are incremented on a packet by packet basis, ensuring new entries are learn refreshed and looked up at every packet, making it the worst case scenario.

Ethernet wire encapsulations tested include: untagged, dot1q, dot1ad.

#### **IPv4 Routing**

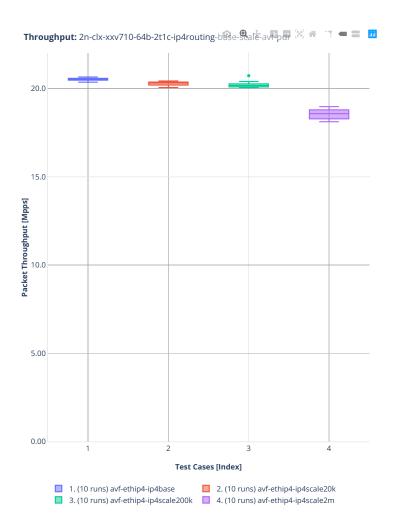

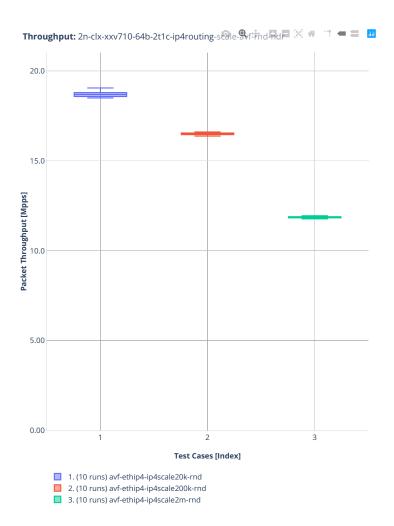

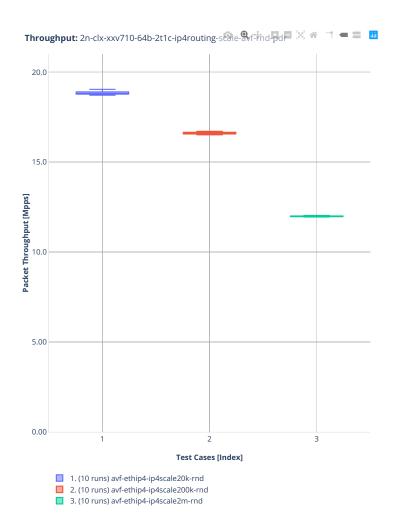

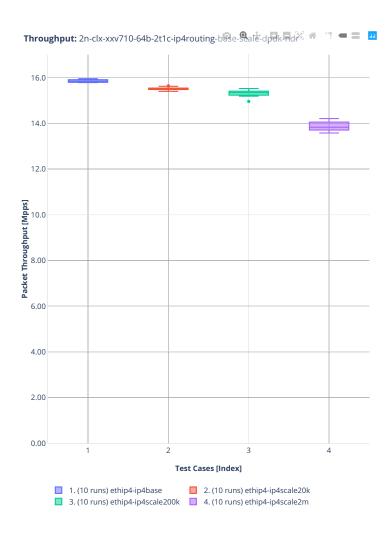

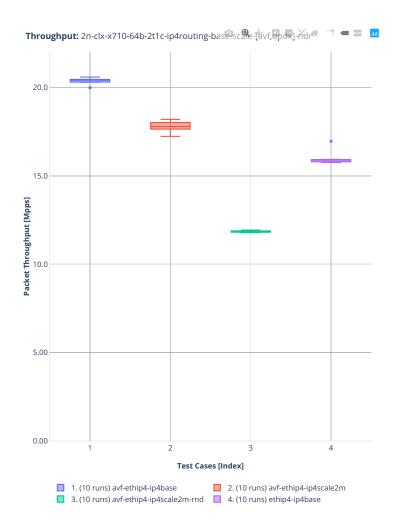

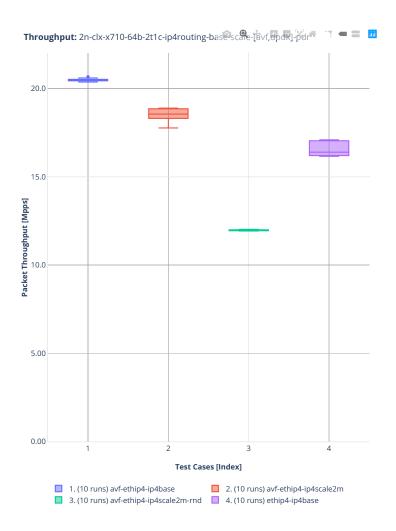

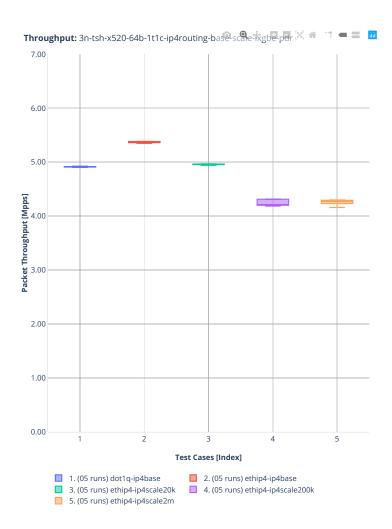

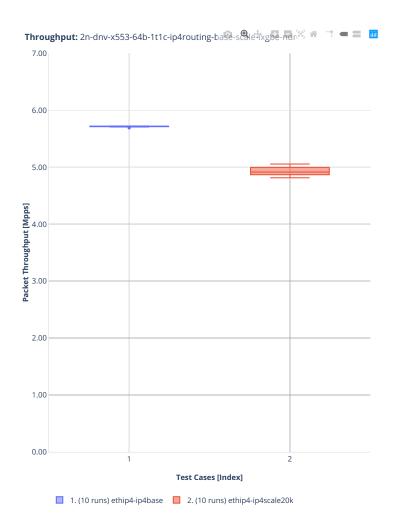

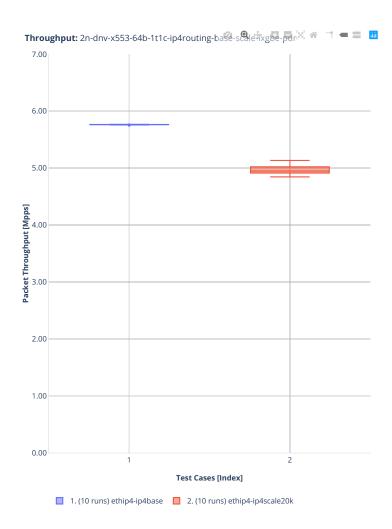

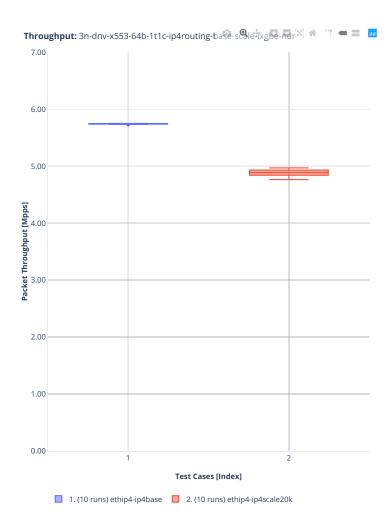

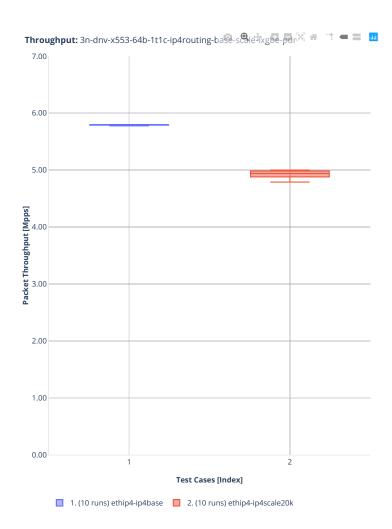

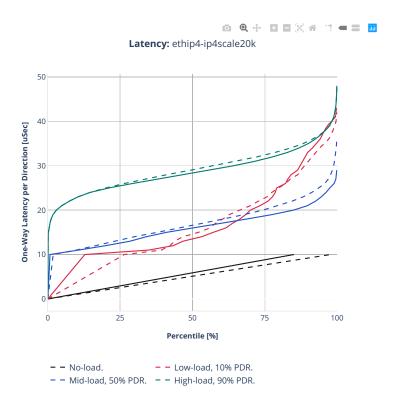

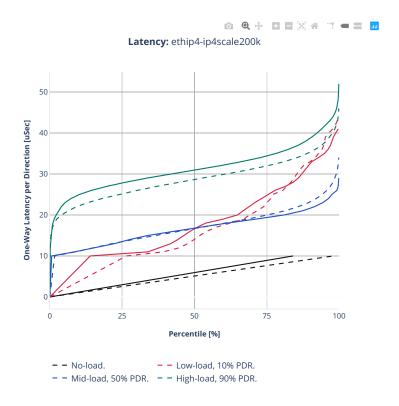

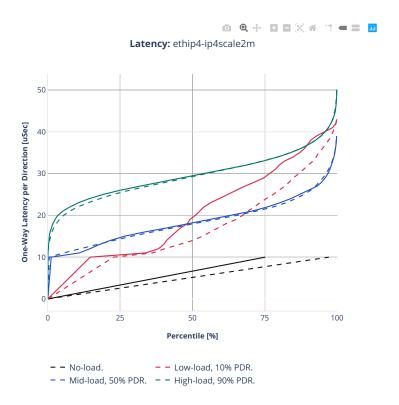

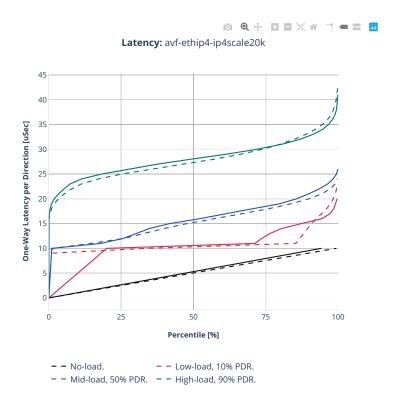

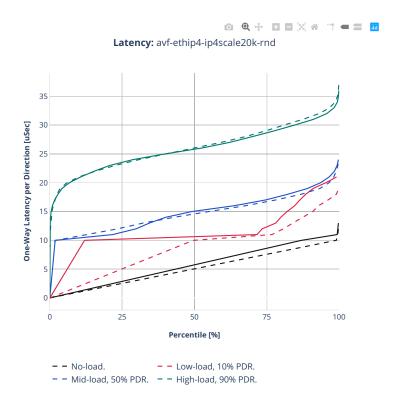

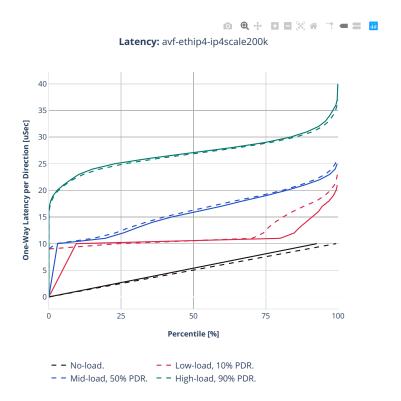

IPv4 routing tests are executed in baseline and scale configurations:

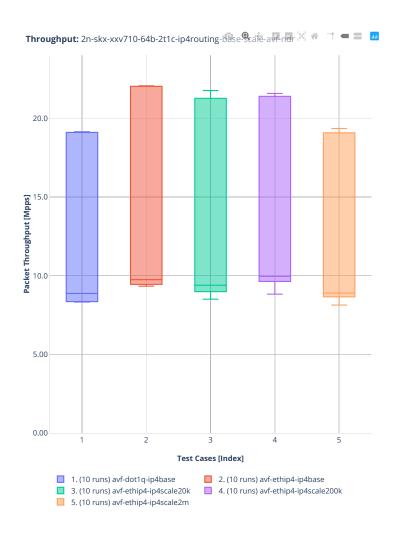

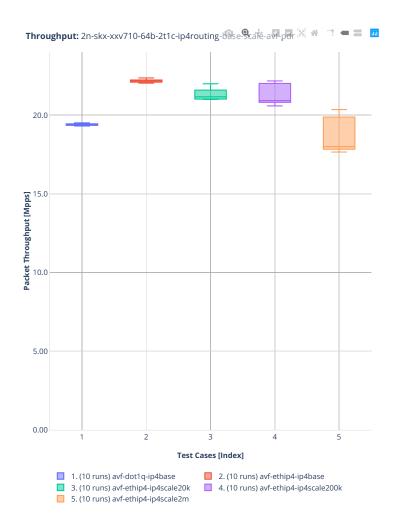

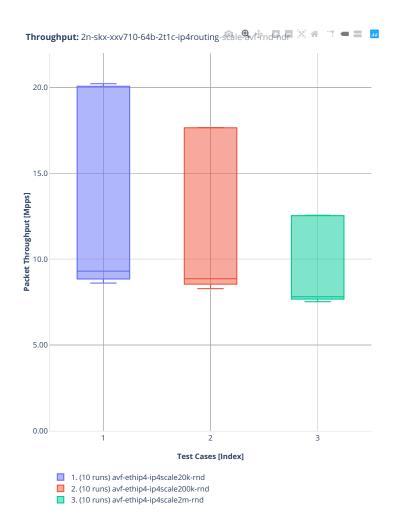

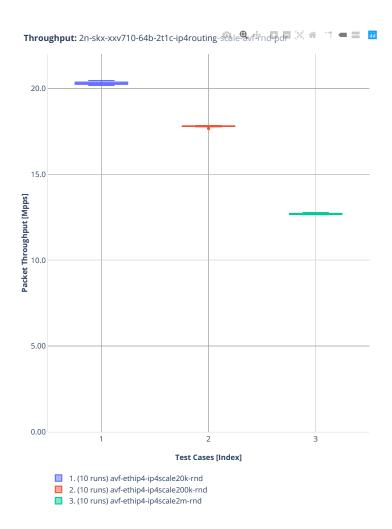

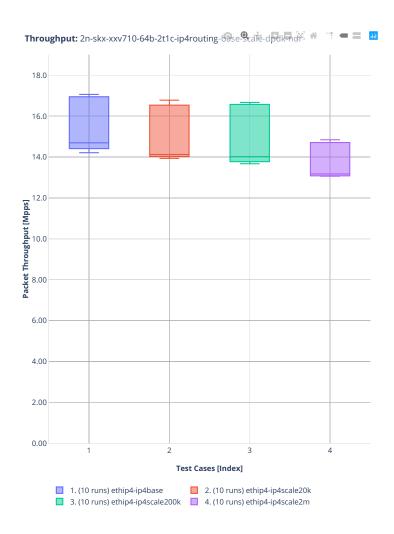

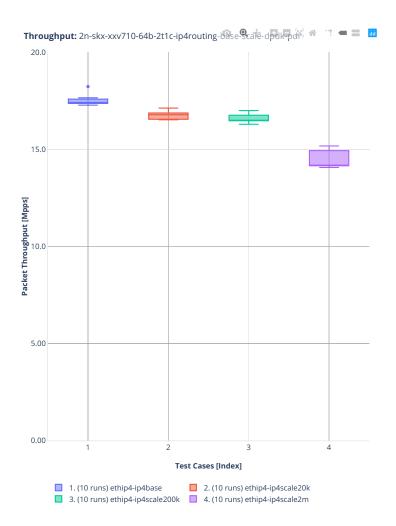

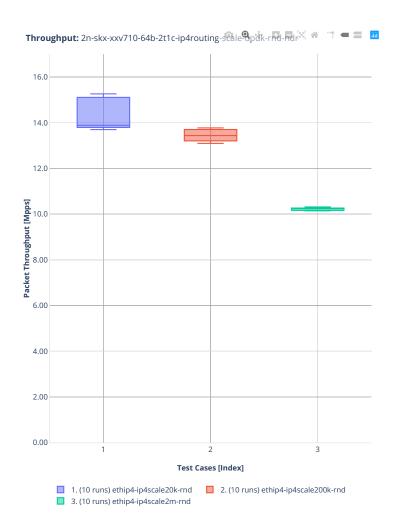

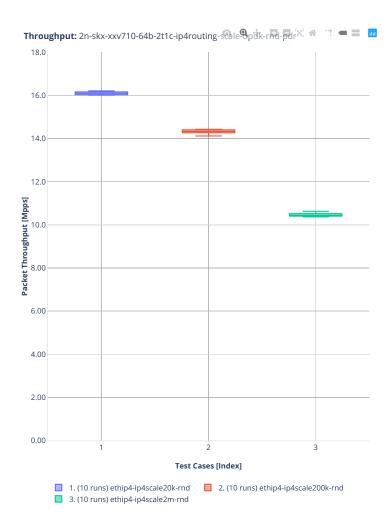

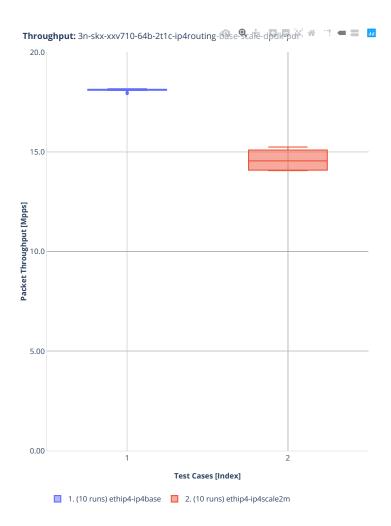

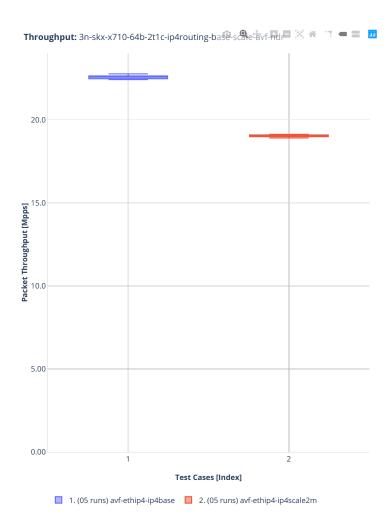

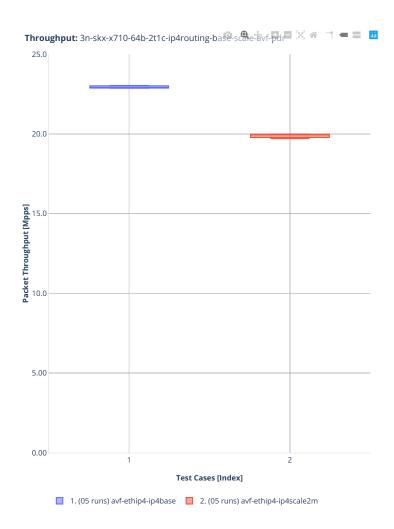

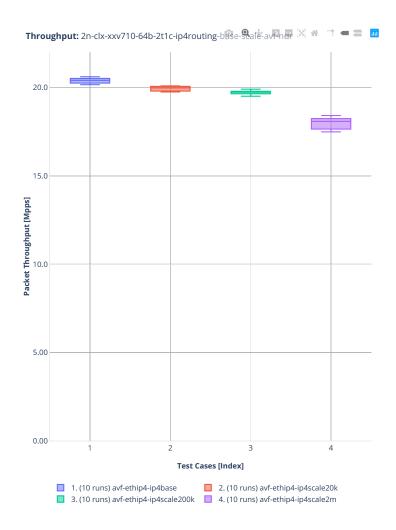

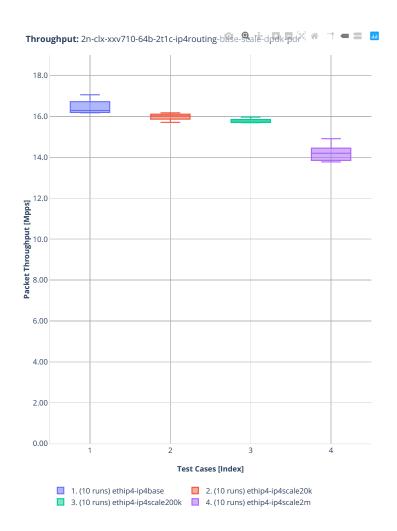

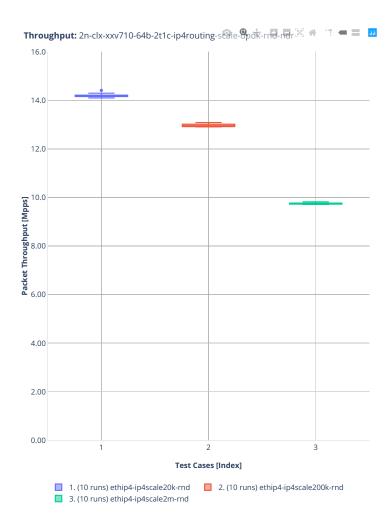

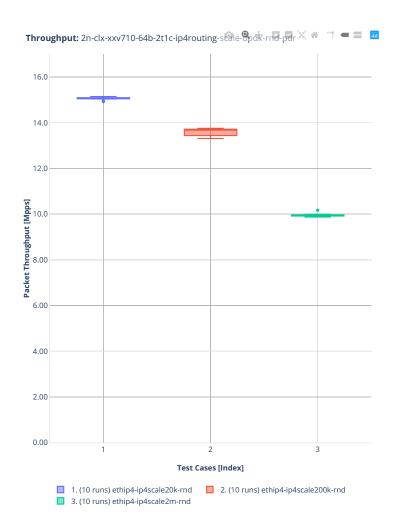

- *ip4base*: low number of IPv4 flows (253 or 254 per direction) is routed by VPP. They drive the content of IPv4 FIB size (506 or 508 total /32 prefixes). Destination IPv4 addresses are incremented on a packet by packet basis.

- *ip4scale*: high number of IPv4 flows is routed by VPP. Tested IPv4 FIB sizes of /32 prefixes include: i) 20k (10k unique flows per direction), ii) 200k (2x 100k flows) and iii) 2M (2x 1M). Destination IPv4 addresses are incremented on a packet by packet basis, ensuring new FIB entries are looked up at every packet, making it the worst case scenario.

#### **IPv6 Routing**

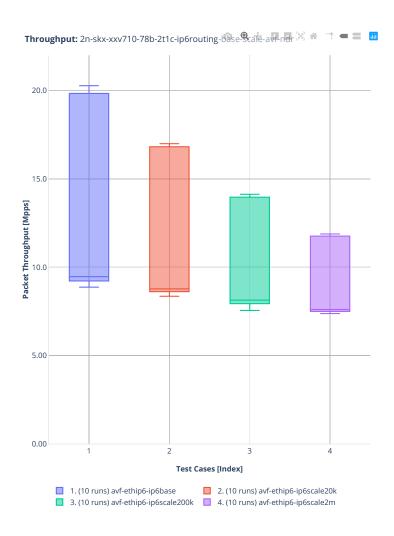

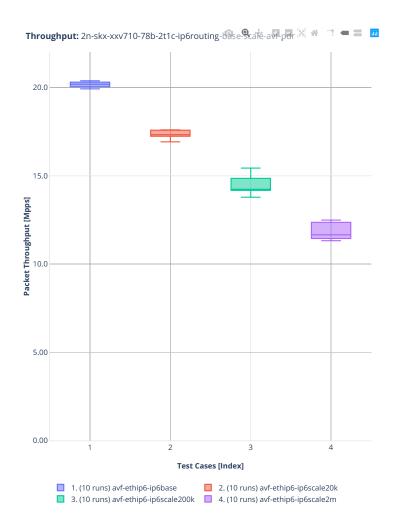

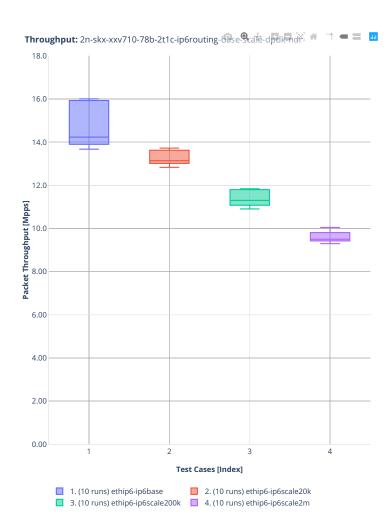

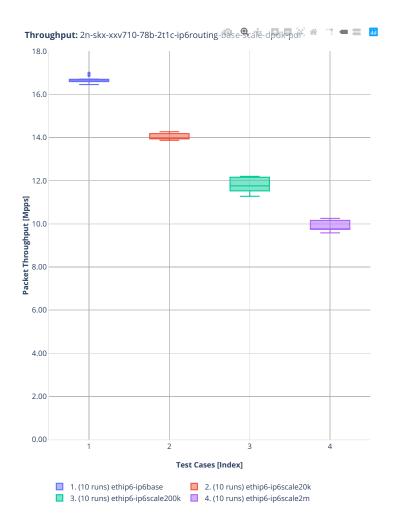

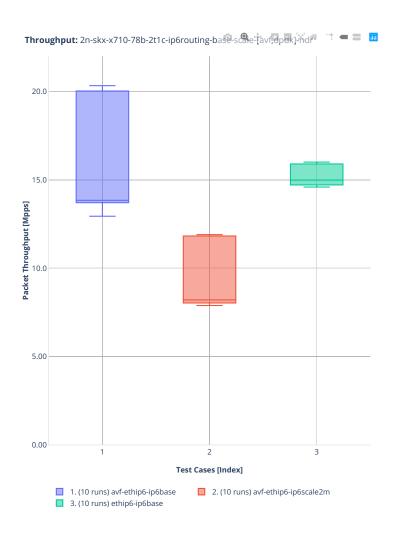

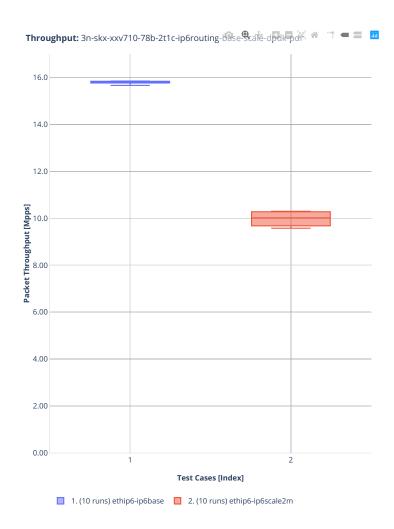

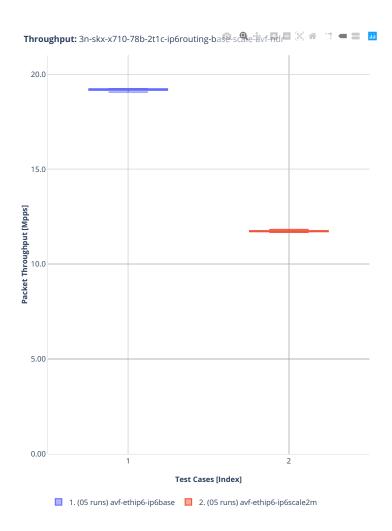

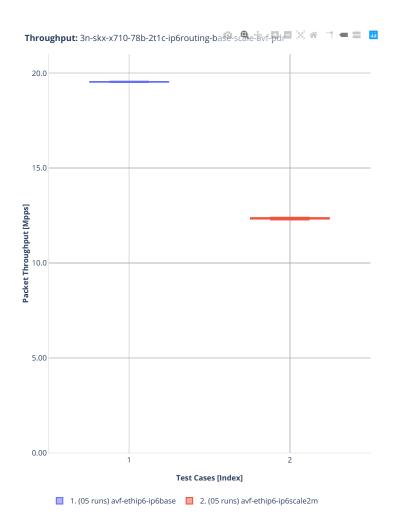

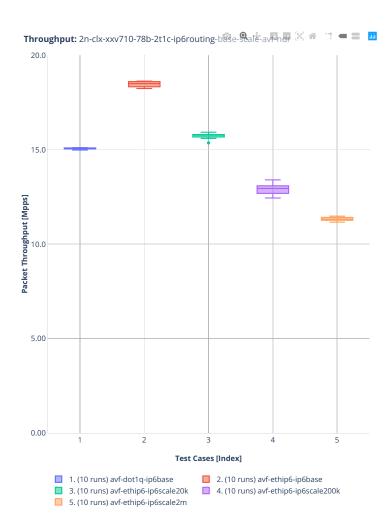

IPv6 routing tests are executed in baseline and scale configurations:

- *ip6base*: low number of IPv6 flows (253 or 254 per direction) is routed by VPP. They drive the content of IPv6 FIB size (506 or 508 total /128 prefixes). Destination IPv6 addresses are incremented on a packet by packet basis.

- *ip6scale*: high number of IPv6 flows is routed by VPP. Tested IPv6 FIB sizes of /128 prefixes include: i) 20k (10k unique flows per direction), ii) 200k (2x 100k flows) and iii) 2M (2x 1M). Destination IPv6 addresses are incremented on a packet by packet basis, ensuring new FIB entries are looked up at every packet, making it the worst case scenario.

#### **SRv6 Routing**

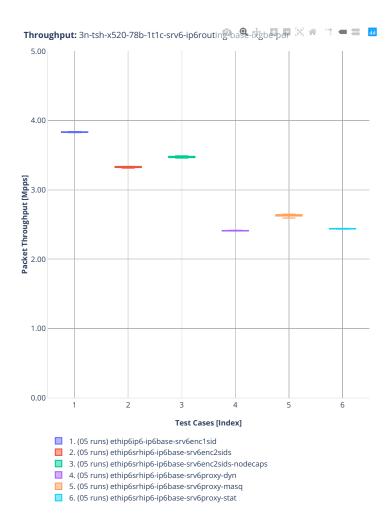

SRv6 routing tests are executed in a number of baseline configurations, in each case SR policy and steering policy are configured for one direction and one (or two) SR behaviours (functions) in the other directions:

- srv6enc1sid: One SID (no SRH present), one SR function End.

- srv6enc2sids: Two SIDs (SRH present), two SR functions End and End.DX6.

- srv6enc2sids-nodecaps: Two SIDs (SRH present) without decapsulation, one SR function End.

- srv6proxy-dyn: Dynamic SRv6 proxy, one SR function End.AD.

- srv6proxy-masq: Masquerading SRv6 proxy, one SR function End.AM.

- srv6proxy-stat: Static SRv6 proxy, one SR function End.AS.

In all listed cases low number of IPv6 flows (253 per direction) is routed by VPP.

# 1.5.3 Tunnel Encapsulations

Tunnel encapsulations testing is grouped based on the type of outer header: IPv4 or IPv6.

#### **IPv4 Tunnels**

VPP is tested in the following IPv4 tunnel baseline configurations:

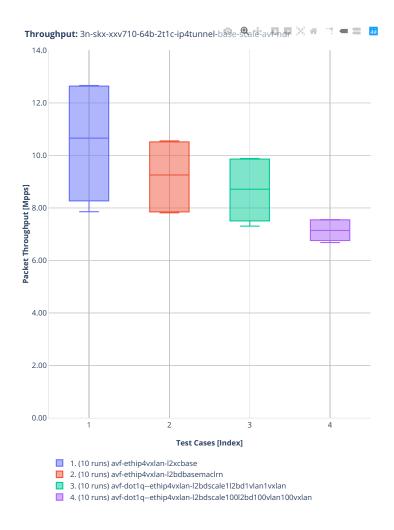

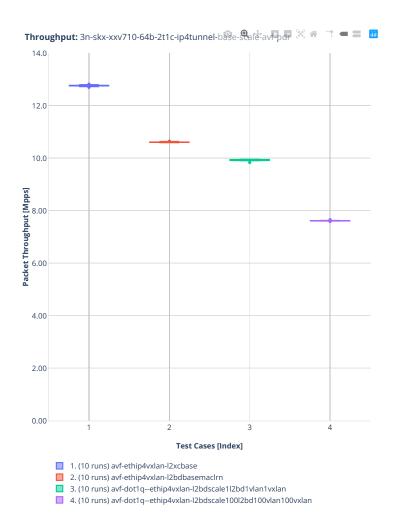

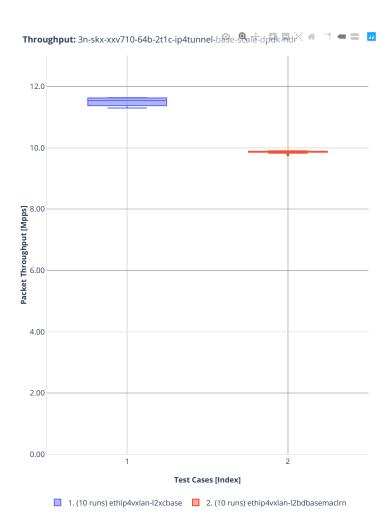

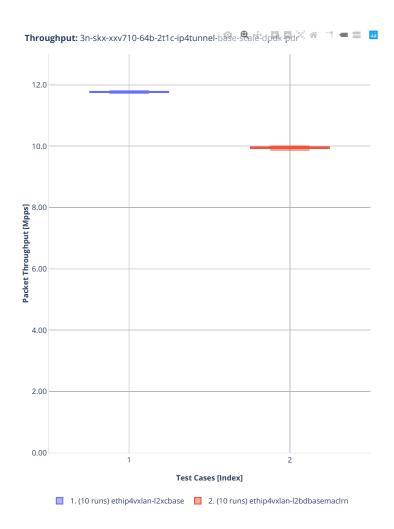

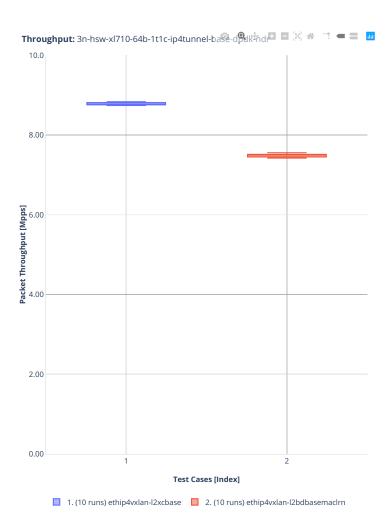

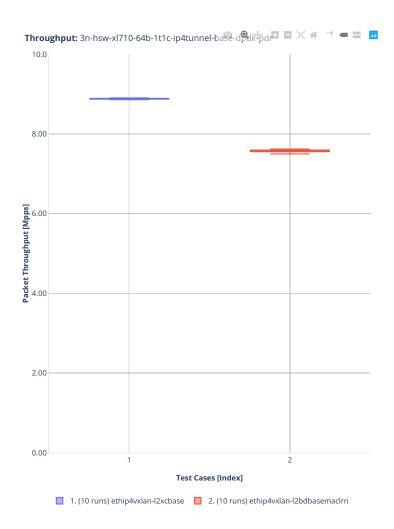

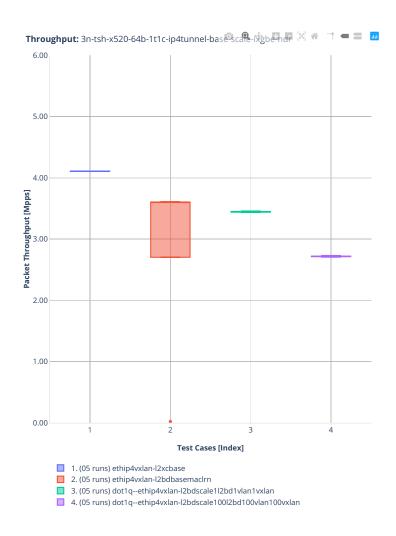

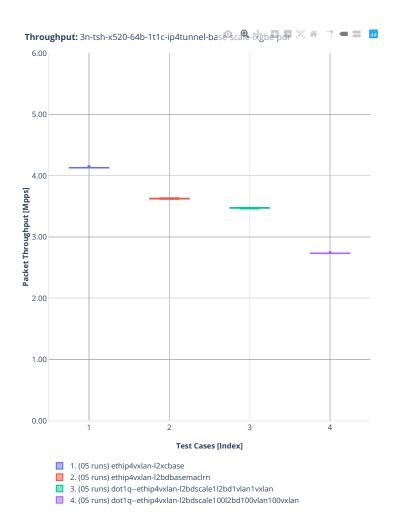

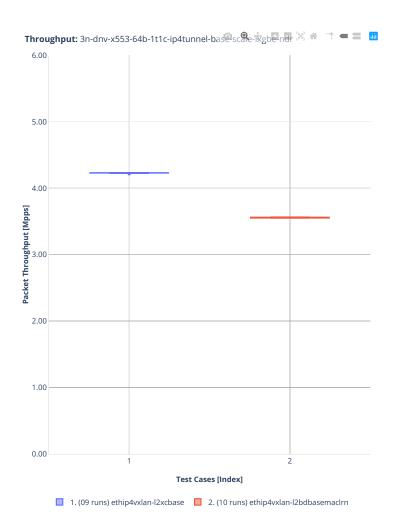

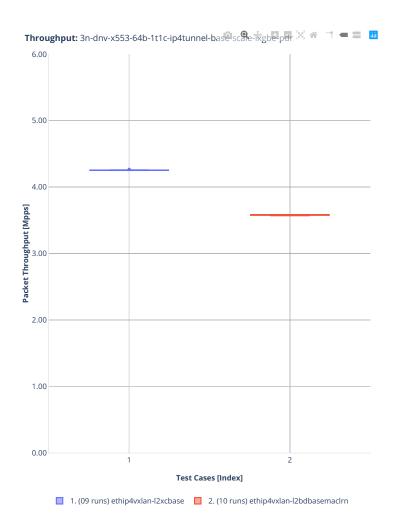

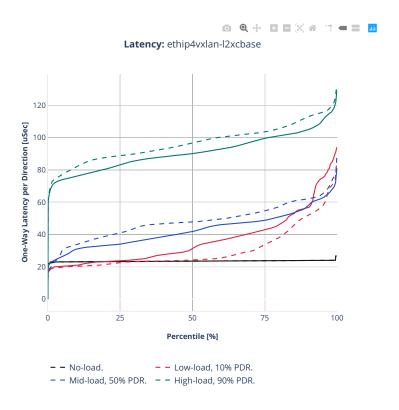

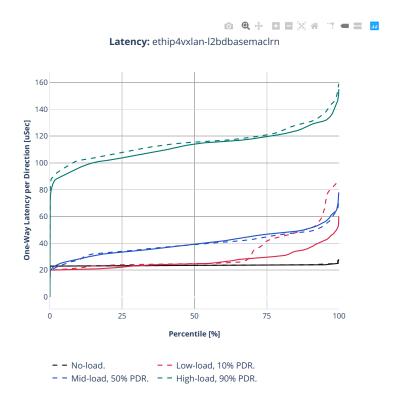

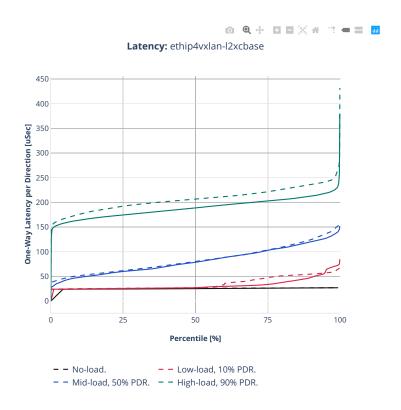

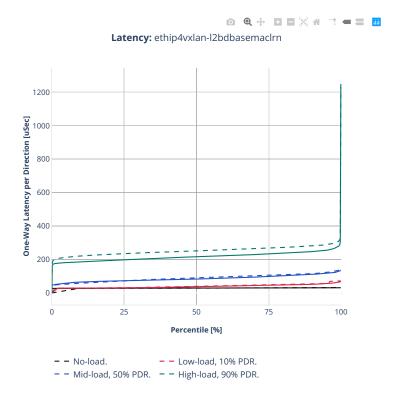

- ip4vxlan-l2bdbase: VXLAN over IPv4 tunnels with L2 bridge-domain MAC switching.

- ip4vxlan-l2xcbase: VXLAN over IPv4 tunnels with L2 cross-connect.

- ip4lispip4-ip4base: LISP over IPv4 tunnels with IPv4 routing.

- ip4lispip6-ip6base: LISP over IPv4 tunnels with IPv6 routing.

In all cases listed above low number of MAC, IPv4, IPv6 flows (253 or 254 per direction) is switched or routed by VPP.

In addition selected IPv4 tunnels are tested at scale:

• dot1q-ip4vxlanscale-l2bd: VXLAN over IPv4 tunnels with L2 bridge- domain MAC switching, with scaled up dot1q VLANs (10, 100, 1k), mapped to scaled up L2 bridge-domains (10, 100, 1k), that are in turn mapped to (10, 100, 1k) VXLAN tunnels. 64.5k flows are transmitted per direction.

#### **IPv6 Tunnels**

VPP is tested in the following IPv6 tunnel baseline configurations:

- ip6lispip4-ip4base: LISP over IPv4 tunnels with IPv4 routing.

- ip6lispip6-ip6base: LISP over IPv4 tunnels with IPv6 routing.

In all cases listed above low number of IPv4, IPv6 flows (253 or 254 per direction) is routed by VPP.

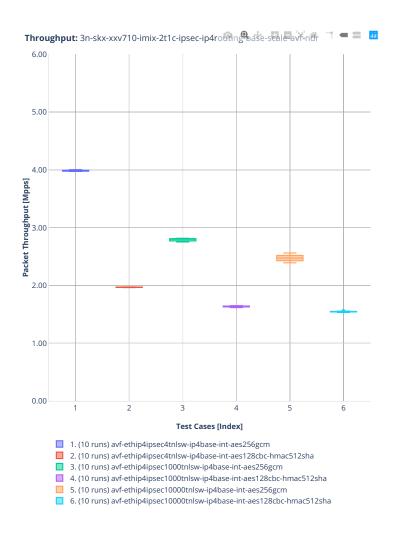

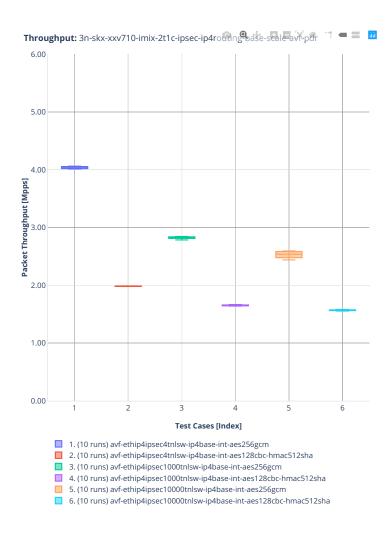

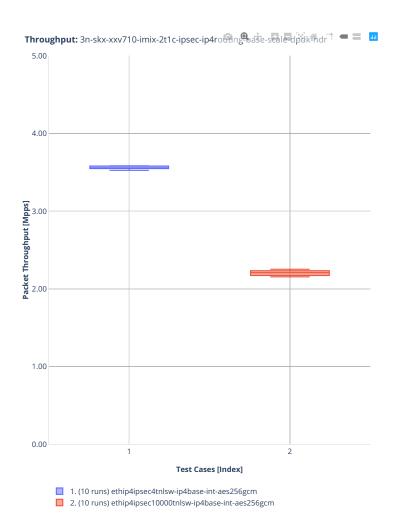

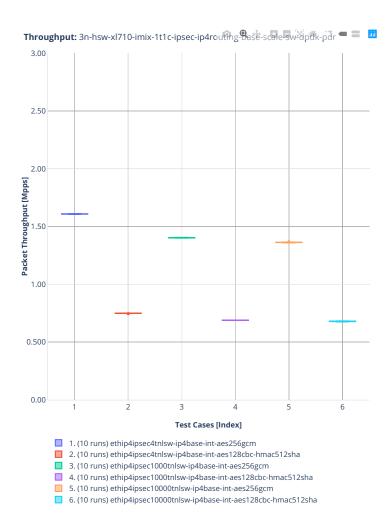

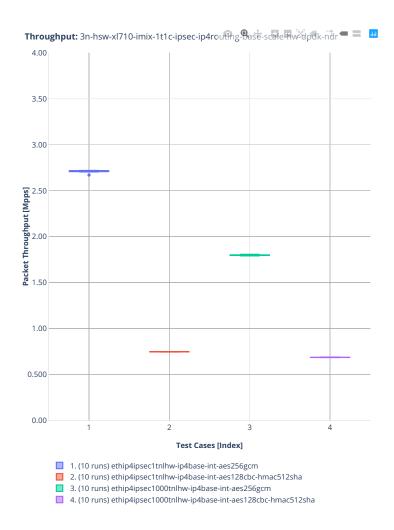

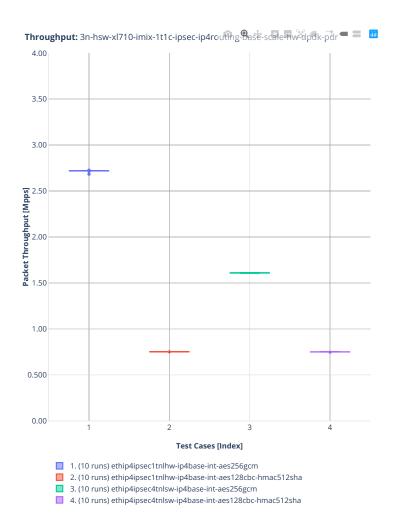

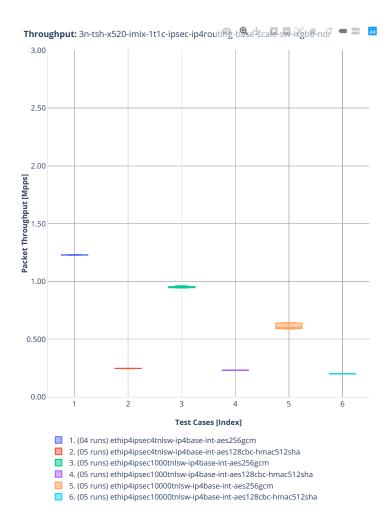

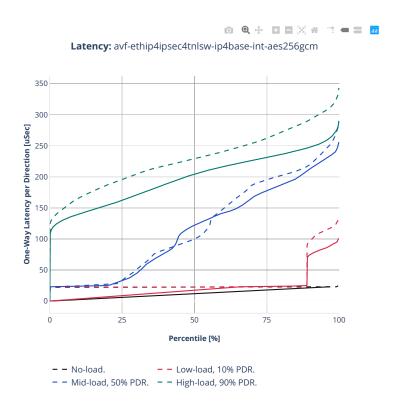

## 1.5.4 Internet Protocol Security (IPsec)

VPP IPsec performance tests are executed for the following crypto plugins:

- crypto\_native, used for software based crypto leveraging CPU platform optimizations e.g. Intel's AES-NI instruction set.

- crypto\_ipsecmb, used for hardware based crypto with Intel QAT PCIe cards.

#### **IPsec with VPP Native SW Crypto**

Currently CSIT-2009 implements following IPsec test cases relying on VPP native crypto (*crypto\_native* plugin):

| VPP Crypto Engine | ESP Encryption   | ESP Integrity | Scale Tested     |

|-------------------|------------------|---------------|------------------|

| crypto_native     | AES[128 256]-GCM | GCM           | 1 to 60k tunnels |

| crypto_native     | AES128-CBC       | SHA[256 512]  | 1 to 60k tunnels |

VPP IPsec with SW crypto are executed in both tunnel and policy modes, with tests running on 3-node testbeds: 3n-hsw and 3n-skx.

#### **IPsec with Intel QAT HW**

Currently CSIT-2009 implements following IPsec test cases relying on ipsecmb library (*crypto\_ipsecmb* plugin) and Intel QAT 8950 (50G HW crypto card):

dpdk\_cryptodev

| VPP Crypto Engine | VPP Crypto Workers  | ESP Encryption | ESP Integrity | Scale Tested     |

|-------------------|---------------------|----------------|---------------|------------------|

| crypto_ipsecmb    | sync/all workers    | AES[128 256]-  | GCM           | 1, 1k tunnels    |

|                   |                     | GCM            |               |                  |

| crypto_ipsecmb    | sync/all workers    | AES[128]-CBC   | SHA[256 512]  | 1, 1k tunnels    |

| crypto_ipsecmb    | async/crypto worker | AES[128 256]-  | GCM           | 1, 4, 1k tunnels |

|                   |                     | GCM            |               |                  |

| crypto_ipsecmb    | async/crypto worker | AES[128]-CBC   | SHA[256 512]  | 1, 4, 1k tunnels |

VPP IPsec with HW crypto are executed in both tunnel and policy modes, with tests running on 3-node Haswell testbeds (3n-hsw), as these are the only testbeds equipped with Intel QAT cards.

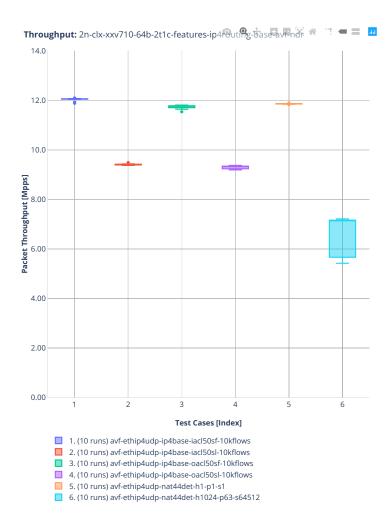

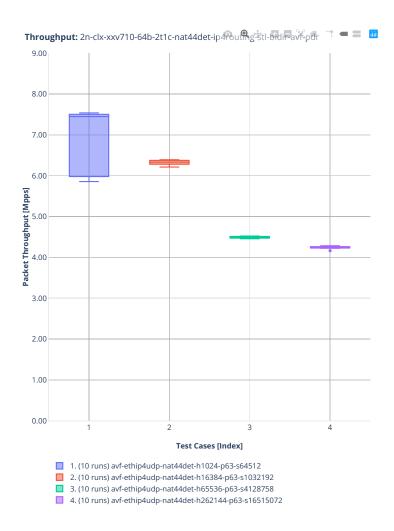

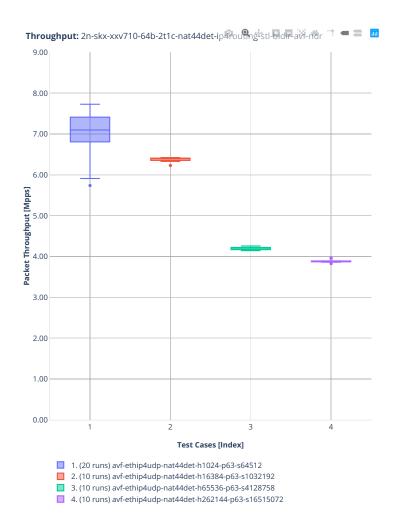

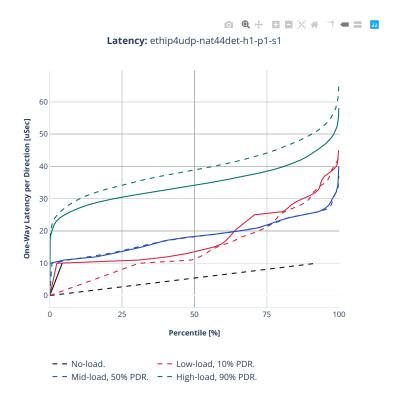

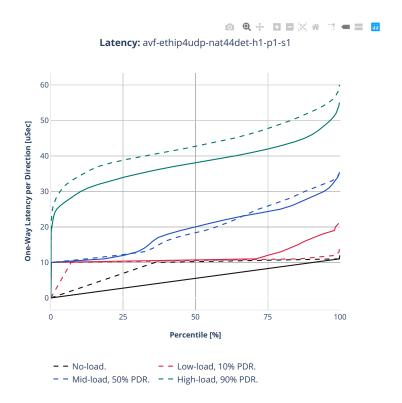

#### 1.5.5 Network Address Translation IPv4 to IPv4

#### **NAT44 Prefix Bindings**

NAT44 prefix bindings should be representative to target applications, where a number of private IPv4 addresses from the range defined by RFC 1918<sup>4</sup> is mapped to a smaller set of public IPv4 addresses from the public range.

Following quantities are used to describe inside to outside IP address and port bindings scenarios:

- inside-addresses, ports-per-inside-address, number of inside source addresses (representing inside hosts) and number of TCP/UDP source ports per inside source address.

- outside-addresses, number of outside (public) source addresses allocated to NAT44. The maximal number of ports-per-outside-address usable for NAT is 64 512 (in non-reserved port range 1024-65535, RFC 4787<sup>5</sup>).

- sharing-ratio, equal to inside-addresses / outside-addresses.

CSIT NAT44 tests are designed to take into account the maximum number of ports (sessions) required per inside host (inside-address) and at the same time to maximize the use of outside-address range by using all available outside ports. With this in mind, the following scheme of NAT44 sharing ratios has been devised for use in CSIT:

<sup>&</sup>lt;sup>4</sup> https://tools.ietf.org/html/rfc1918.html

<sup>&</sup>lt;sup>5</sup> https://tools.ietf.org/html/rfc4787.html

| ports-per-inside-address | sharing-ratio |

|--------------------------|---------------|

| 63                       | 1024          |

| 126                      | 512           |

| 252                      | 256           |

| 504                      | 128           |

Initial CSIT NAT44 tests, including associated TG/TRex traffic profiles, are based on ports-per-inside-address set to 63 and the sharing ratio of 1024. This approach is currently used for all NAT44 tests including NAT44det (NAT44 deterministic used for Carrier Grade NAT applications) and NAT44ed.

Private address ranges to be used in tests:

- 192.168.0.0 192.168.255.255 (192.168/16 prefix)

- Total of 2<sup>16</sup> (65 536) of usable IPv4 addresses.

- Used in tests for up to 65 536 inside addresses (inside hosts).

- 172.16.0.0 172.31.255.255 (172.16/12 prefix)

- Total of 2^20 (1 048 576) of usable IPv4 addresses.

- Used in tests for up to 1 048 576 inside addresses (inside hosts).

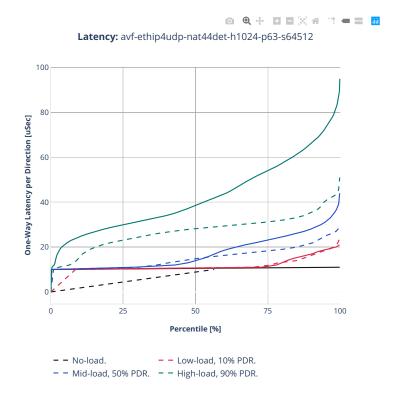

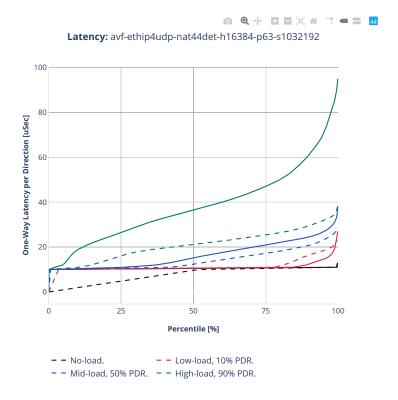

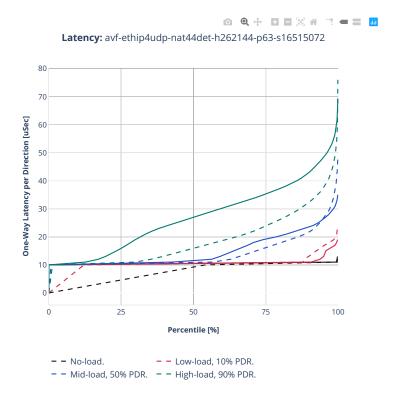

#### **NAT44 Session Scale**

NAT44 session scale tested is govern by the following logic:

- Number of inside addresses/hosts H[i] = (H[i-1] x 2^2) with H(0)=1 024, i = 1,2,3,...

- H[i] = 1 024, 4 096, 16 384, 65 536, 262 144, 1 048 576, ...

- Number of sessions S[i](ports-per-host) = H[i] \* ports-per-inside-address

- ports-per-host = 63

| i | hosts   | sessions   |

|---|---------|------------|

| 0 | 1 024   | 64 512     |

| 1 | 4 096   | 258 048    |

| 2 | 16 384  | 1 032 192  |

| 3 | 65 536  | 4 128 768  |

| 4 | 262 144 | 16 515 072 |

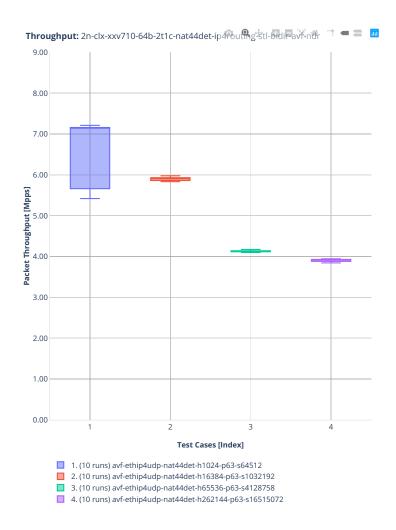

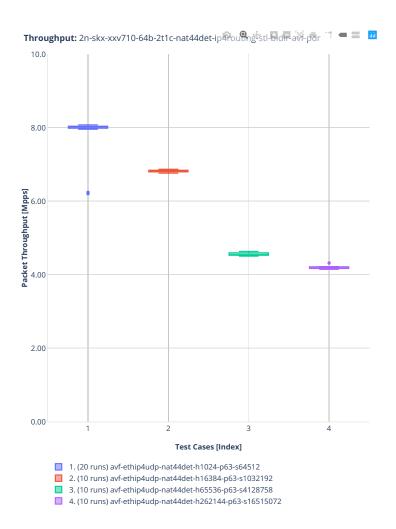

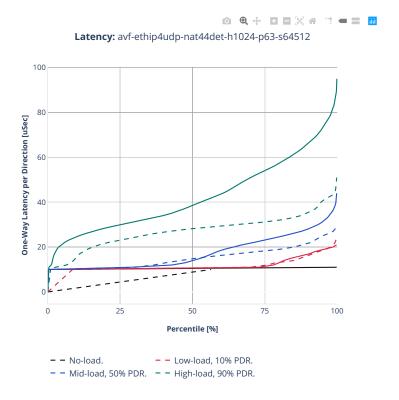

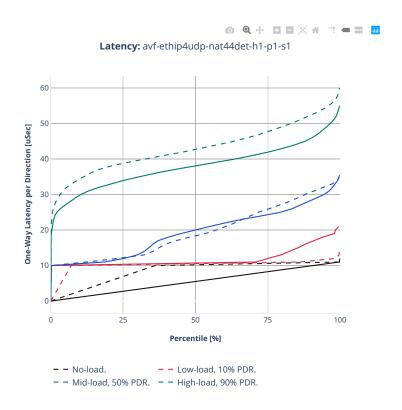

#### **NAT44 Deterministic**

NAT44det throughput tests are using TRex STL (Stateless) API and traffic profiles, similar to all other stateless packet forwarding tests like ip4, ip6 and I2, sending UDP packets in both directions inside-to-outside and outside-to-inside. See *Data Plane Throughput Tests* (page 20) for more detail.

NAT44det translation entries are created during the ramp-up phase preceding the throughput test, followed by verification that all entries are present, before proceeding to the throughput test. This ensures session setup does not impact the forwarding performance test.

Associated CSIT test cases use the following naming scheme to indicate NAT44det scenario tested:

- ethip4udp-nat44det-h{H}-p{P}-s{S}-[mrr|ndrpdr|soak]

- {H}, number of inside hosts, H = 1024, 4096, 16384, 65536, 262144.

- {P}, number of ports per inside host, P = 63.

- {S}, number of sessions, S = 64512, 258048, 1032192, 4128768, 16515072.

- [mrr|ndrpdr|soak], MRR, NDRPDR or SOAK test.

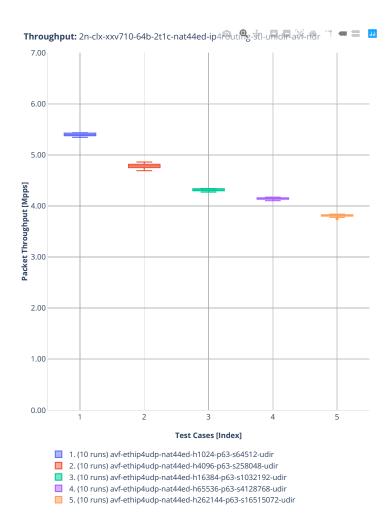

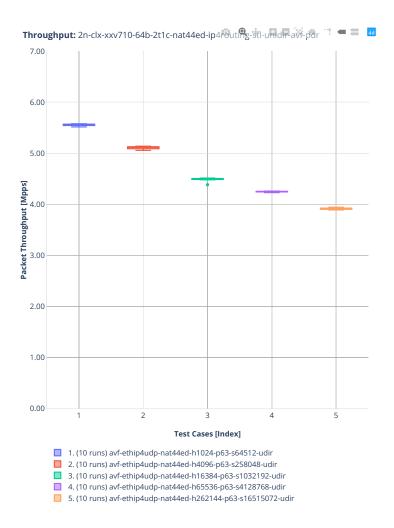

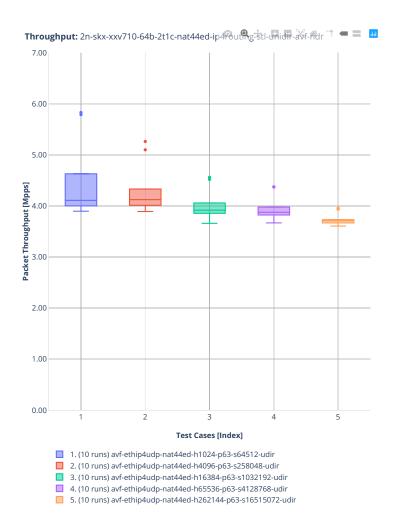

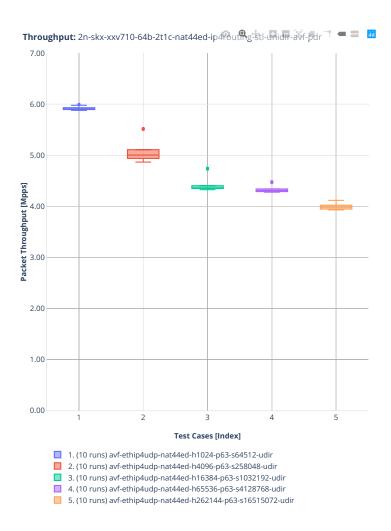

#### **NAT44 Endpoint-Dependent**

NAT44ed is benchmarked using following methodologies:

- Uni-directional throughput using stateless traffic profile.

- Connections-per-second using stateful traffic profile.

- Bi-directional throughput using stateful traffic profile.

Uni-directional NAT44ed throughput tests are using TRex STL (Stateless) APIs and traffic profiles, but with packets sent only in inside-to-outside direction. Due to indeterministic bindings of outside to inside (src\_addr,src\_port) that are created dynamically at flow start bidirectional testing is not possible with stateless traffic profiles. See *Data Plane Throughput Tests* (page 20) for more detail.

Similarly to NAT44det, NAT44ed uni-directional throughput tests include a ramp-up phase to establish and verify the presence of required NAT44ed binding entries. NAT44ed CPS (connections-per-second) and throughput / PPS stateful tests do not have a ramp-up phase.

Stateful NAT44ed tests are using TRex ASTF (Advanced Stateful) APIs and traffic profiles, with packets sent in both directions. Tests are run with both UDP and TCP/IP sessions.

Associated CSIT test cases use the following naming scheme to indicate NAT44DET case tested:

- Stateless: ethip4udp-nat44ed-h{H}-p{P}-s{S}-udir-[mrr|ndrpdr|soak]

- {H}, number of inside hosts, H = 1024, 4096, 16384, 65536, 262144.

- {P}, number of ports per inside host, P = 63.

- {S}, number of sessions, S = 64512, 258048, 1032192, 4128768, 16515072.

- udir-[mrr|ndrpdr|soak], unidirectional stateless tests MRR, NDRPDR or SOAK.

- Stateful: ethip4[udp|tcp]-nat44ed-h{H}-p{P}-s{S}-[cps|pps]-[mrr|ndrpdr]

- [udp|tcp], UDP or TCP/IP sessions

- {H}, number of inside hosts, H = 1024, 4096, 16384, 65536, 262144.

- {P}, number of ports per inside host, P = 63.

- {S}, number of sessions, S = 64512, 258048, 1032192, 4128768, 16515072.

- [cps|pps], connections-per-second session establishment rate or packets-per-second throughput rate.

- [mrr|ndrpdr], bidirectional stateful tests MRR, NDRPDR.

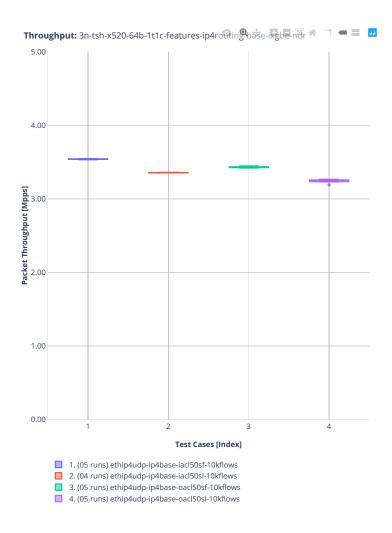

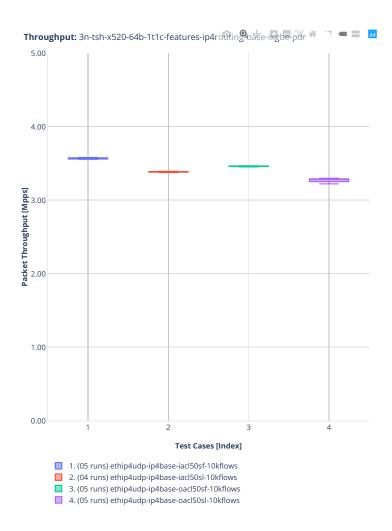

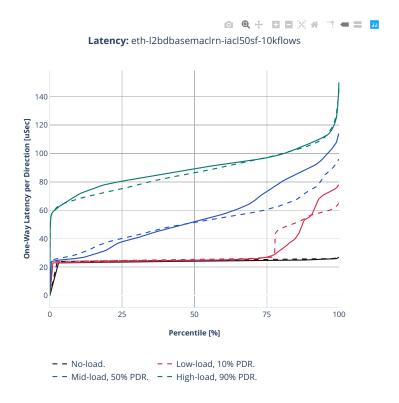

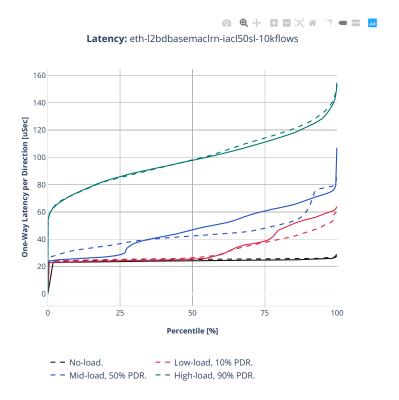

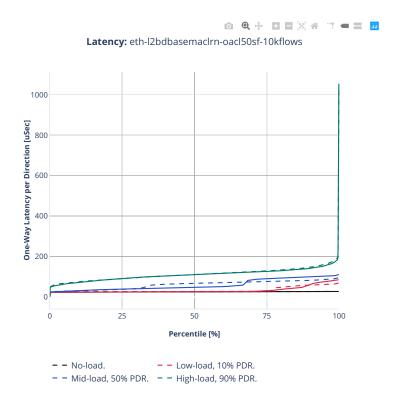

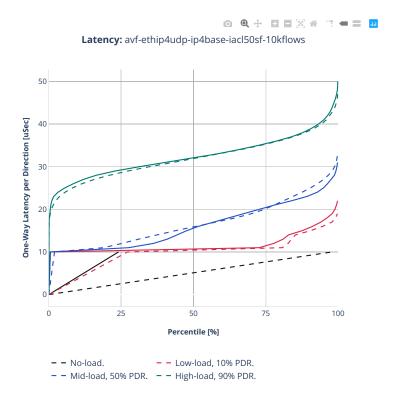

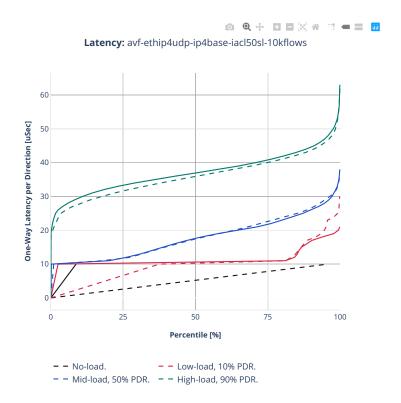

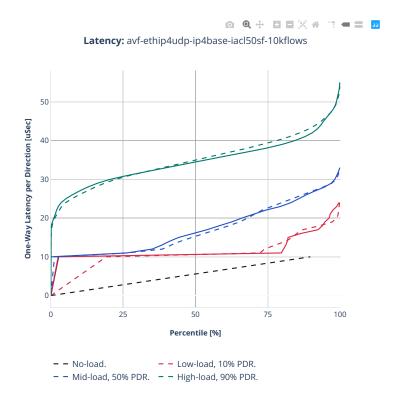

#### 1.5.6 Access Control Lists

VPP is tested in a number of data plane feature configurations across different forwarding modes. Following sections list features tested.

#### **ACL Security-Groups**

Both stateless and stateful access control lists (ACL), also known as security-groups, are supported by VPP.

Following ACL configurations are tested for MAC switching with L2 bridge-domains:

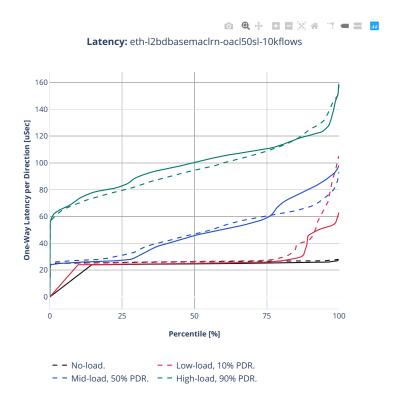

- *12bdbasemaclrn-iacl{E}sl-{F}flows*: Input stateless ACL, with {E} entries and {F} flows.

- *12bdbasemaclrn-oacl{E}sl-{F}flows*: Output stateless ACL, with {E} entries and {F} flows.

- *12bdbasemaclrn-iacl{E}sf-{F}flows*: Input stateful ACL, with {E} entries and {F} flows.

- *12bdbasemaclrn-oacl{E}sf-{F}flows*: Output stateful ACL, with {E} entries and {F} flows.

Following ACL configurations are tested with IPv4 routing:

- ip4base-iacl{E}sl-{F}flows: Input stateless ACL, with {E} entries and {F} flows.

- ip4base-oacl{E}sl-{F}flows: Output stateless ACL, with {E} entries and {F} flows.

- ip4base-iacl{E}sf-{F}flows: Input stateful ACL, with {E} entries and {F} flows.

- ip4base-oacl{E}sf-{F}flows: Output stateful ACL, with {E} entries and {F} flows.

ACL tests are executed with the following combinations of ACL entries and number of flows:

- ACL entry definitions

- flow non-matching deny entry: (src-ip4, dst-ip4, src-port, dst-port).

- flow matching permit ACL entry: (src-ip4, dst-ip4).

- {E} number of non-matching deny ACL entries, {E} = [1, 10, 50].

- {F} number of UDP flows with different tuple (src-ip4, dst-ip4, src-port, dst-port), {F} = [100, 10k, 100k].

- All {E}x{F} combinations are tested per ACL type, total of 9.

#### **ACL MAC-IP**

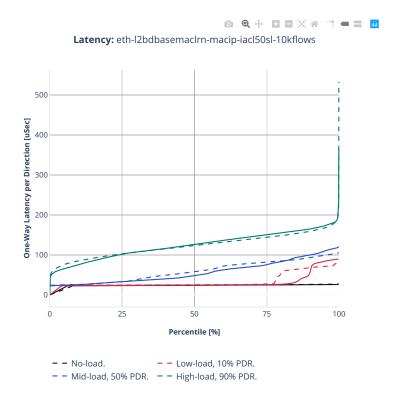

MAC-IP binding ACLs are tested for MAC switching with L2 bridge-domains:

• I2bdbasemacIrn-macip-iacl{E}sI-{F}flows: Input stateless ACL, with {E} entries and {F} flows.

MAC-IP ACL tests are executed with the following combinations of ACL entries and number of flows:

- ACL entry definitions

- flow non-matching deny entry: (dst-ip4, dst-mac, bit-mask)

- flow matching permit ACL entry: (dst-ip4, dst-mac, bit-mask)

- {E} number of non-matching deny ACL entries, {E} = [1, 10, 50]

- {F} number of UDP flows with different tuple (dst-ip4, dst-mac), {F} = [100, 10k, 100k]

- All {E}x{F} combinations are tested per ACL type, total of 9.

#### 1.5.7 Data Plane Throughput

# **Data Plane Throughput Tests**

Network data plane throughput is measured using multiple test methods in order to obtain representative and repeatable results across the large set of performance test cases implemented and executed within CSIT

Following throughput test methods are used:

- MLRsearch Multiple Loss Ratio search

- MRR Maximum Receive Rate

- PLRsearch Probabilistic Loss Ratio search

Description of each test method is followed by generic test properties shared by all methods.

#### **MLRsearch Tests**

#### **Description**

Multiple Loss Ratio search (MLRsearch) tests discover multiple packet throughput rates in a single search, reducing the overall test execution time compared to a binary search. Each rate is associated with a distinct Packet Loss Ratio (PLR) criteria. In FD.io CSIT two throughput rates are discovered: Non-Drop Rate (NDR, with zero packet loss, PLR=0) and Partial Drop Rate (PDR, with PLR<0.5%). MLRsearch is compliant with RFC 2544<sup>6</sup>.

#### **Usage**

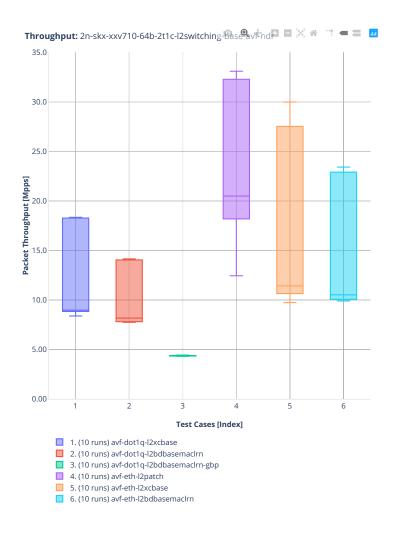

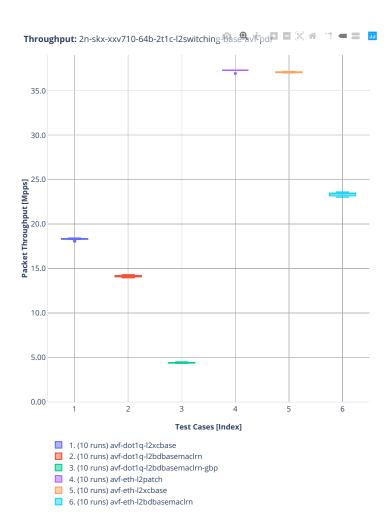

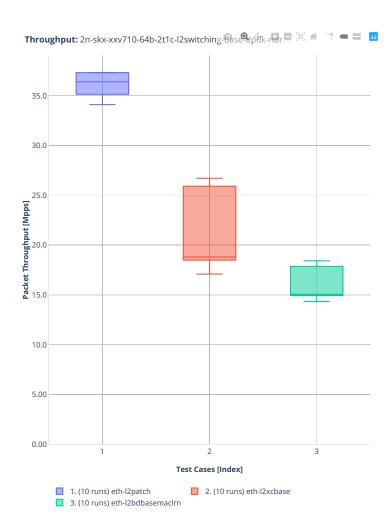

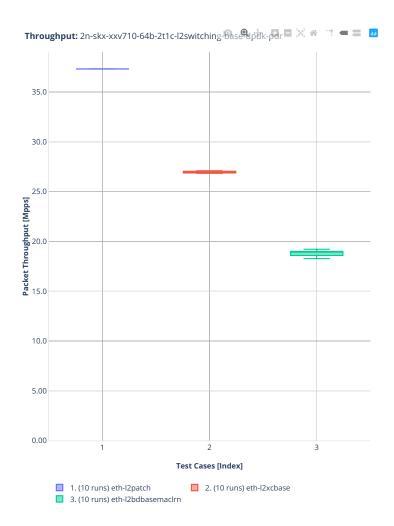

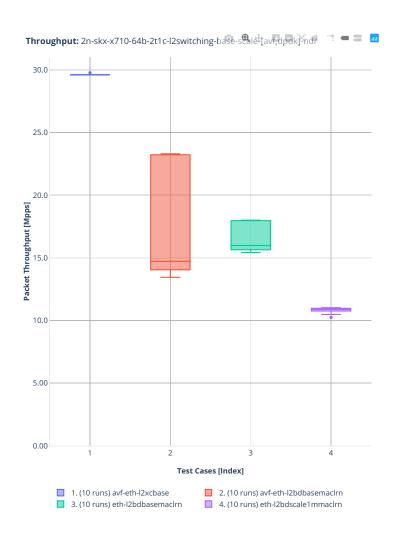

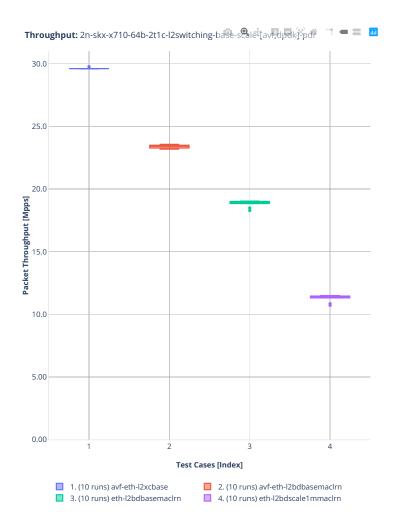

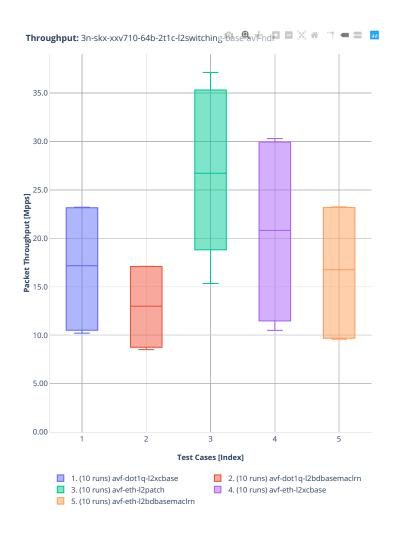

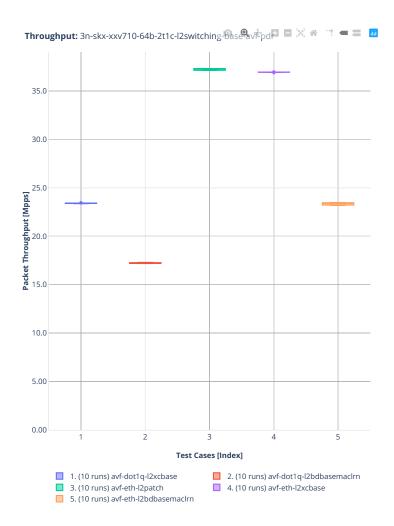

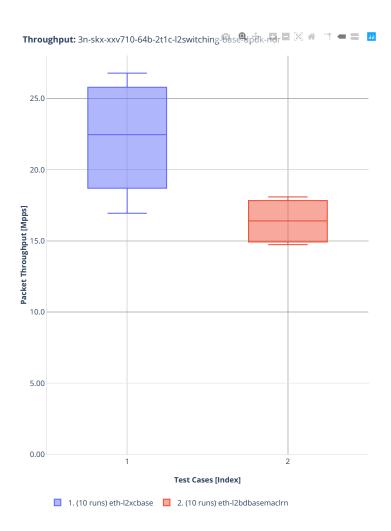

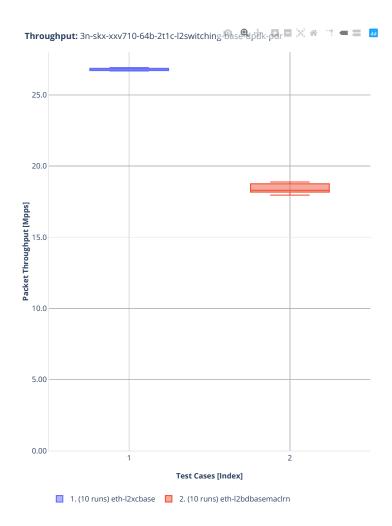

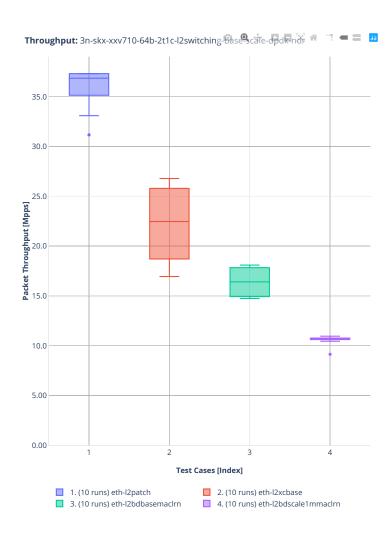

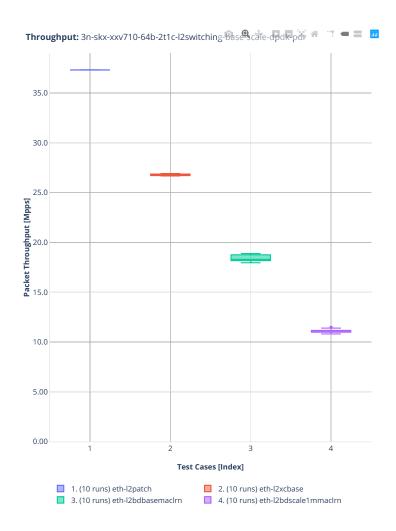

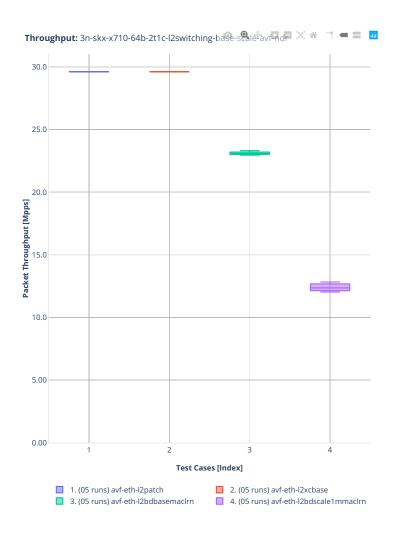

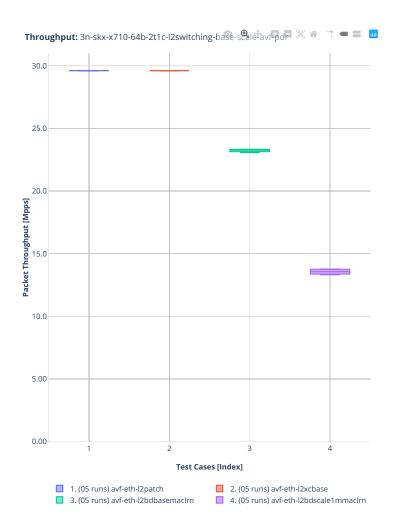

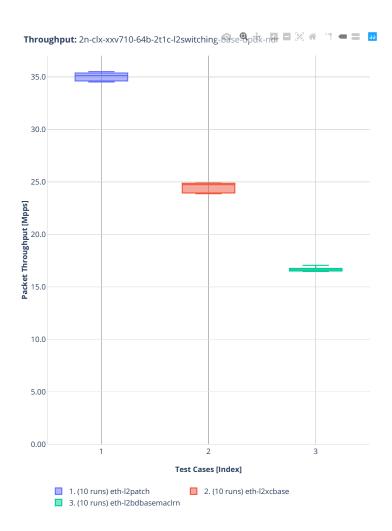

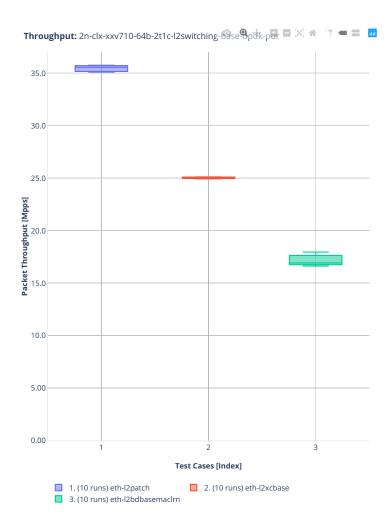

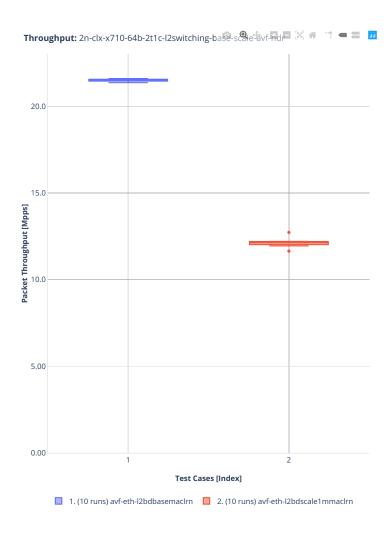

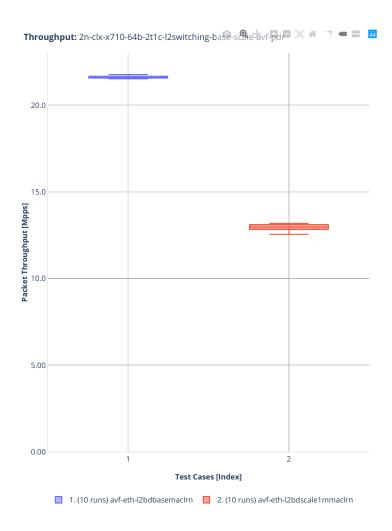

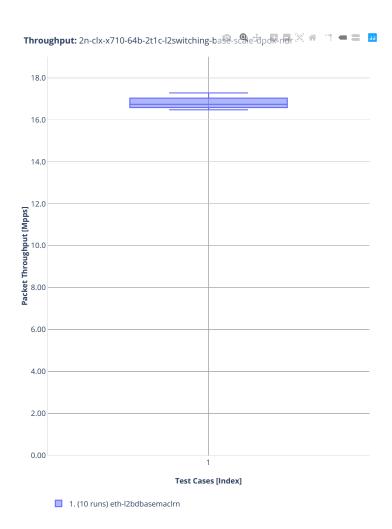

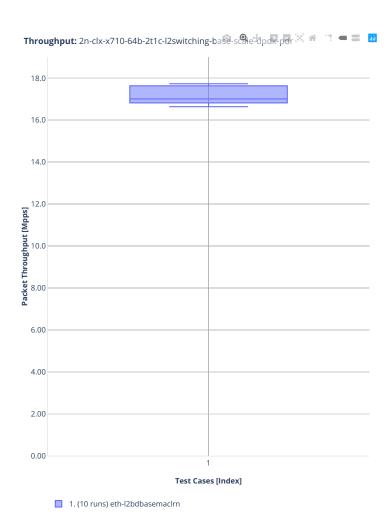

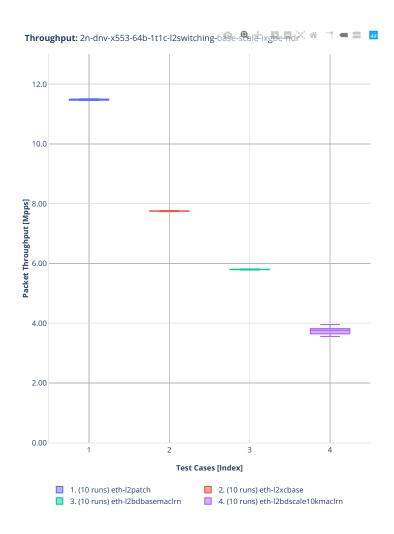

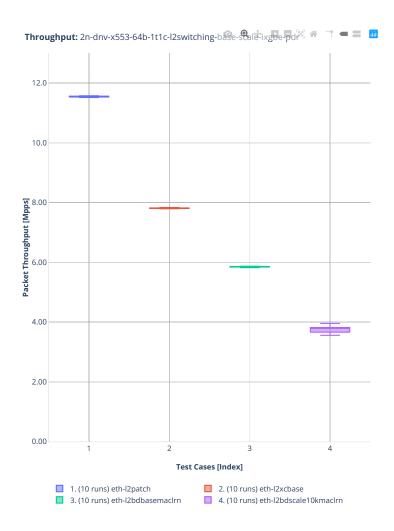

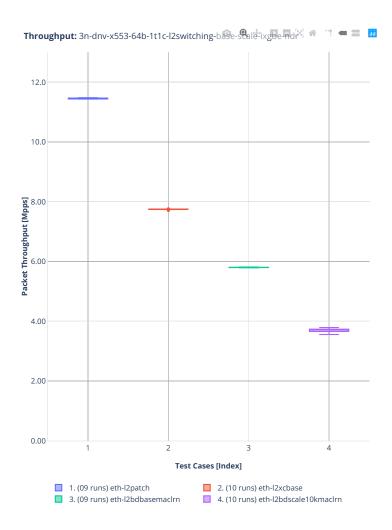

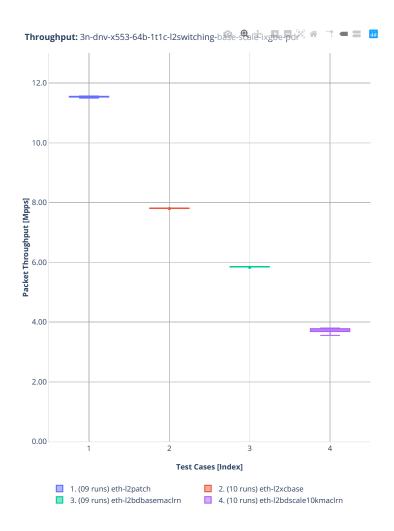

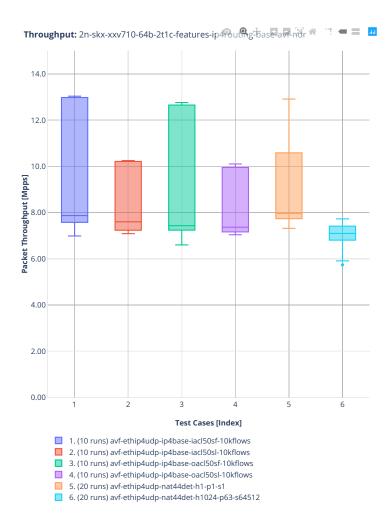

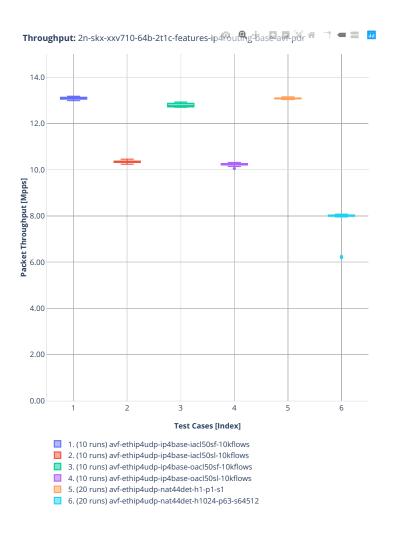

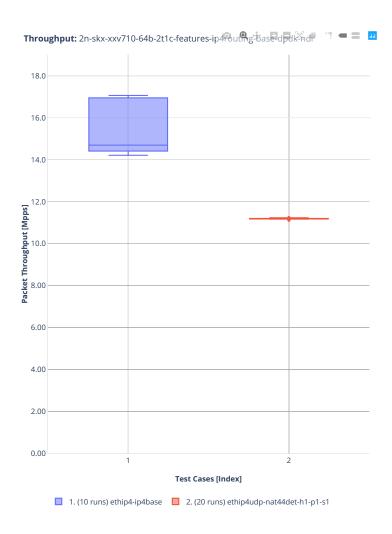

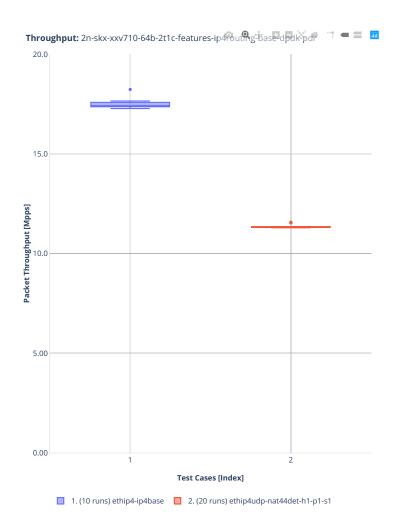

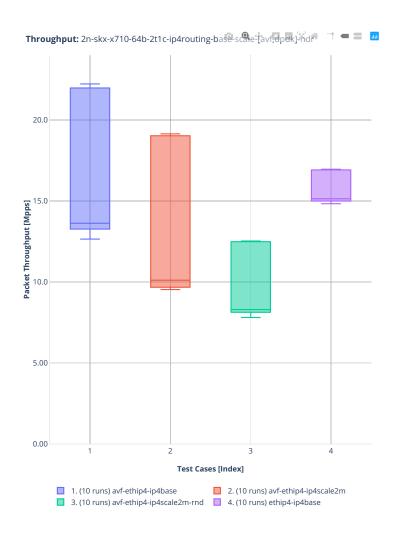

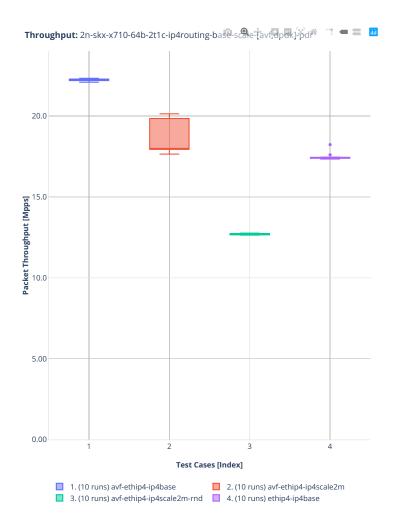

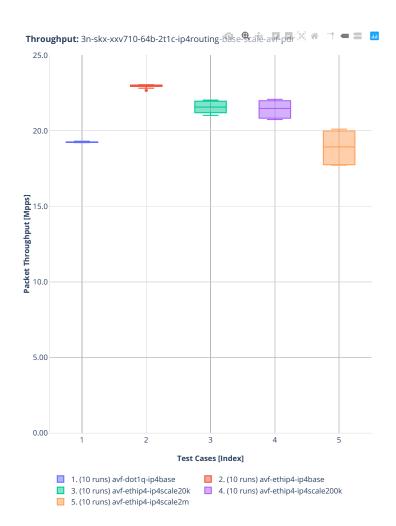

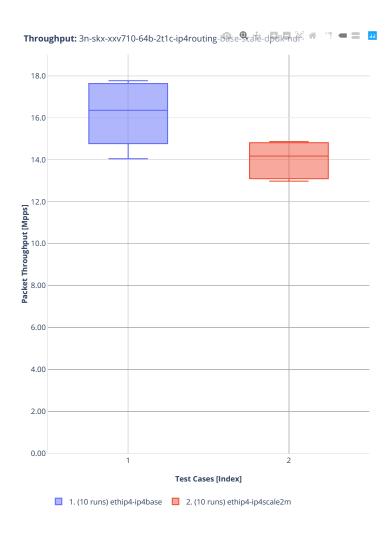

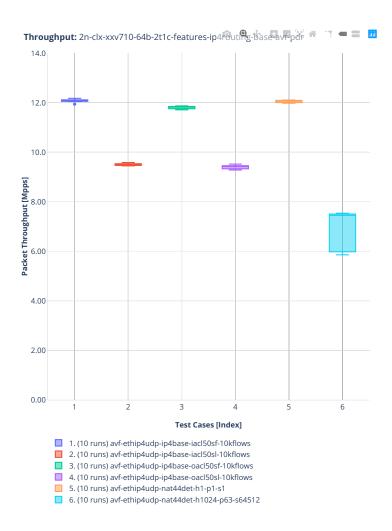

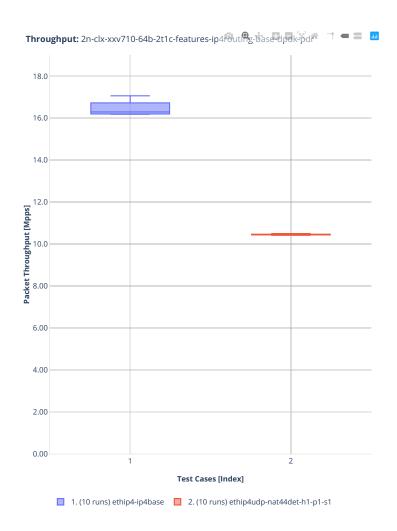

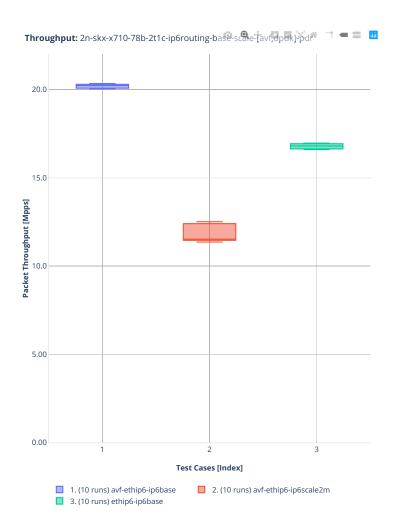

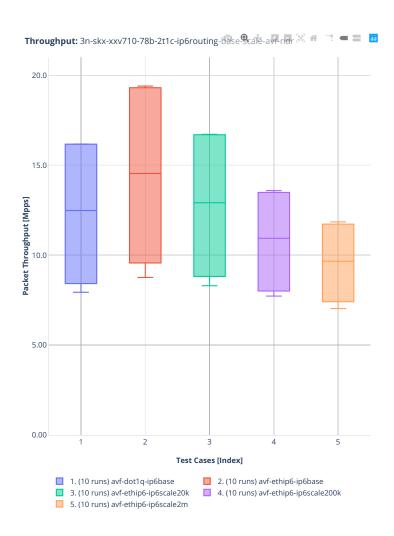

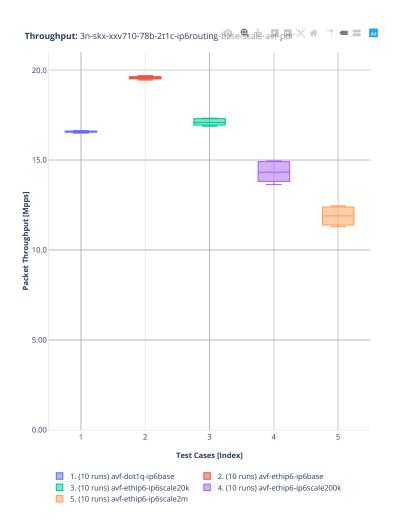

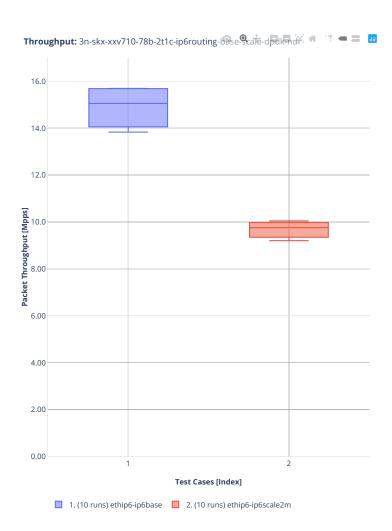

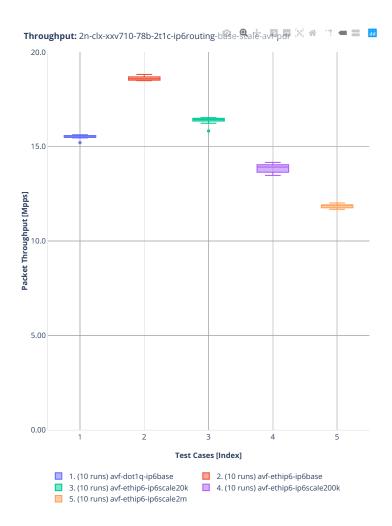

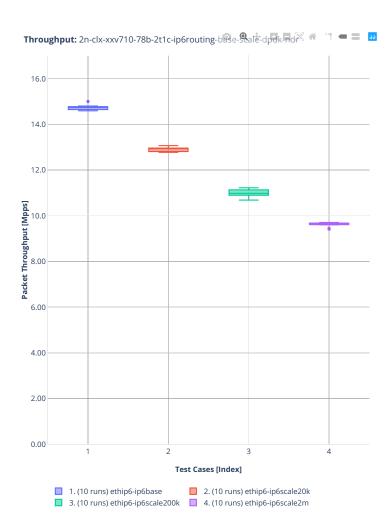

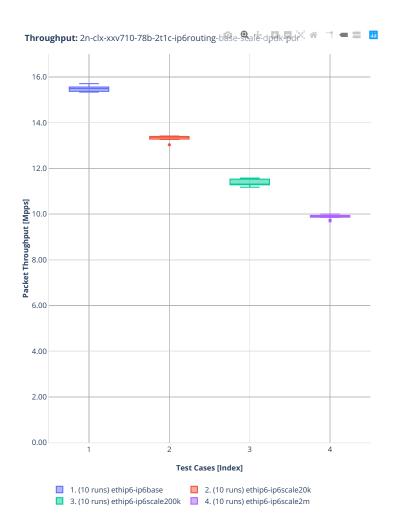

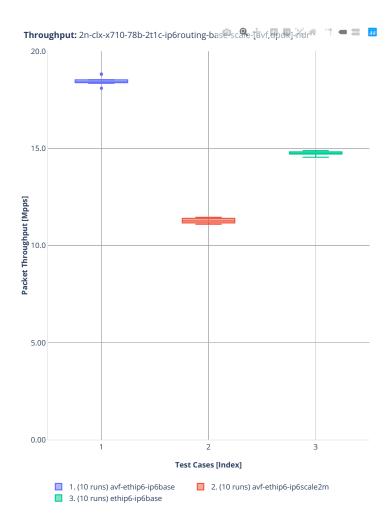

MLRsearch tests are run to discover NDR and PDR rates for each VPP and DPDK release covered by CSIT report. Results for small frame sizes (64b/78B, IMIX) are presented in packet throughput graphs (Box-and-Whisker Plots) with NDR and PDR rates plotted against the test cases covering popular VPP packet paths.

Each test is executed at least 10 times to verify measurements repeatability and results are compared between releases and test environments. NDR and PDR packet and bandwidth throughput results for all frame sizes and for all tests are presented in detailed results tables.

#### **Details**

See MLRsearch Tests (page 22) section for more detail. MLRsearch is being standardized in IETF in draft-vpolak-mkonstan-mlrsearch<sup>7</sup>.

# **MRR Tests**

#### **Description**

Maximum Receive Rate (MRR) tests are complementary to MLRsearch tests, as they provide a maximum "raw" throughput benchmark for development and testing community.

MRR tests measure the packet forwarding rate under the maximum load offered by traffic generator (dependent on link type and NIC model) over a set trial duration, regardless of packet loss. Maximum load for specified Ethernet frame size is set to the bi-directional link rate.

### **Usage**

MRR tests are much faster than MLRsearch as they rely on a single trial or a small set of trials with very short duration. It is this property that makes them suitable for continuous execution in daily performance trending jobs enabling detection of performance anomalies (regressions, progressions) resulting from data plane code changes.

MRR tests are also used for VPP per patch performance jobs verifying patch performance vs parent. CSIT reports include MRR throughput comparisons between releases and test environments. Small frame sizes only (64b/78B, IMIX).

<sup>&</sup>lt;sup>6</sup> https://tools.ietf.org/html/rfc2544.html

<sup>&</sup>lt;sup>7</sup> https://tools.ietf.org/html/draft-vpolak-mkonstan-bmwg-mlrsearch

#### **Details**

See MRR Throughput (page 23) section for more detail about MRR tests configuration.

FD.io CSIT performance dashboard includes complete description of daily performance trending tests<sup>8</sup> and VPP per patch tests<sup>9</sup>.

#### **PLRsearch Tests**

#### **Description**

Probabilistic Loss Ratio search (PLRsearch) tests discovers a packet throughput rate associated with configured Packet Loss Ratio (PLR) criteria for tests run over an extended period of time a.k.a. soak testing. PLRsearch assumes that system under test is probabilistic in nature, and not deterministic.

# **Usage**

PLRsearch are run to discover a sustained throughput for PLR=10^-7 (close to NDR) for VPP release covered by CSIT report. Results for small frame sizes (64b/78B) are presented in packet throughput graphs (Box Plots) for a small subset of baseline tests.

Each soak test lasts 30 minutes and is executed at least twice. Results are compared against NDR and PDR rates discovered with MLRsearch.

#### **Details**

See *PLRsearch* (page 24) methodology section for more detail. PLRsearch is being standardized in IETF in draft-vpolak-bmwg-plrsearch<sup>10</sup>.

#### **Generic Test Properties**

All data plane throughput test methodologies share following generic properties:

- Tested L2 frame sizes (untagged Ethernet):

- IPv4 payload: 64B, IMIX (28x64B, 16x570B, 4x1518B), 1518B, 9000B.

- IPv6 payload: 78B, IMIX (28x78B, 16x570B, 4x1518B), 1518B, 9000B.

- All quoted sizes include frame CRC, but exclude per frame transmission overhead of 20B (preamble, inter frame gap).

- Offered packet load is always bi-directional and symmetric.

- All measured and reported packet and bandwidth rates are aggregate bi-directional rates reported from external Traffic Generator perspective.

#### **MLRsearch Tests**

#### Overview

Multiple Loss Rate search (MLRsearch) tests use new search algorithm implemented in FD.io CSIT project. MLRsearch discovers multiple packet throughput rates in a single search, with each rate associated with a different Packet Loss Ratio (PLR) criteria.

<sup>&</sup>lt;sup>8</sup> https://docs.fd.io/csit/master/trending/methodology/performance\_tests.html

$<sup>^9\</sup> https://docs.fd.io/csit/master/trending/methodology/perpatch\_performance\_tests.html$

<sup>&</sup>lt;sup>10</sup> https://tools.ietf.org/html/draft-vpolak-bmwg-plrsearch

Two throughput measurements used in FD.io CSIT are Non-Drop Rate (NDR, with zero packet loss, PLR=0) and Partial Drop Rate (PDR, with packet loss rate not greater than the configured non-zero PLR).

MLRsearch discovers NDR and PDR in a single pass reducing required time duration compared to separate 'binary search'\_es for NDR and PDR. Overall search time is reduced even further by relying on shorter trial durations of intermediate steps, with only the final measurements conducted at the specified final trial duration. This results in the shorter overall execution time when compared to standard NDR/PDR binary search, while guaranteeing similar results.

If needed, next version of MLRsearch can be easily adopted to discover more throughput rates with different pre-defined PLRs.

**Note:** All throughput rates are *always* bi-directional aggregates of two equal (symmetric) uni-directional packet rates received and reported by an external traffic generator.

#### **Search Implementation**

Detailed description of the MLRsearch algorithm is included in the IETF draft draft-vpolak-mkonstan-mlrsearch<sup>11</sup> that is in the process of being standardized in the IETF Benchmarking Methodology Working Group (BMWG).

MLRsearch is also available as a PyPI (Python Package Index) library<sup>12</sup>.

#### **Implementation Deviations**

FD.io CSIT implementation of MLRsearch so far is fully based on the -02 version of the draft-vpolak-mkonstan-mlrsearch-02<sup>13</sup>.

#### **MRR Throughput**

Maximum Receive Rate (MRR) tests are complementary to MLRsearch tests, as they provide a maximum "raw" throughput benchmark for development and testing community. MRR tests measure the packet forwarding rate under the maximum load offered by traffic generator over a set trial duration, regardless of packet loss.

MRR tests are currently used for following test jobs:

- Report performance comparison: 64B, IMIX for vhost, memif.

- Daily performance trending: 64B, IMIX for vhost, memif.

- Per-patch performance verification: 64B.

- Initial iterations of MLRsearch and PLRsearch: 64B.

Maximum offered load for specific L2 Ethernet frame size is set to either the maximum bi-directional link rate or tested NIC model capacity, as follows:

- For 10GE NICs the maximum packet rate load is 2x14.88 Mpps for 64B, a 10GE bi-directional link rate.

- For 25GE NICs the maximum packet rate load is 2x18.75 Mpps for 64B, a 25GE bi-directional link sub-rate limited by 25GE NIC used on TRex TG, XXV710.

- For 40GE NICs the maximum packet rate load is 2x18.75 Mpps for 64B, a 40GE bi-directional link sub-rate limited by 40GE NIC used on TRex TG,XL710. Packet rate for other tested frame sizes is limited by PCleGen3 x8 bandwidth limitation of ~50Gbps.

$<sup>^{11}\ \</sup>text{https://tools.ietf.org/html/draft-vpolak-mkonstan-bmwg-mlrsearch}$

<sup>12</sup> https://pypi.org/project/MLRsearch/

<sup>&</sup>lt;sup>13</sup> https://tools.ietf.org/html/draft-vpolak-mkonstan-bmwg-mlrsearch-02

MRR test code implements multiple bursts of offered packet load and has two configurable burst parameters: individual trial duration and number of trials in a single burst. This enables more precise performance trending by providing more results data for analysis.

Burst parameter settings vary between different tests using MRR:

- MRR individual trial duration:

- Report performance comparison: 1 sec.

- Daily performance trending: 1 sec.

- Per-patch performance verification: 10 sec.

- Initial iteration for MLRsearch: 1 sec.

- Initial iteration for PLRsearch: 5.2 sec.

- Number of MRR trials per burst:

- Report performance comparison: 10.

- Daily performance trending: 10.

- Per-patch performance verification: 5.

- Initial iteration for MLRsearch: 1.

- Initial iteration for PLRsearch: 1.

#### **PLRsearch**

#### Motivation for PLRsearch

Network providers are interested in throughput a system can sustain.

RFC 2544<sup>14</sup> assumes loss ratio is given by a deterministic function of offered load. But NFV software systems are not deterministic enough. This makes deterministic algorithms (such as binary search<sup>15</sup> per RFC 2544 and MLRsearch with single trial) to return results, which when repeated show relatively high standard deviation, thus making it harder to tell what "the throughput" actually is.

We need another algorithm, which takes this indeterminism into account.

#### **Generic Algorithm**

Detailed description of the PLRsearch algorithm is included in the IETF draft draft-vpolak-bmwg-plrsearch-02<sup>16</sup> that is in the process of being standardized in the IETF Benchmarking Methodology Working Group (BMWG).

#### **Terms**

The rest of this page assumes the reader is familiar with the following terms defined in the IETF draft:

- Trial Order Independent System

- Duration Independent System

- Target Loss Ratio

- Critical Load

- · Offered Load regions

<sup>14</sup> https://tools.ietf.org/html/rfc2544

<sup>&</sup>lt;sup>15</sup> https://en.wikipedia.org/wiki/Binary\_search\_algorithm

<sup>&</sup>lt;sup>16</sup> https://tools.ietf.org/html/draft-vpolak-bmwg-plrsearch-02

- Zero Loss Region

- Non-Deterministic Region

- Guaranteed Loss Region

- Fitting Function

- Stretch Function

- Erf Function

- Bayesian Inference

- Prior distribution

- Posterior Distribution

- Numeric Integration

- Monte Carlo

- Importance Sampling

#### **FD.io CSIT Implementation Specifics**

The search receives min\_rate and max\_rate values, to avoid measurements at offered loads not supported by the traffic generator.

The implemented tests cases use bidirectional traffic. The algorithm stores each rate as bidirectional rate (internally, the algorithm is agnostic to flows and directions, it only cares about aggregate counts of packets sent and packets lost), but debug output from traffic generator lists unidirectional values.

In a sample implemenation in FD.io CSIT project, there is roughly 0.5 second delay between trials due to restrictons imposed by packet traffic generator in use (T-Rex).

As measurements results come in, posterior distribution computation takes more time (per sample), although there is a considerable constant part (mostly for inverting the fitting functions).

Also, the integrator needs a fair amount of samples to reach the region the posterior distribution is concentrated at.

And of course, the speed of the integrator depends on computing power of the CPU the algorithm is able to use

All those timing related effects are addressed by arithmetically increasing trial durations with configurable coefficients (currently 5.1 seconds for the first trial, each subsequent trial being 0.1 second longer).

In order to avoid them, the current implementation tracks natural logarithm (instead of the original quantity) for any quantity which is never negative. Logarithm of zero is minus infinity (not supported by Python), so special value "None" is used instead. Specific functions for frequent operations (such as "logarithm of sum of exponentials") are defined to handle None correctly.

Current implementation uses two fitting functions, called "stretch" and "erf". In general, their estimates for critical rate differ, which adds a simple source of systematic error, on top of randomness error reported by integrator. Otherwise the reported stdev of critical rate estimate is unrealistically low.

Both functions are not only increasing, but also convex (meaning the rate of increase is also increasing).

Both fitting functions have several mathematically equivalent formulas, each can lead to an arithmetic overflow or underflow in different sub-terms. Overflows can be eliminated by using different exact formulas for different argument ranges. Underflows can be avoided by using approximate formulas in affected argument ranges, such ranges have their own formulas to compute. At the end, both fitting function implementations contain multiple "if" branches, discontinuities are a possibility at range boundaries.

The numeric integrator expects all the parameters to be distributed (independently and) uniformly on an interval (-1, 1).

As both "mrr" and "spread" parameters are positive and not dimensionless, a transformation is needed. Dimentionality is inherited from max\_rate value.

The "mrr" parameter follows a Lomax distribution<sup>17</sup> with alpha equal to one, but shifted so that mrr is always greater than 1 packet per second.

The "stretch" parameter is generated simply as the "mrr" value raised to a random power between zero and one; thus it follows a reciprocal distribution 18.

After few measurements, the posterior distribution of fitting function arguments gets quite concentrated into a small area. The integrator is using Monte Carlo<sup>19</sup> with importance sampling<sup>20</sup> where the biased distribution is bivariate Gaussian<sup>21</sup> distribution, with deliberately larger variance. If the generated sample falls outside (-1, 1) interval, another sample is generated.

The center and the covariance matrix for the biased distribution is based on the first and second moments of samples seen so far (within the computation). The center is used directly, covariance matrix is scaled up by a heurictic constant (8.0 by default). The following additional features are applied designed to avoid hyper-focused distributions.

Each computation starts with the biased distribution inherited from the previous computation (zero point and unit covariance matrix is used in the first computation), but the overal weight of the data is set to the weight of the first sample of the computation. Also, the center is set to the first sample point. When additional samples come, their weight (including the importance correction) is compared to sum of the weights of data seen so far (within the iteration). If the new sample is more than one e-fold more impactful, both weight values (for data so far and for the new sample) are set to (geometric) average of the two weights.

This combination showed the best behavior, as the integrator usually follows two phases. First phase (where inherited biased distribution or single big sample are dominating) is mainly important for locating the new area the posterior distribution is concentrated at. The second phase (dominated by whole sample population) is actually relevant for the critical rate estimation.

First two measurements are hardcoded to happen at the middle of rate interval and at max\_rate. Next two measurements follow MRR-like logic, offered load is decreased so that it would reach target loss ratio if offered load decrease lead to equal decrease of loss rate.

The rest of measurements start directly in between erf and stretch estimate average. There is one workaround implemented, aimed at reducing the number of consequent zero loss measurements (per fitting function). The workaround first stores every measurement result which loss ratio was the targed loss ratio or higher. Sorted list (called lossy loads) of such results is maintained.

When a sequence of one or more zero loss measurement results is encountered, a smallest of lossy loads is drained from the list. If the estimate average is smaller than the drained value, a weighted average of this estimate and the drained value is used as the next offered load. The weight of the estimate decreases exponentially with the length of consecutive zero loss results.

This behavior helps the algorithm with convergence speed, as it does not need so many zero loss result to get near critical region. Using the smallest (not drained yet) of lossy loads makes it sure the new offered load is unlikely to result in big loss region. Draining even if the estimate is large enough helps to discard early measurements when loss hapened at too low offered load. Current implementation adds 4 copies of lossy loads and drains 3 of them, which leads to fairly stable behavior even for somewhat inconsistent SUTs.

As high loss count measurements add many bits of information, they need a large amount of small loss count measurements to balance them, making the algorithm converge quite slowly. Typically, this happens when few initial measurements suggest spread way bigger then later measurements. The workaround in offered load selection helps, but more intelligent workarounds could get faster convergence still.

<sup>&</sup>lt;sup>17</sup> https://en.wikipedia.org/wiki/Lomax\_distribution

<sup>&</sup>lt;sup>18</sup> https://en.wikipedia.org/wiki/Reciprocal\_distribution

<sup>&</sup>lt;sup>19</sup> https://en.wikipedia.org/wiki/Monte\_Carlo\_integration

<sup>&</sup>lt;sup>20</sup> https://en.wikipedia.org/wiki/Importance\_sampling

<sup>&</sup>lt;sup>21</sup> https://en.wikipedia.org/wiki/Multivariate\_normal\_distribution

Some systems evidently do not follow the assumption of repeated measurements having the same average loss rate (when the offered load is the same). The idea of estimating the trend is not implemented at all, as the observed trends have varied characteristics.

Probably, using a more realistic fitting functions will give better estimates than trend analysis.

#### **Bottom Line**

The notion of Throughput is easy to grasp, but it is harder to measure with any accuracy for non-deterministic systems.

Even though the notion of critical rate is harder to grasp than the notion of throughput, it is easier to measure using probabilistic methods.

In testing, the difference between throughput measurements and critical rate measurements is usually small, see soak vs ndr comparison.

In pactice, rules of thumb such as "send at max 95% of purported throughput" are common. The correct benchmarking analysis should ask "Which notion is 95% of throughput an approximation to?" before attempting to answer "Is 95% of critical rate safe enough?".

#### **Algorithmic Analysis**

While the estimation computation is based on hard probability science; the offered load selection part of PLRsearch logic is pure heuristics, motivated by what would a human do based on measurement and computation results.

The quality of any heuristic is not affected by soundness of its motivation, just by its ability to achieve the intended goals. In case of offered load selection, the goal is to help the search to converge to the long duration estimates sooner.

But even those long duration estimates could still be of poor quality. Even though the estimate computation is Bayesian (so it is the best it could be within the applied assumptions), it can still of poor quality when compared to what a human would estimate.

One possible source of poor quality is the randomnes inherently present in Monte Carlo numeric integration, but that can be supressed by tweaking the time related input parameters.

The most likely source of poor quality then are the assumptions. Most importantly, the number and the shape of fitting functions; but also others, such as trial order independence and duration independence.

The result can have poor quality in basically two ways. One way is related to location. Both upper and lower bounds can be overestimates or underestimates, meaning the entire estimated interval between lower bound and upper bound lays above or below (respectively) of human-estimated interval. The other way is related to the estimation interval width. The interval can be too wide or too narrow, compared to human estimation.

An estimate from a particular fitting function can be classified as an overestimate (or underestimate) just by looking at time evolution (without human examining measurement results). Overestimates decrease by time, underestimates increase by time (assuming the system performance stays constant).

Quality of the width of the estimation interval needs human evaluation, and is unrelated to both rate of narrowing (both good and bad estimate intervals get narrower at approximately the same relative rate) and relatative width (depends heavily on the system being tested).

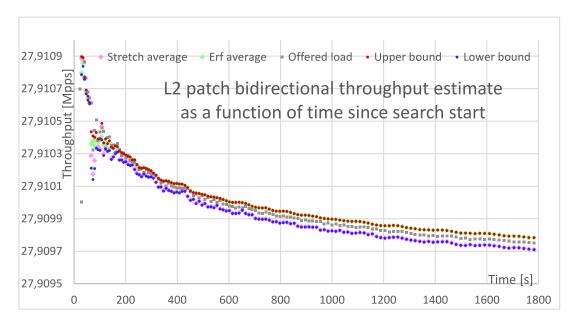

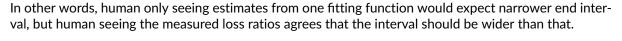

The following pictures show the upper (red) and lower (blue) bound, as well as average of Stretch (pink) and Erf (light green) estimate, and offered load chosen (grey), as computed by PLRsearch, after each trial measurement within the 30 minute duration of a test run.

Both graphs are focusing on later estimates. Estimates computed from few initial measurements are wildly off the y-axis range shown.

The following analysis will rely on frequency of zero loss measurements and magnitude of loss ratio if nonzero.

The offered load selection strategy used implies zero loss measurements can be gleaned from the graph by looking at offered load points. When the points move up farther from lower estimate, it means the previous measurement had zero loss. After non-zero loss, the offered load starts again right between (the previous values of) the estimate curves.

The very big loss ratio results are visible as noticeable jumps of both estimates downwards. Medium and small loss ratios are much harder to distinguish just by looking at the estimate curves, the analysis is based on raw loss ratio measurement results.

The following descriptions should explain why the graphs seem to signal low quality estimate at first sight, but a more detailed look reveals the quality is good (considering the measurement results).

#### L2 patch

Both fitting functions give similar estimates, the graph shows "stochasticity" of measurements (estimates increase and decrease within small time regions), and an overall trend of decreasing estimates.

On the first look, the final interval looks fairly narrow, especially compared to the region the estimates have travelled during the search. But the look at the frequency of zero loss results shows this is not a case of overestimation. Measurements at around the same offered load have higher probability of zero loss earlier (when performed farther from upper bound), but smaller probability later (when performed closer to upper bound). That means it is the performance of the system under test that decreases (slightly) over time.

With that in mind, the apparent narrowness of the interval is not a sign of low quality, just a consequence of PLRsearch assuming the performance stays constant.

#### Vhost

This test case shows what looks like a quite broad estimation interval, compared to other test cases with similarly looking zero loss frequencies. Notable features are infrequent high-loss measurement results causing big drops of estimates, and lack of long-term convergence.

Any convergence in medium-sized intervals (during zero loss results) is reverted by the big loss results, as they happen quite far from the critical load estimates, and the two fitting functions extrapolate differently.

#### **Summary**

The two graphs show the behavior of PLRsearch algorithm applied to soaking test when some of PLRsearch assumptions do not hold:

- L2 patch measurement results violate the assumption of performance not changing over time.

- Vhost measurement results violate the assumption of Poisson distribution matching the loss counts.

The reported upper and lower bounds can have distance larger or smaller than a first look by a human would expect, but a more closer look reveals the quality is good, considering the circumstances.

The usefullness of the critical load estimate is of questionable value when the assumptions are violated.

Some improvements can be made via more specific workarounds, for example long term limit of L2 patch performance could be estmated by some heuristic.

Other improvements can be achieved only by asking users whether loss patterns matter. Is it better to have single digit losses distributed fairly evenly over time (as Poisson distribution would suggest), or is it better to have short periods of medium losses mixed with long periods of zero losses (as happens in Vhost test) with the same overall loss ratio?

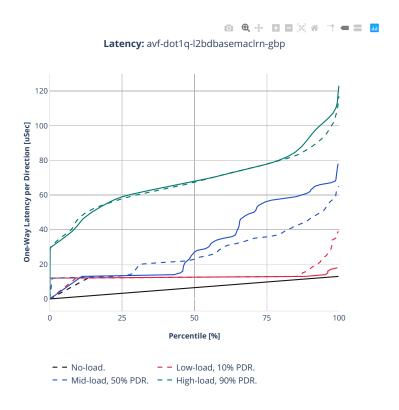

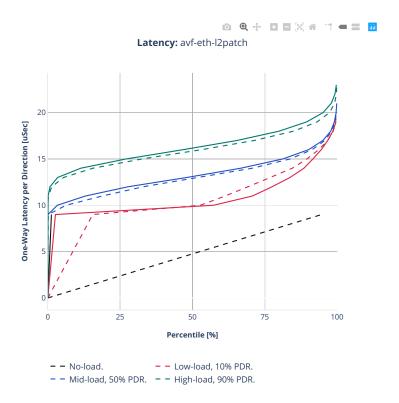

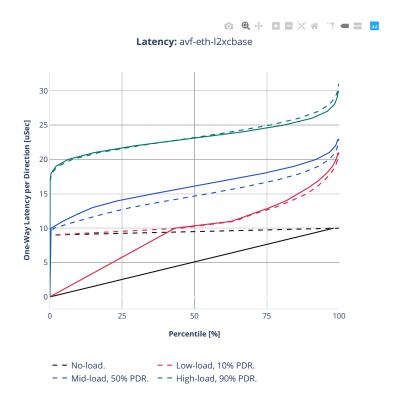

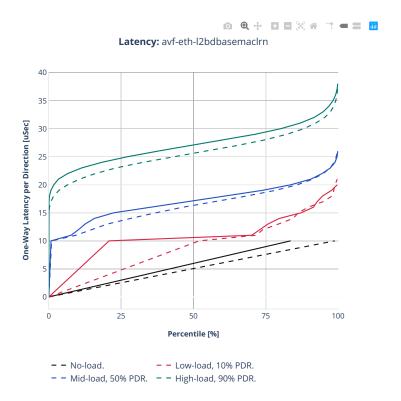

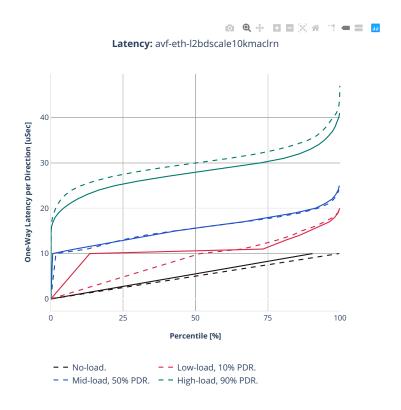

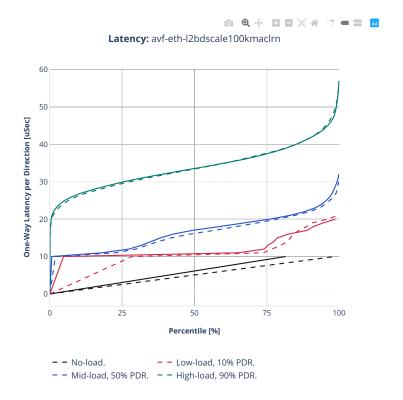

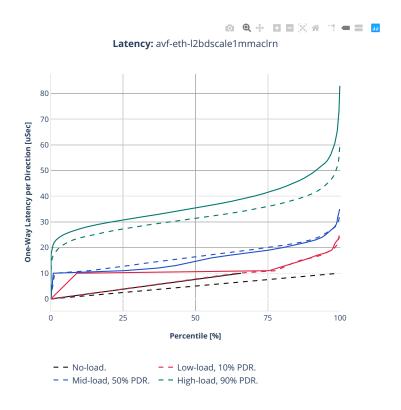

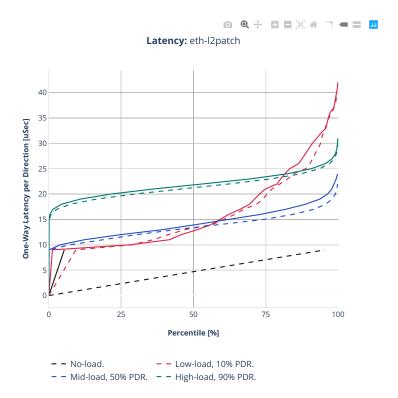

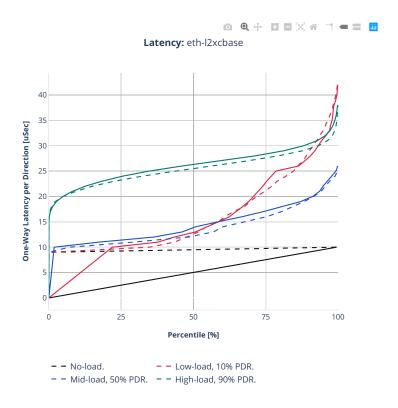

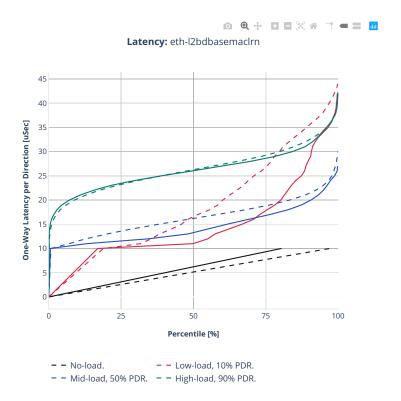

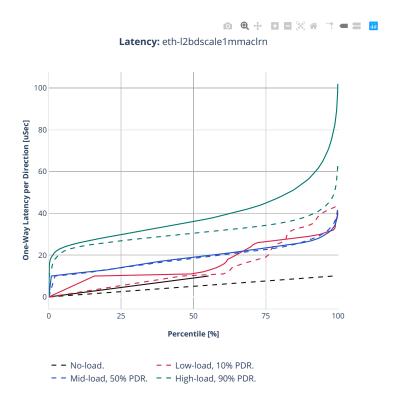

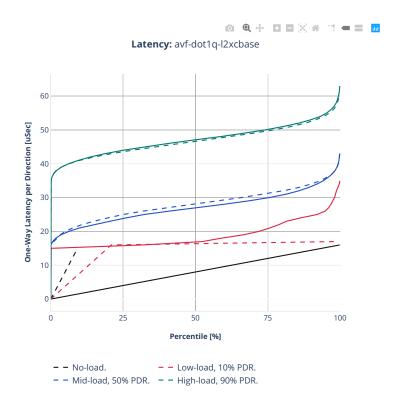

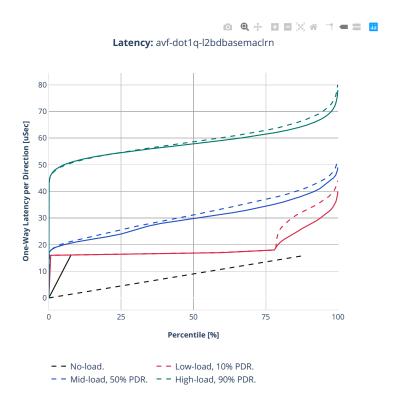

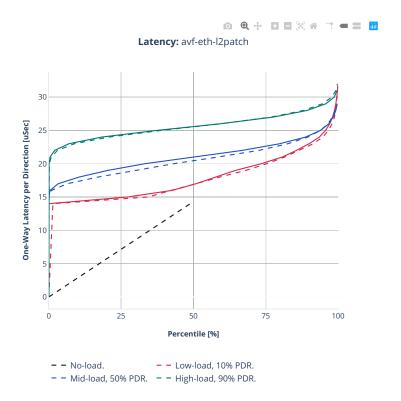

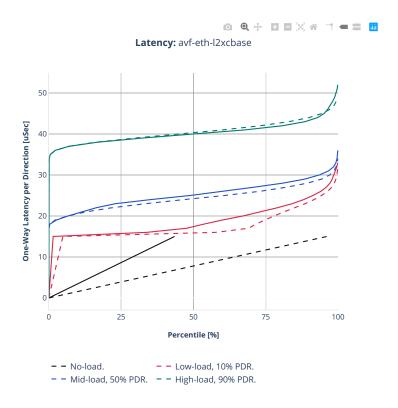

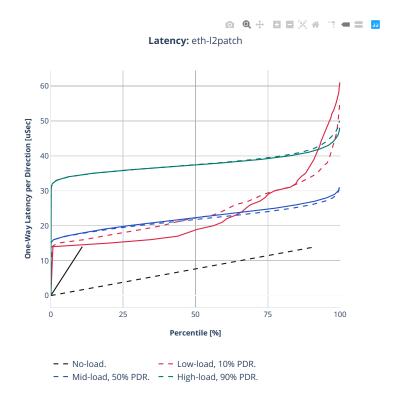

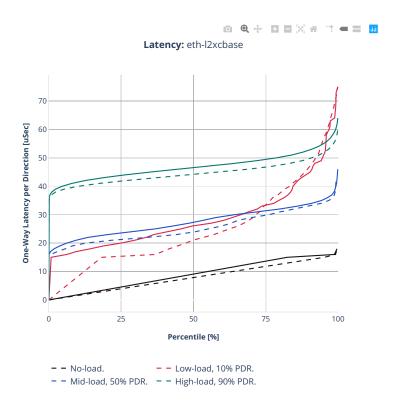

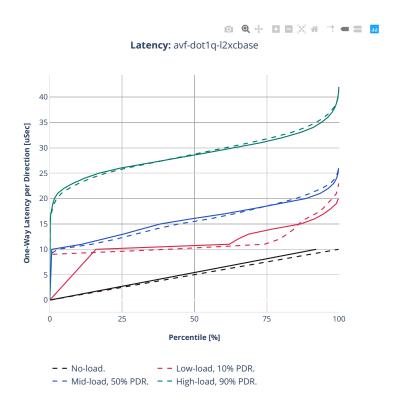

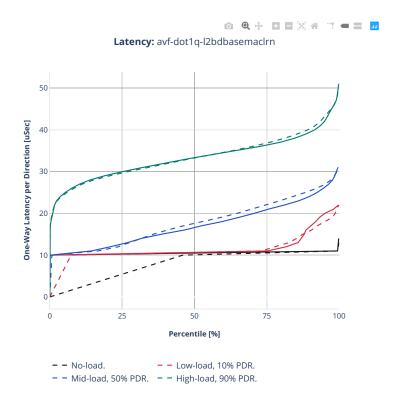

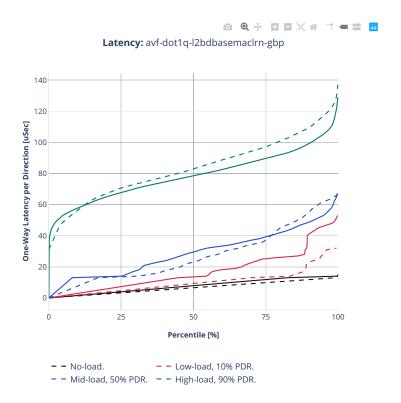

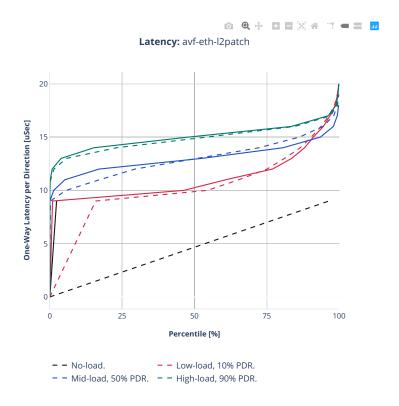

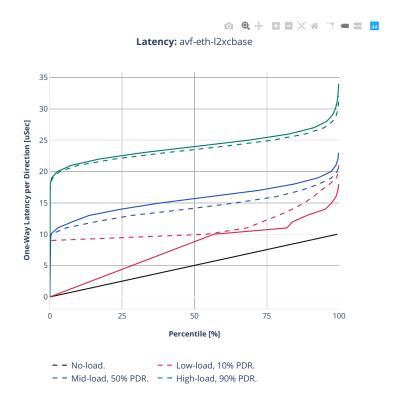

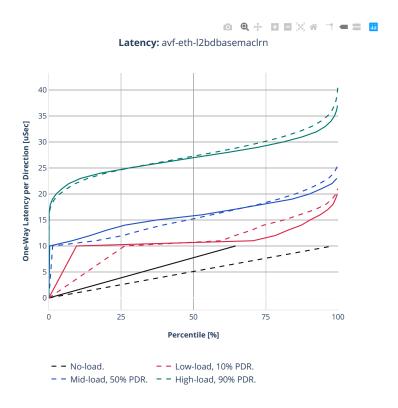

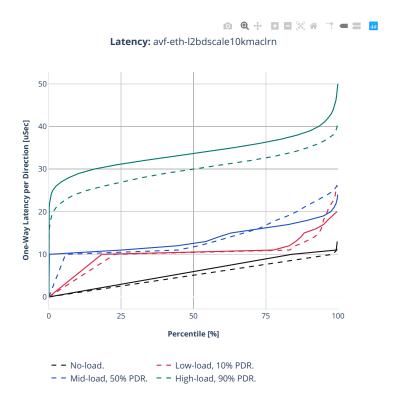

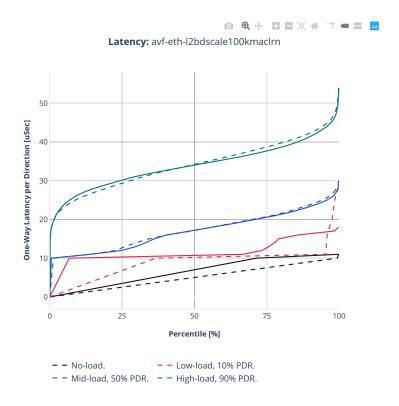

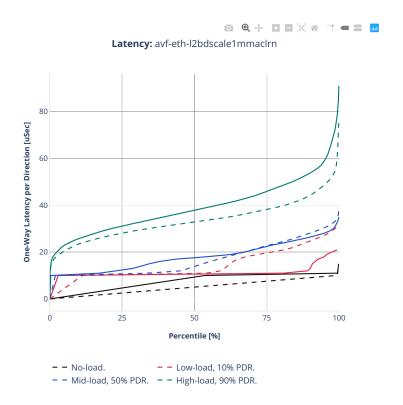

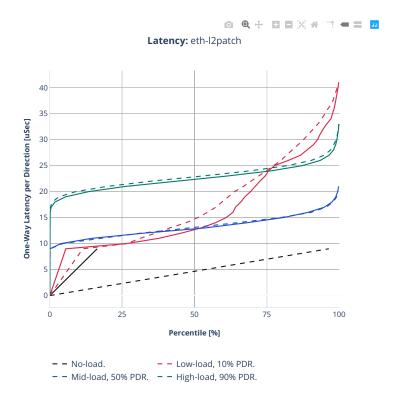

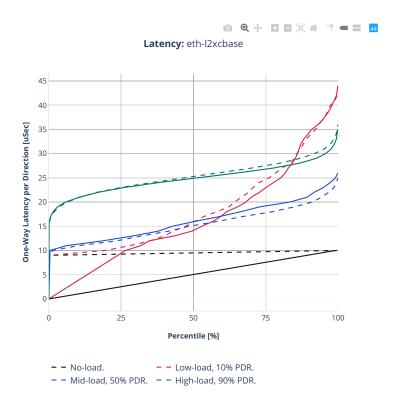

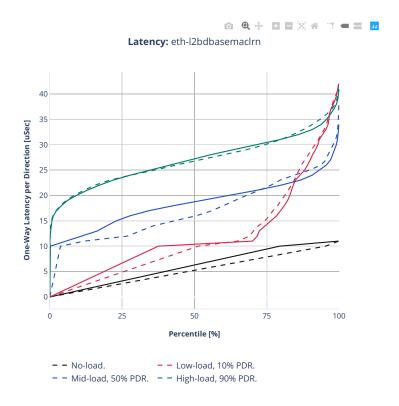

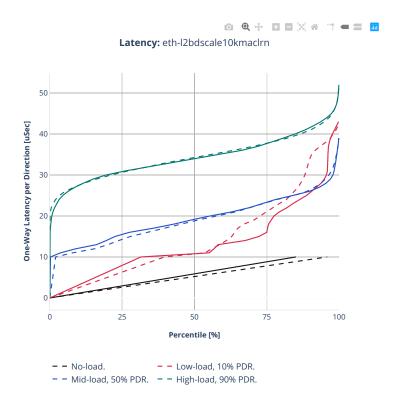

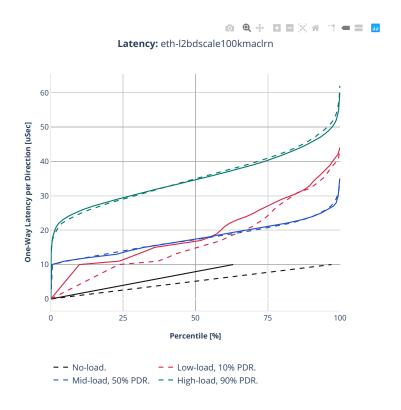

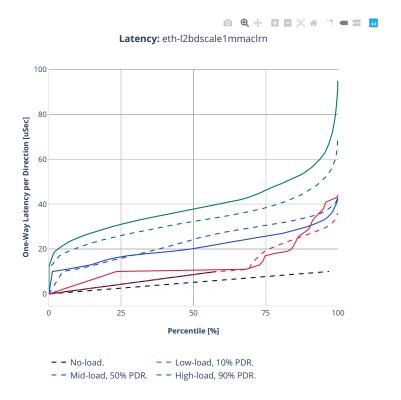

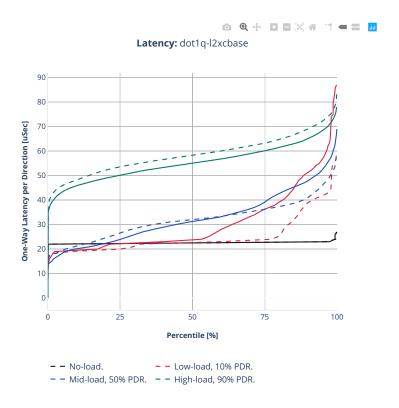

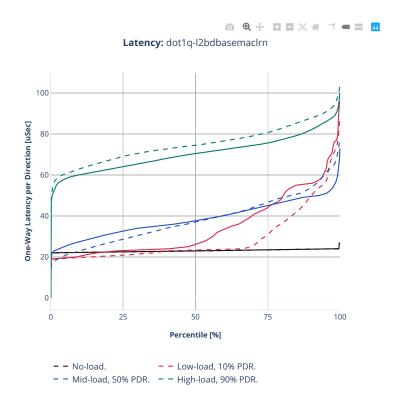

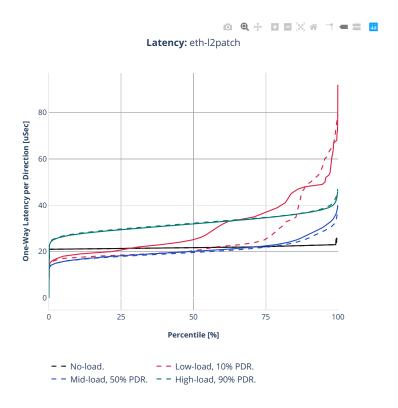

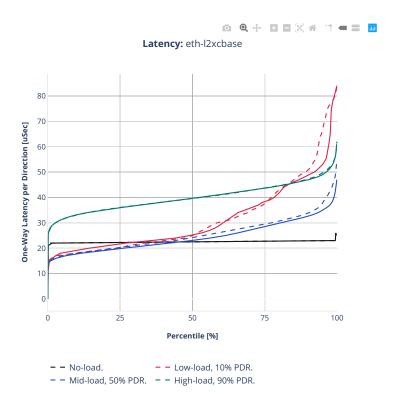

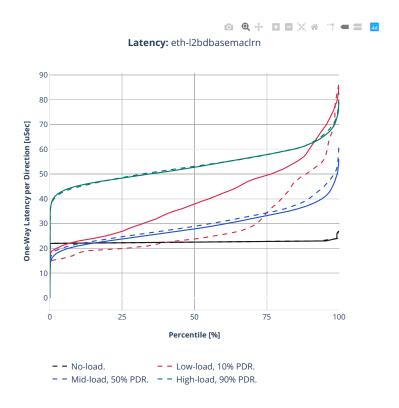

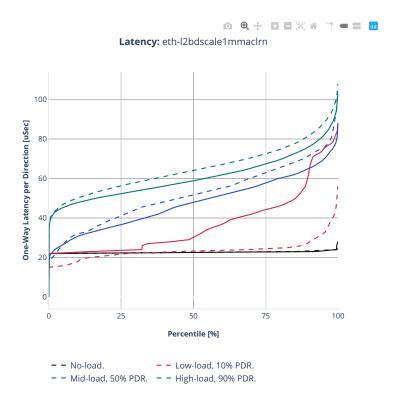

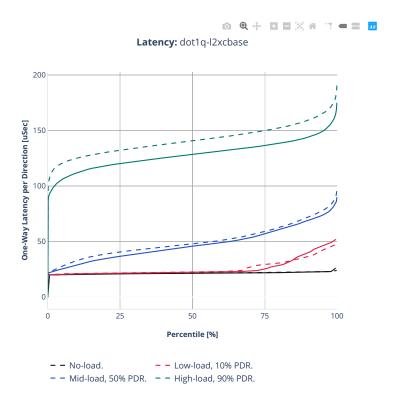

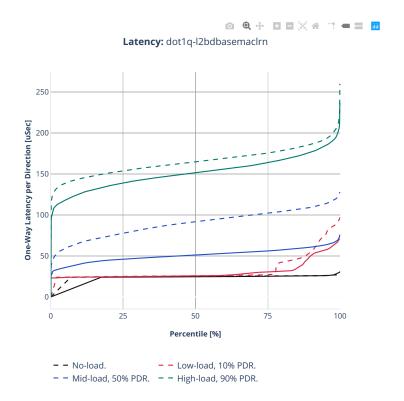

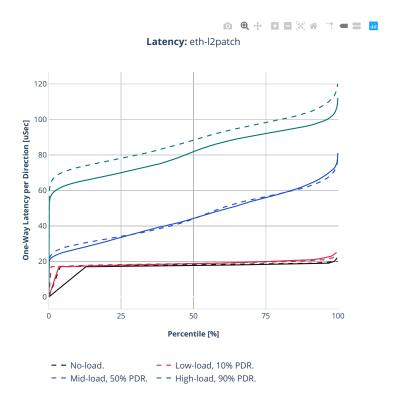

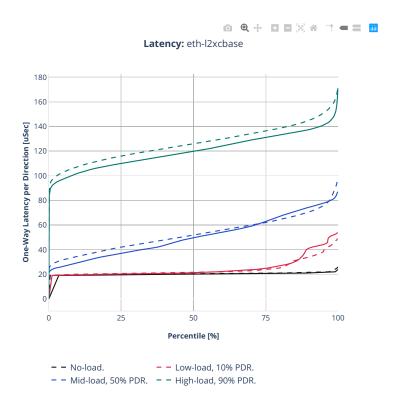

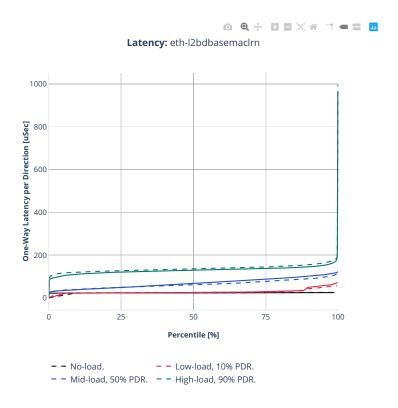

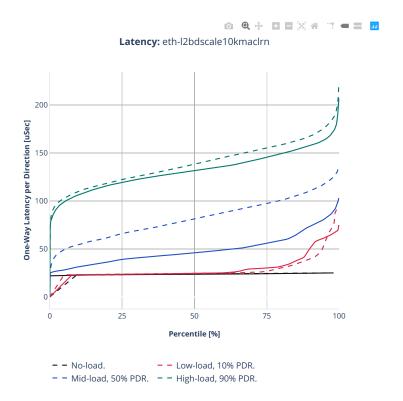

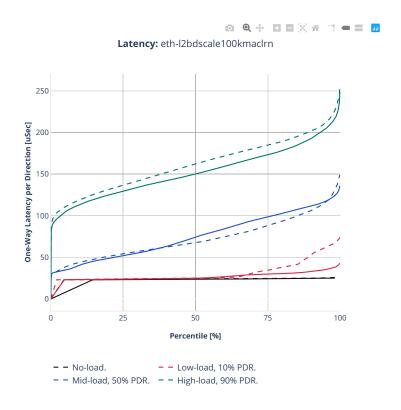

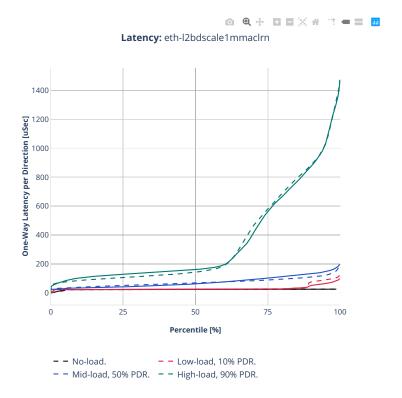

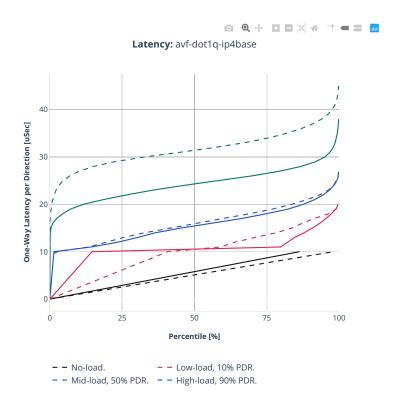

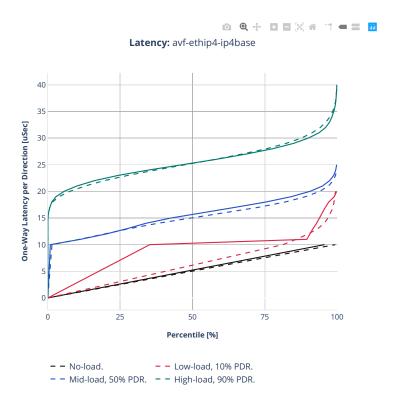

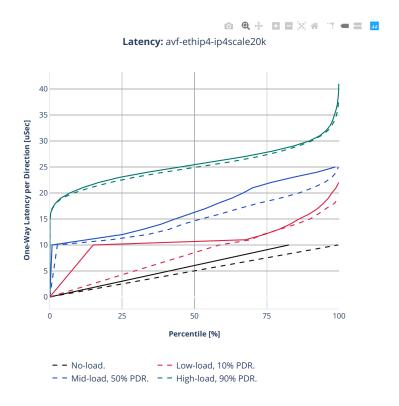

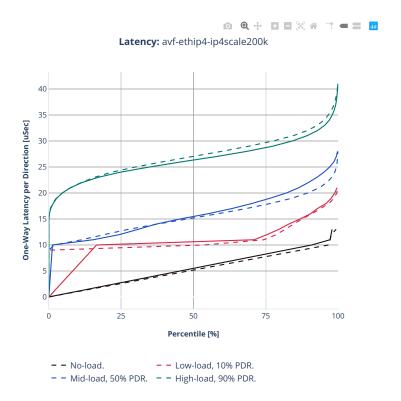

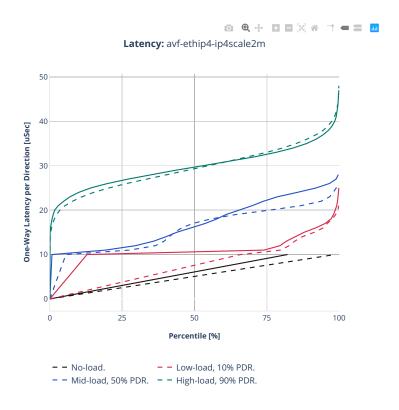

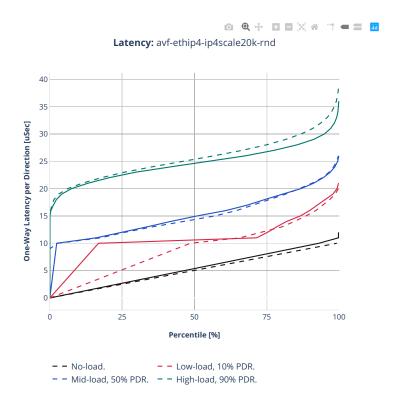

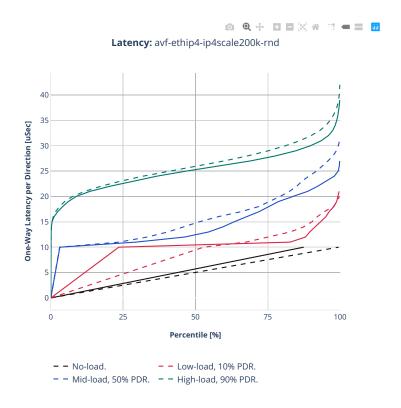

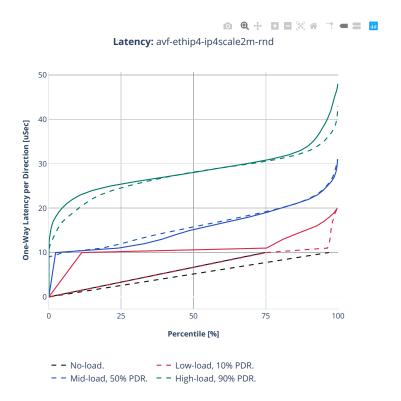

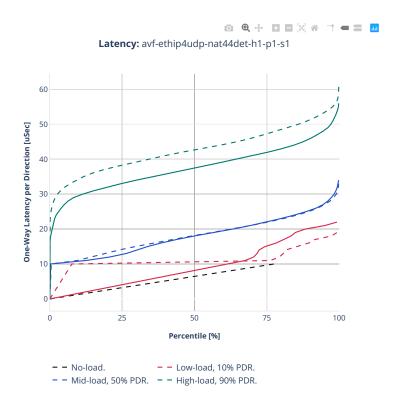

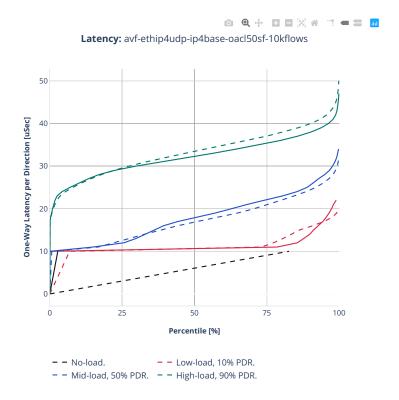

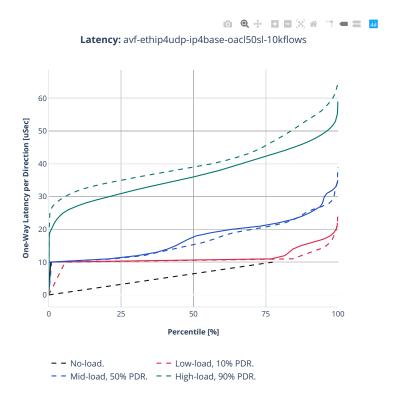

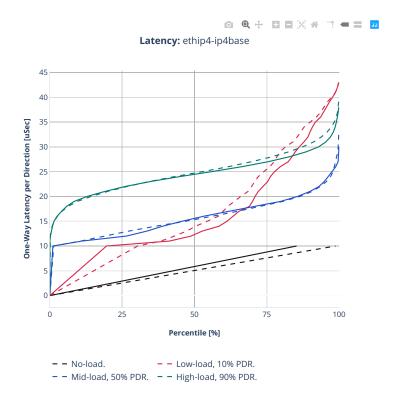

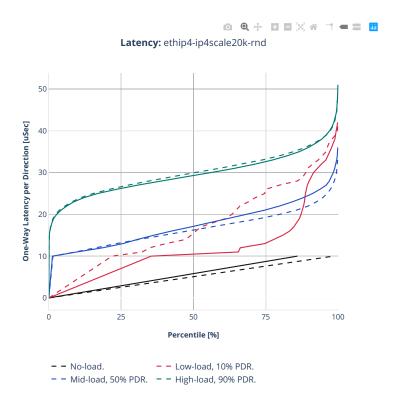

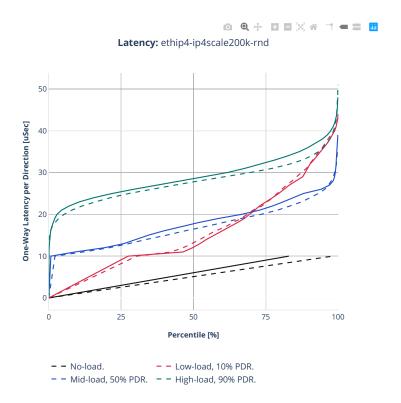

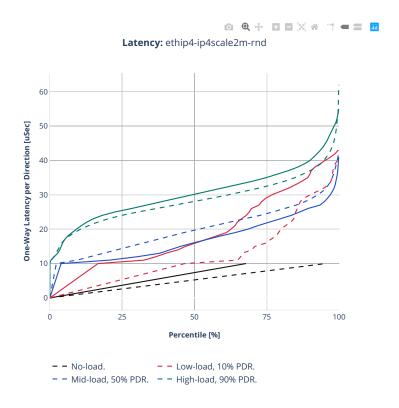

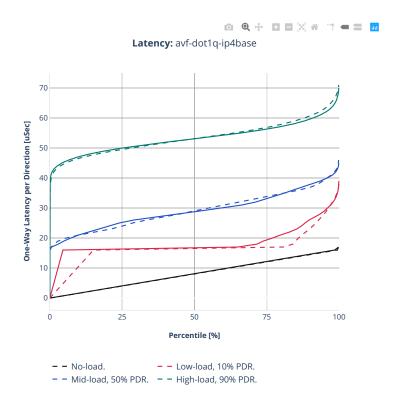

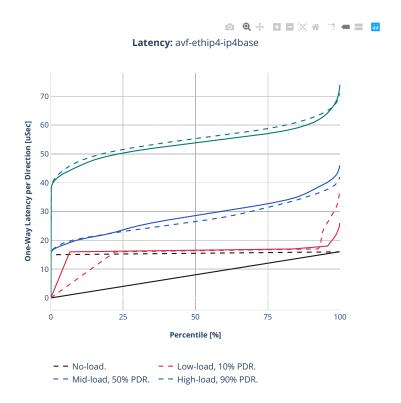

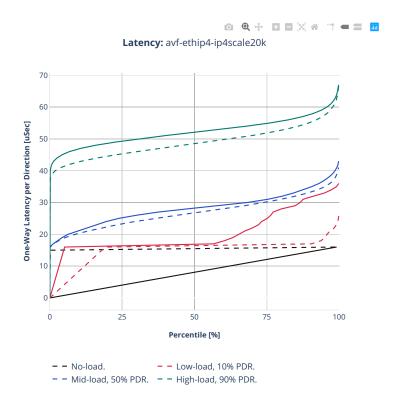

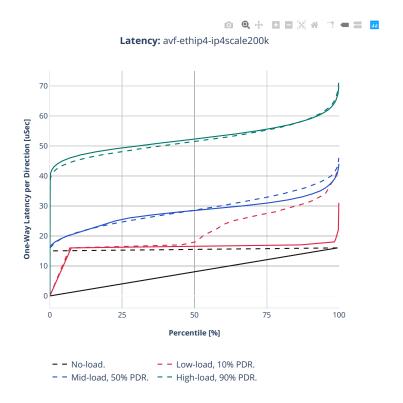

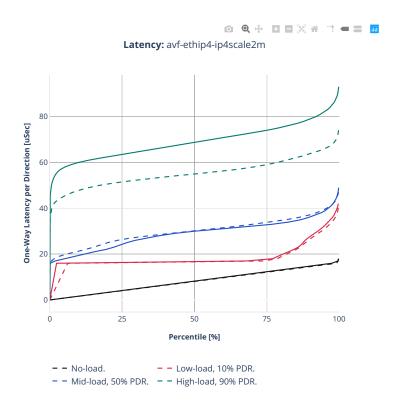

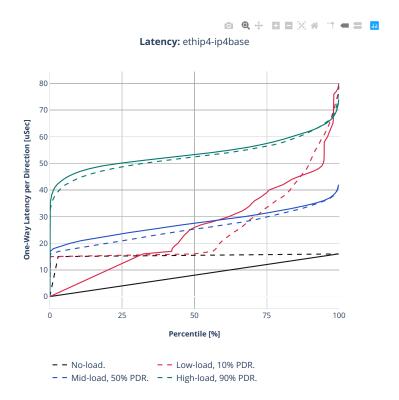

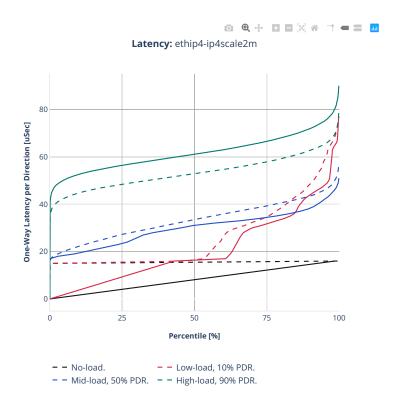

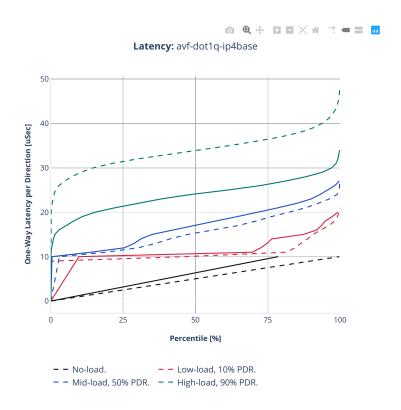

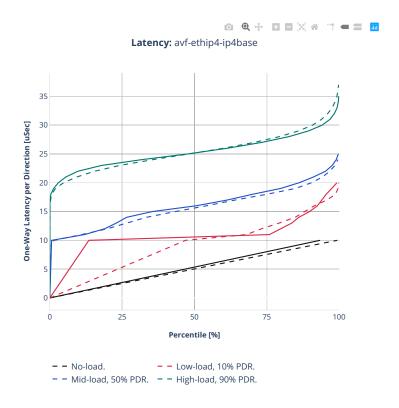

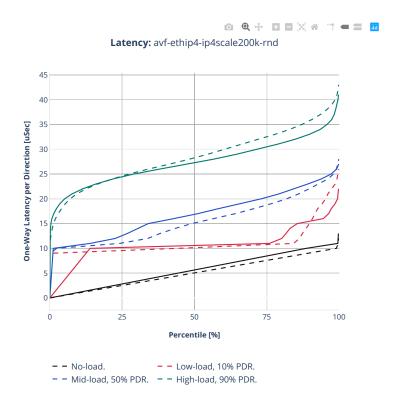

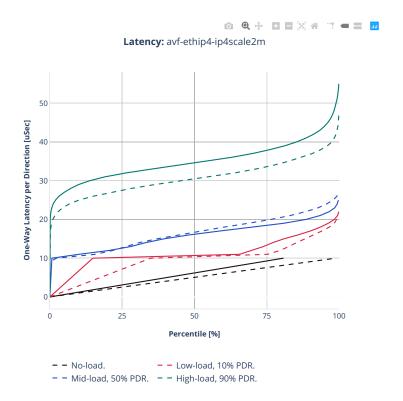

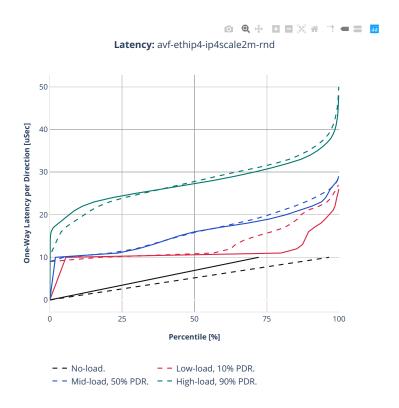

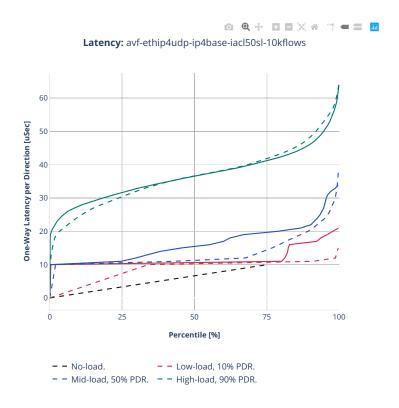

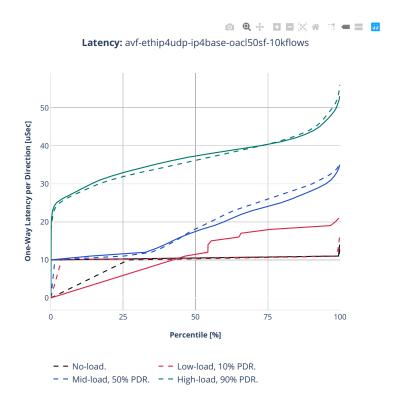

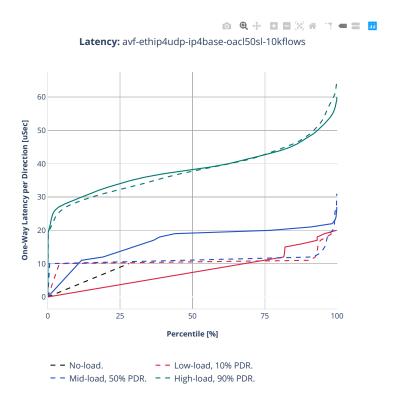

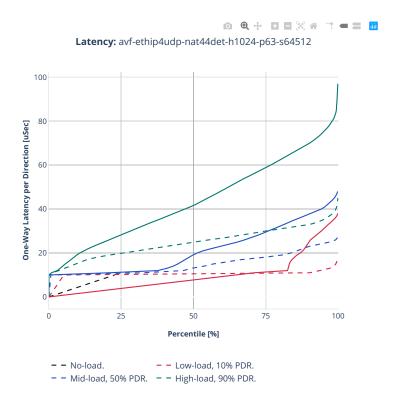

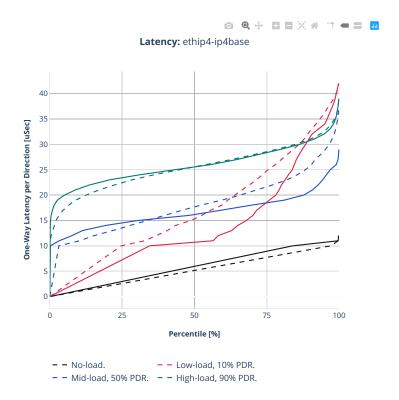

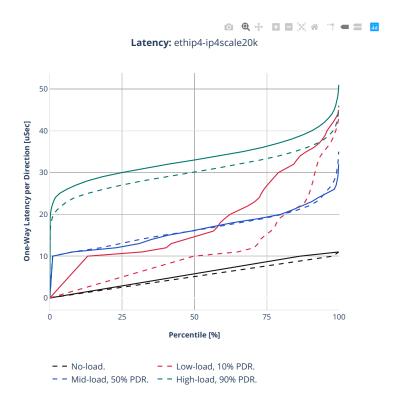

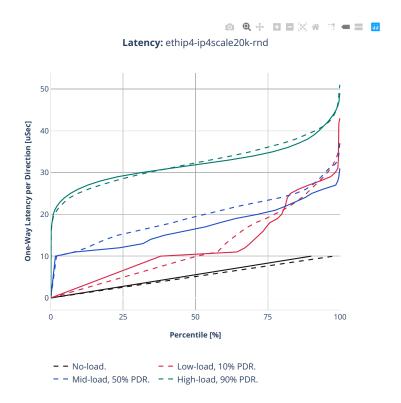

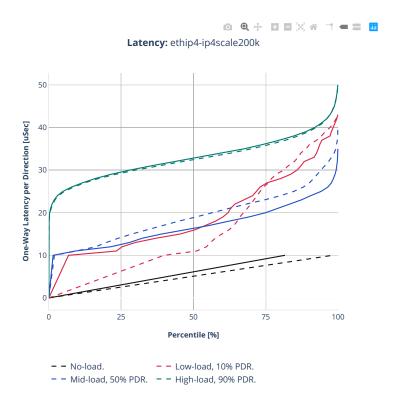

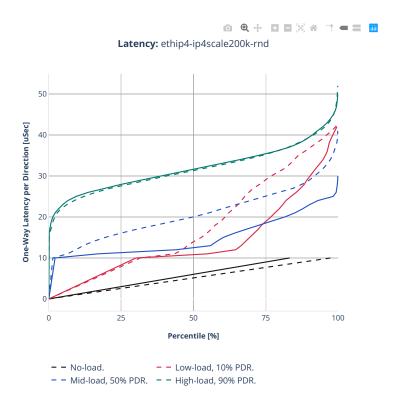

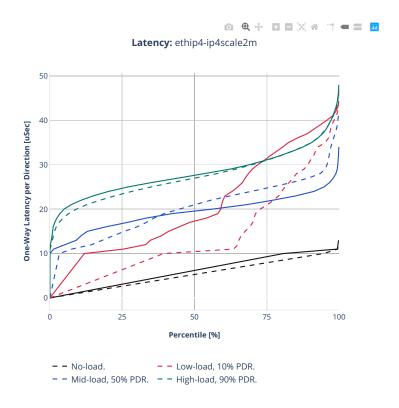

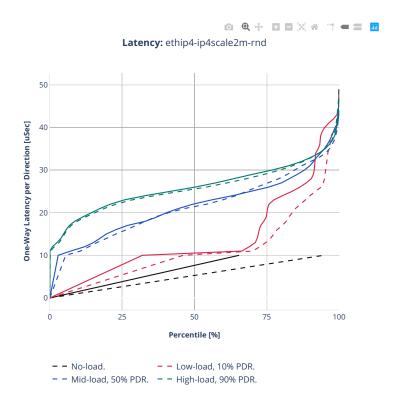

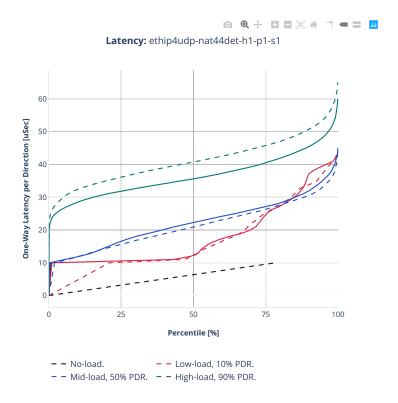

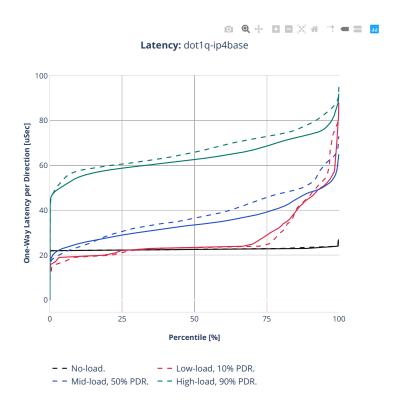

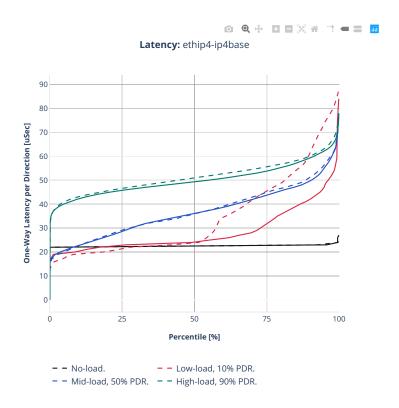

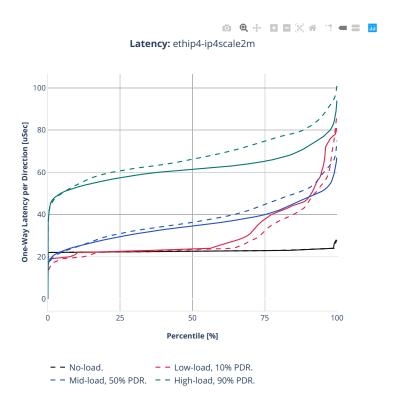

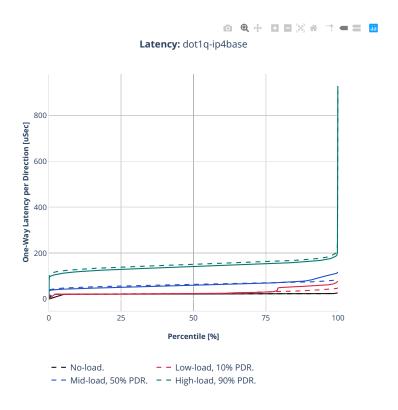

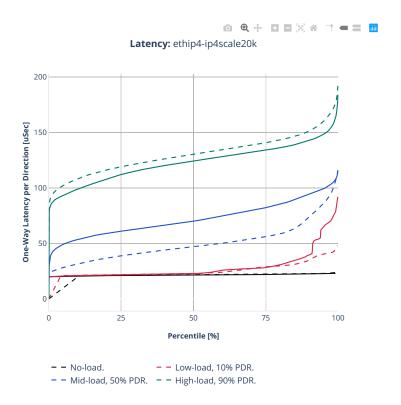

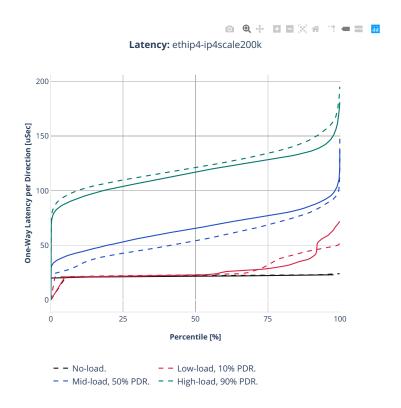

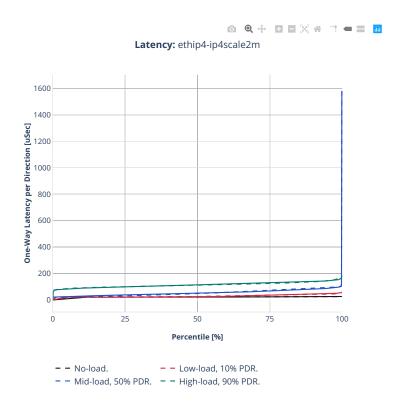

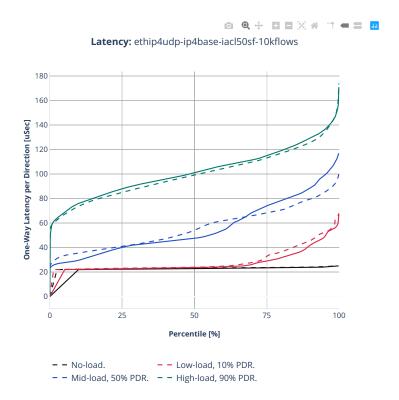

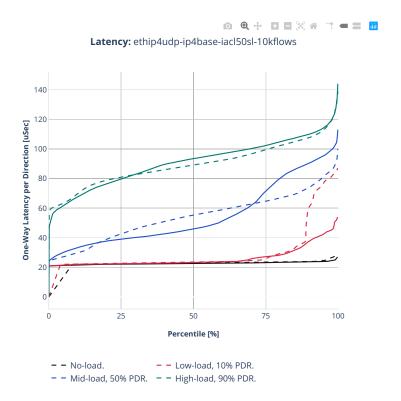

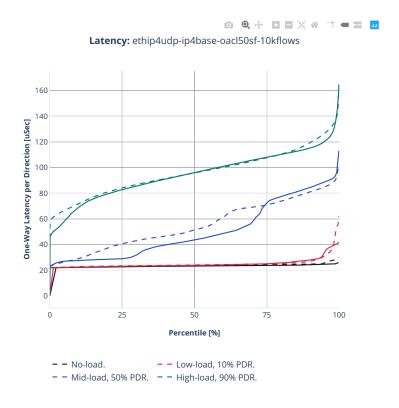

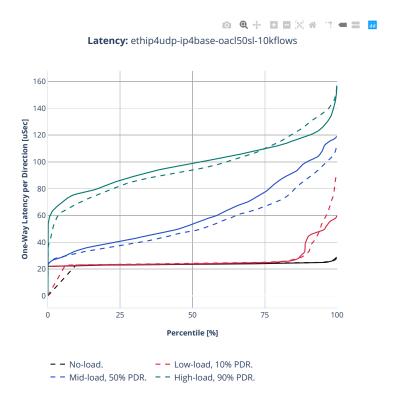

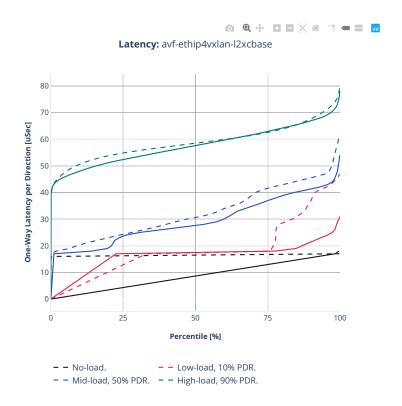

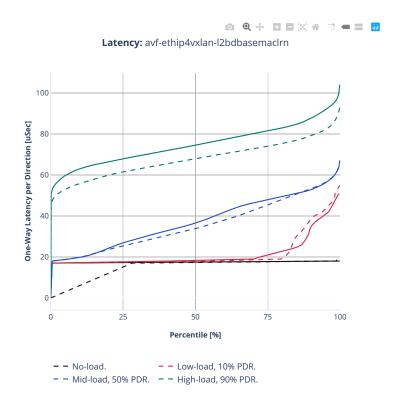

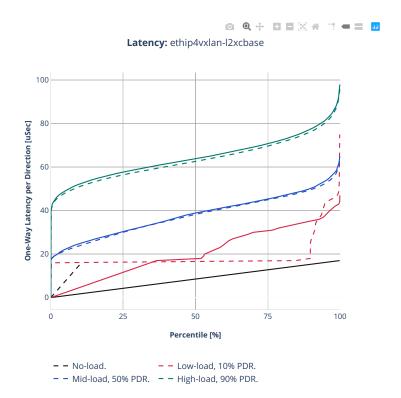

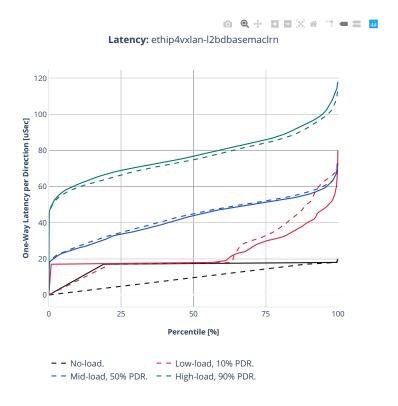

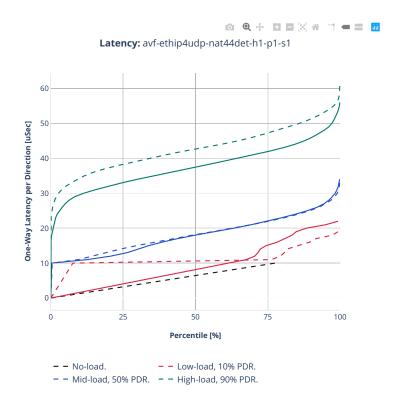

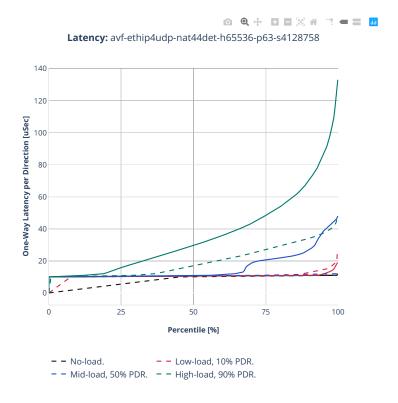

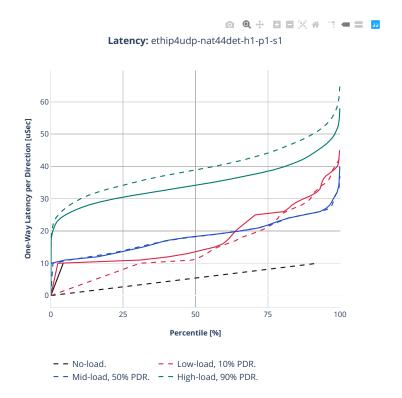

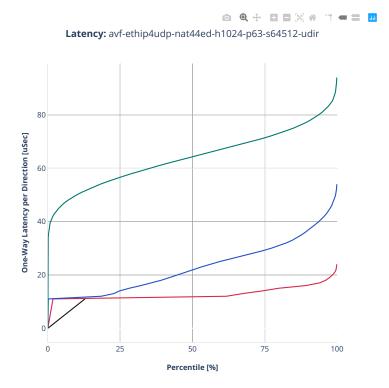

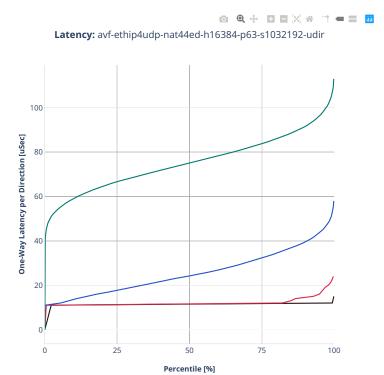

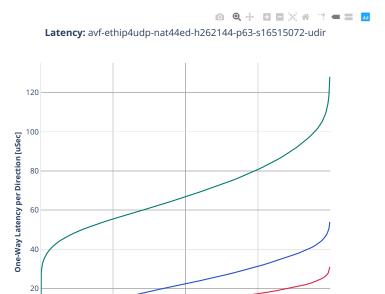

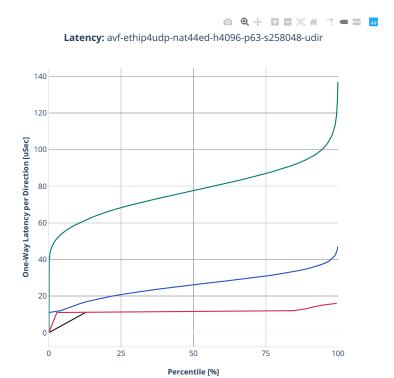

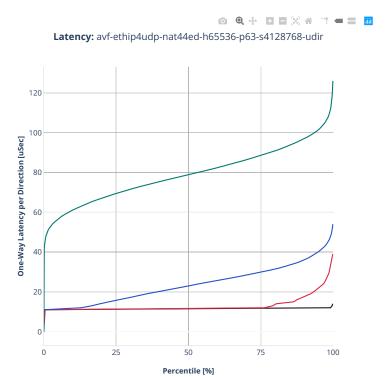

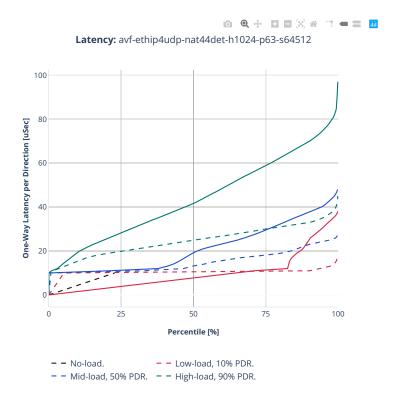

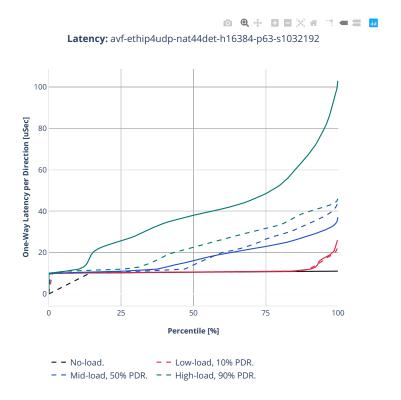

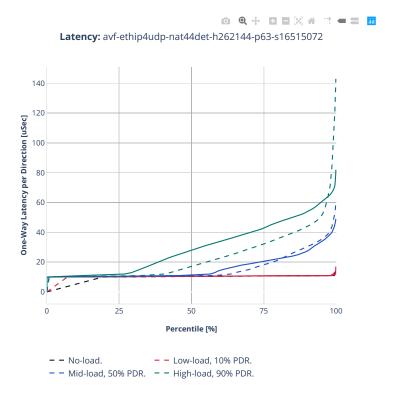

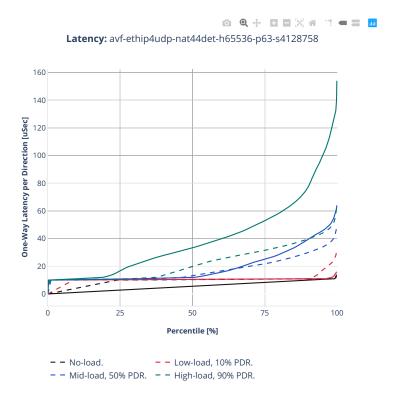

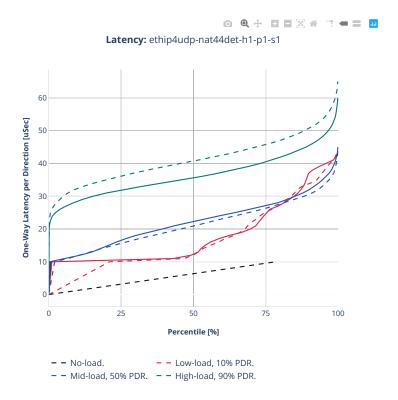

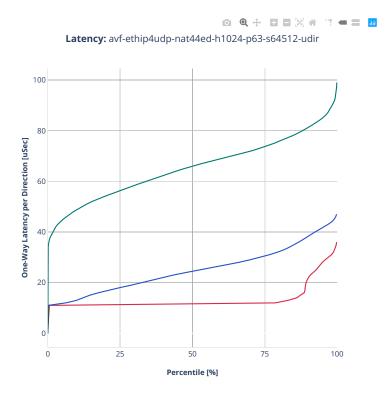

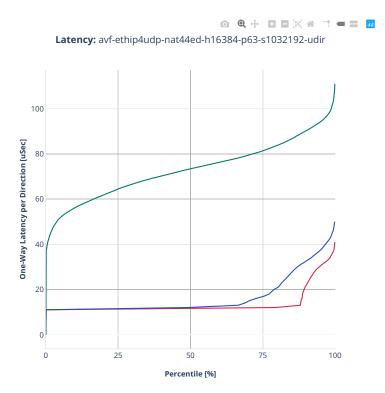

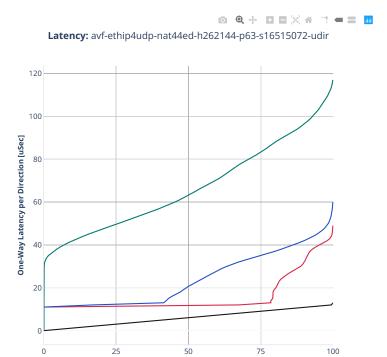

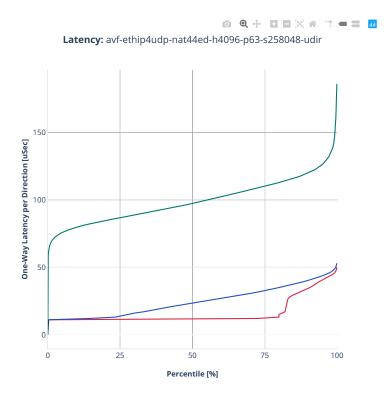

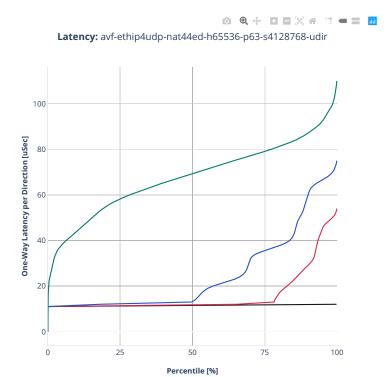

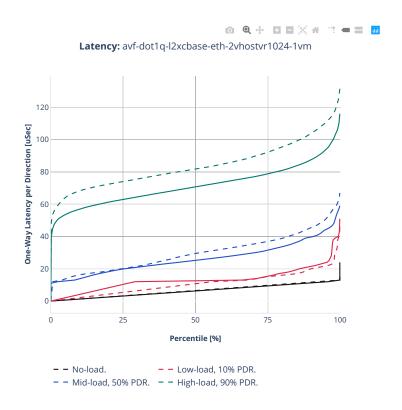

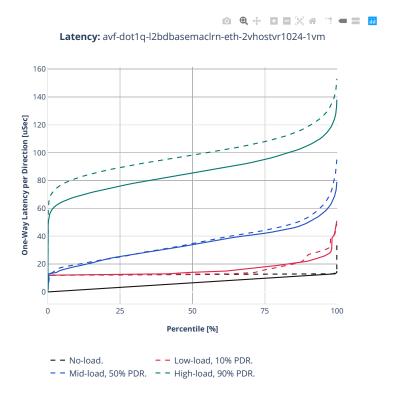

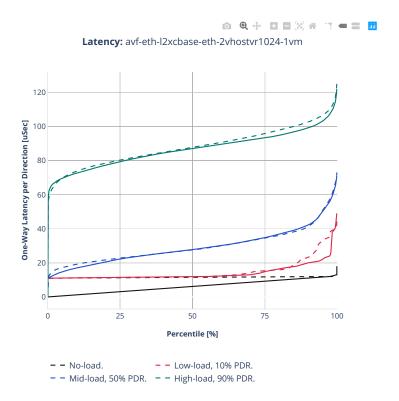

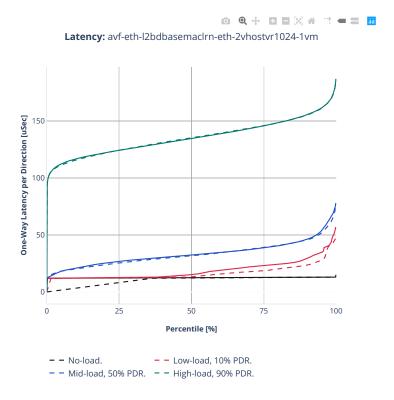

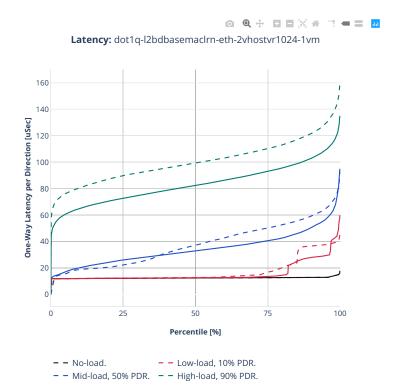

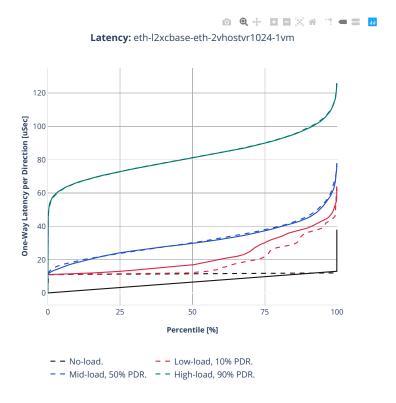

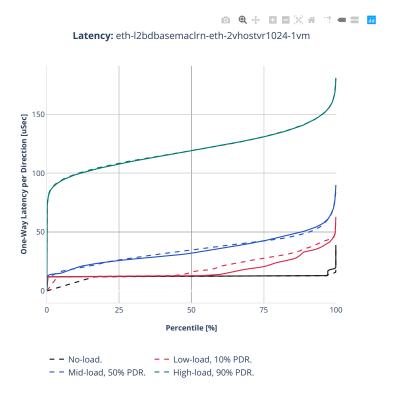

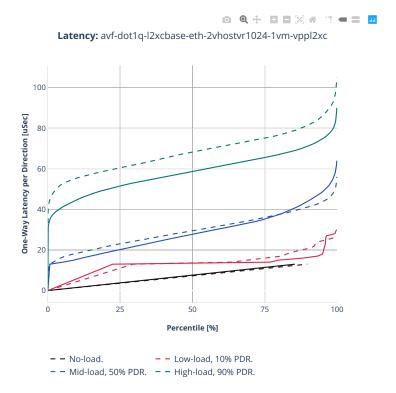

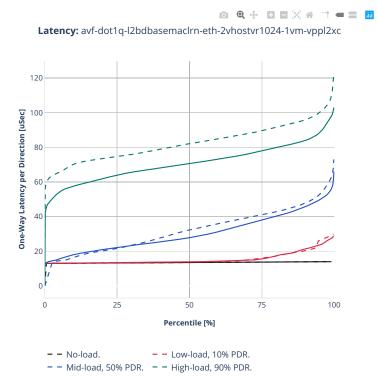

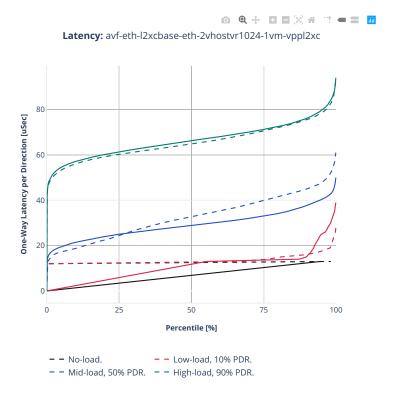

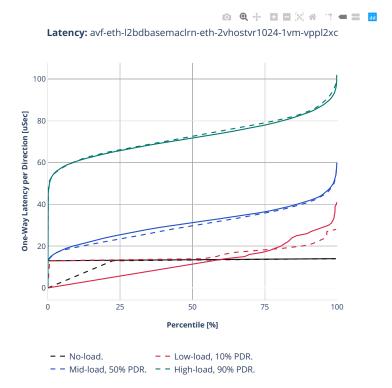

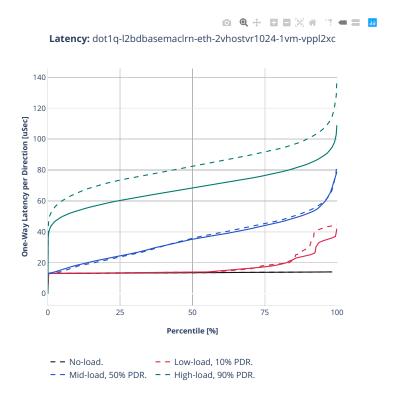

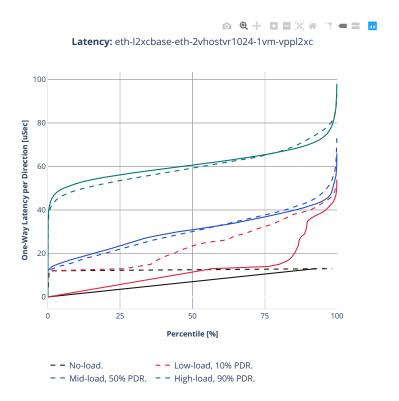

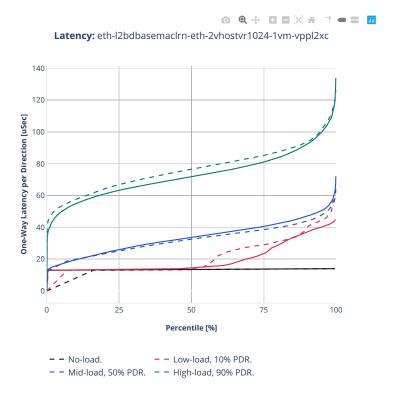

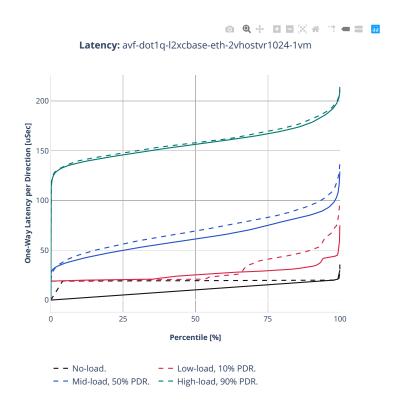

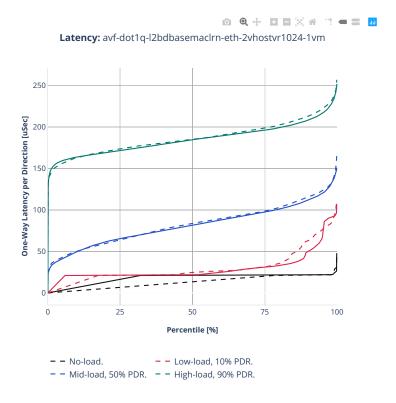

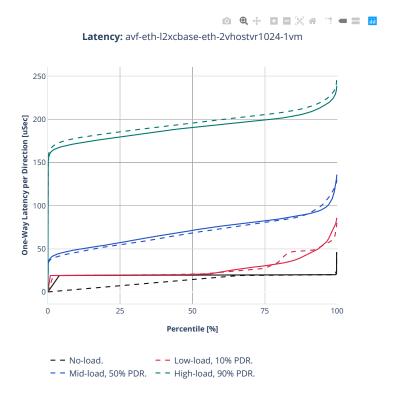

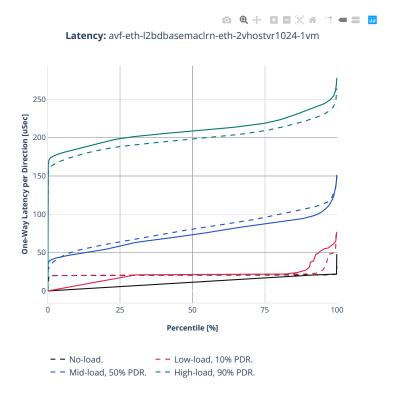

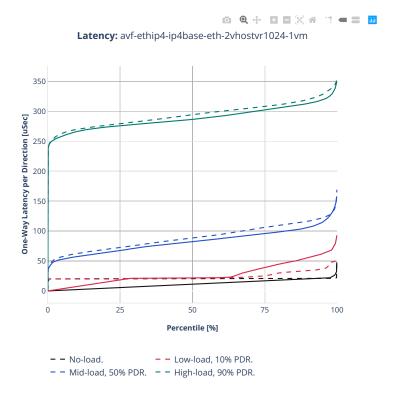

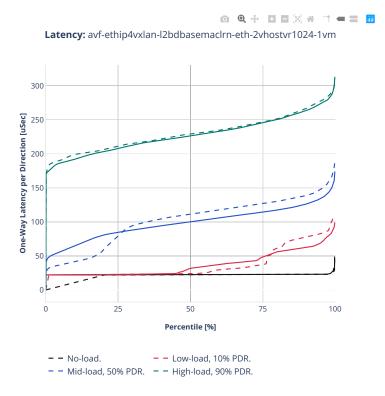

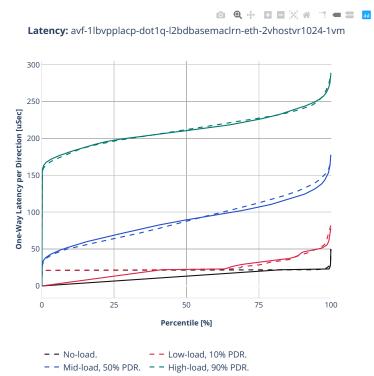

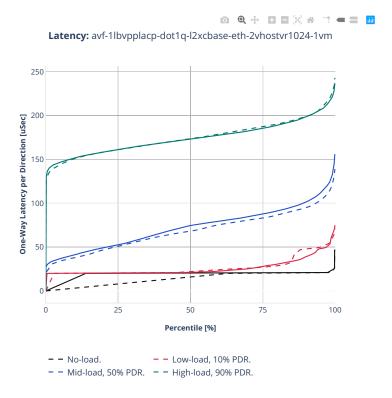

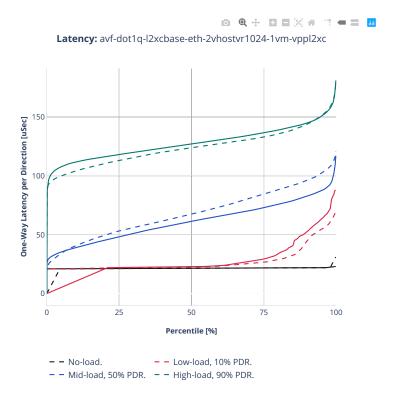

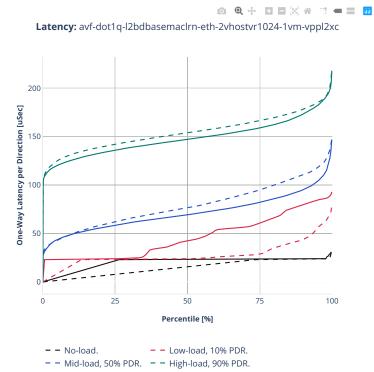

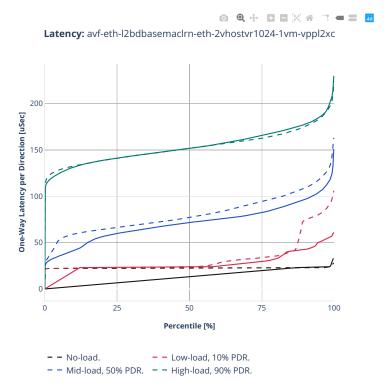

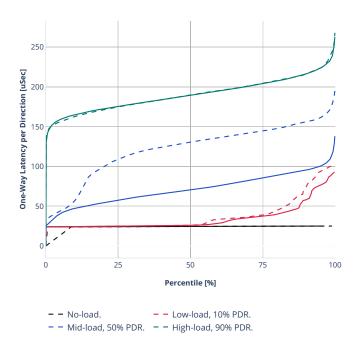

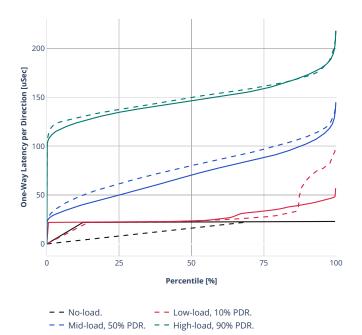

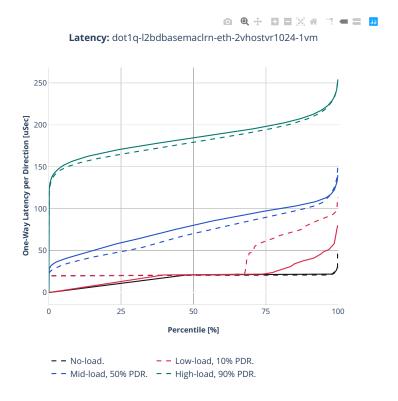

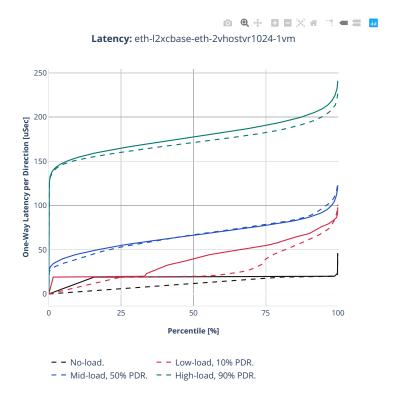

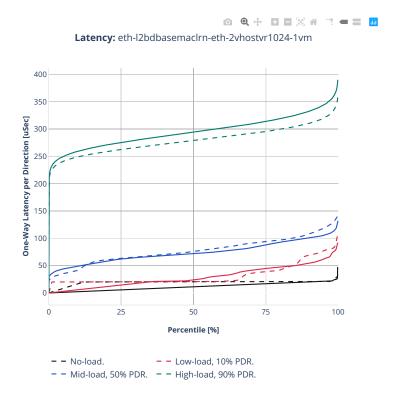

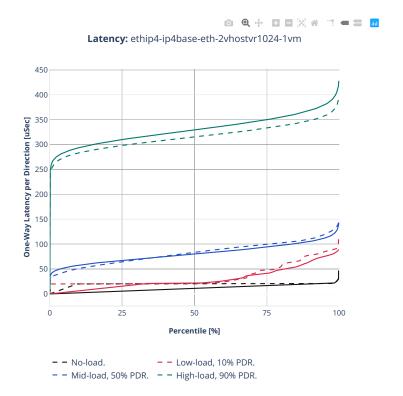

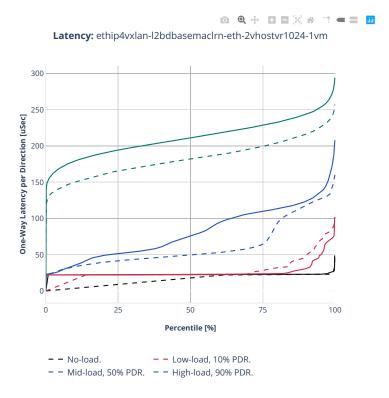

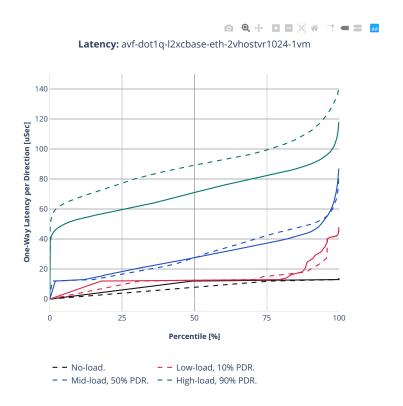

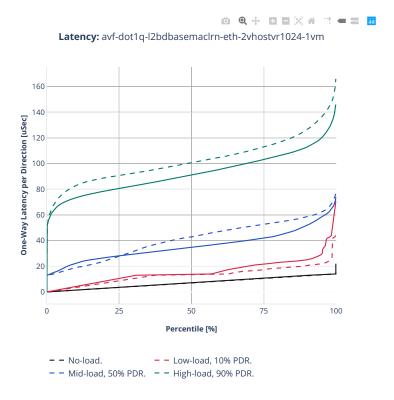

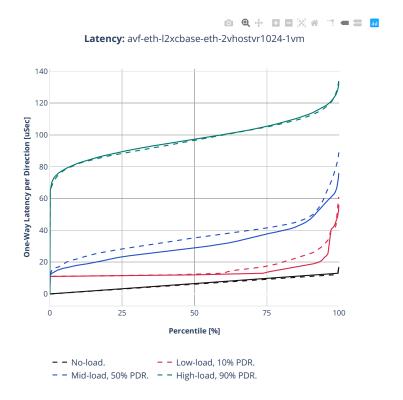

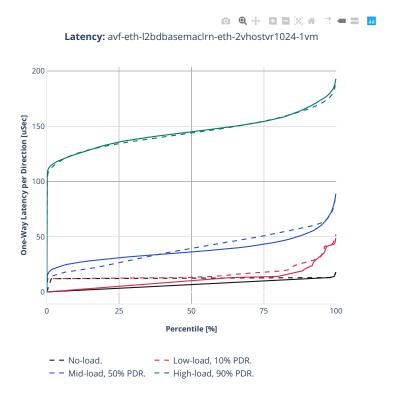

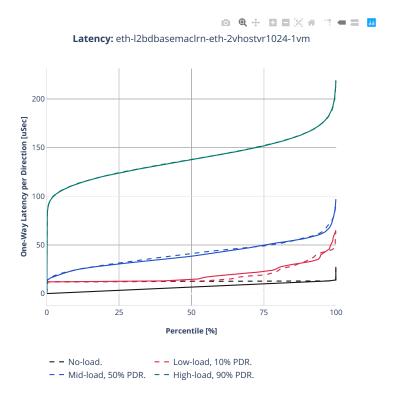

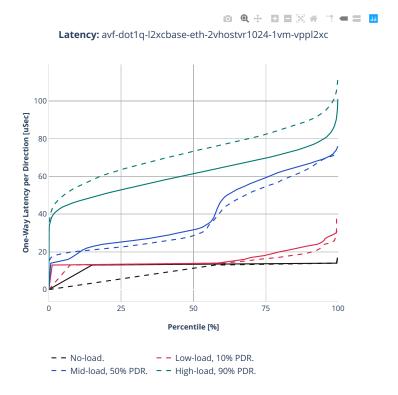

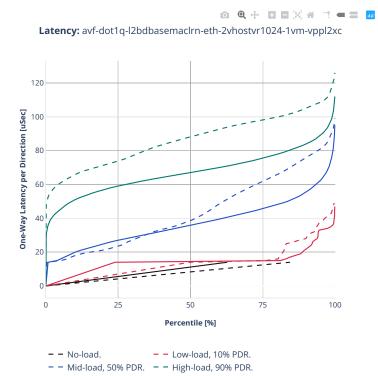

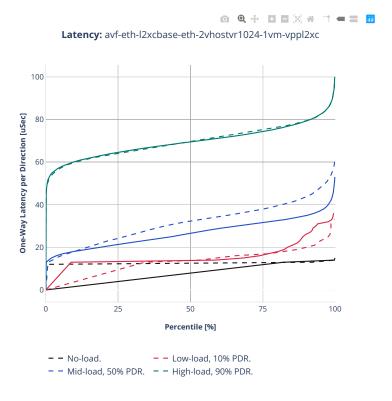

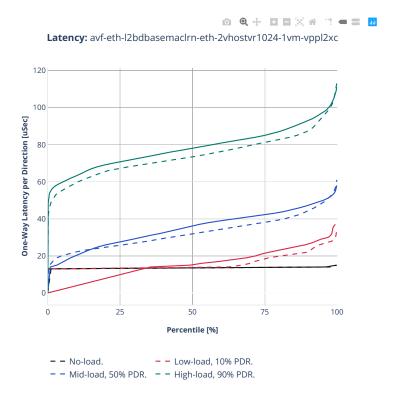

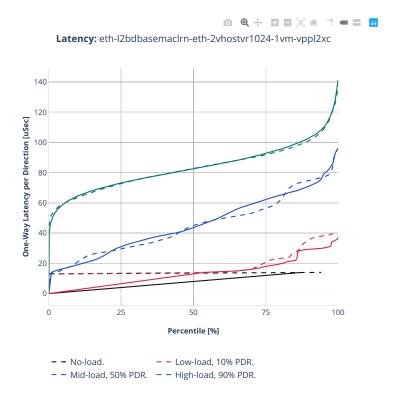

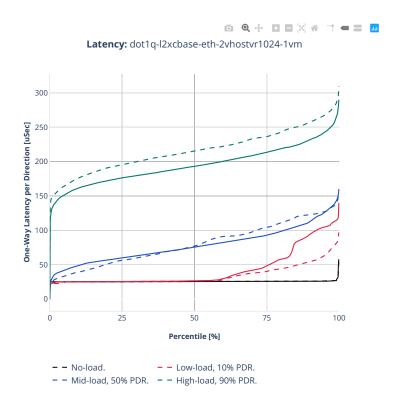

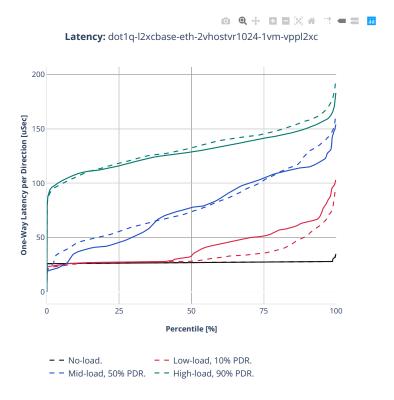

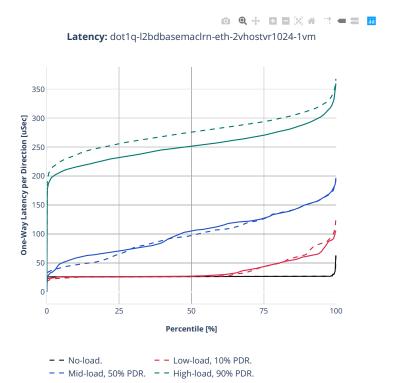

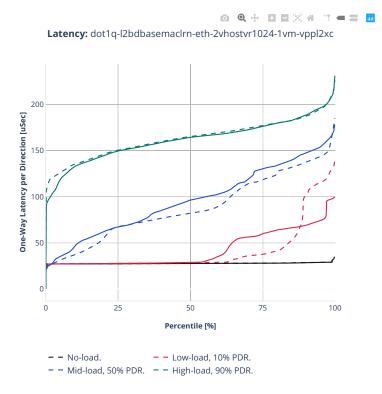

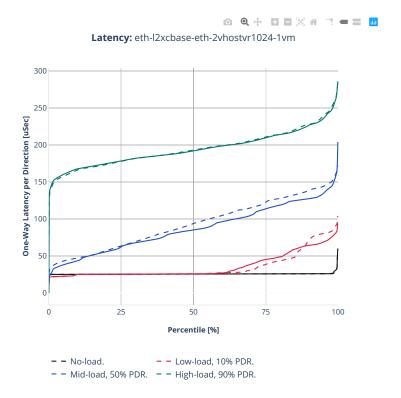

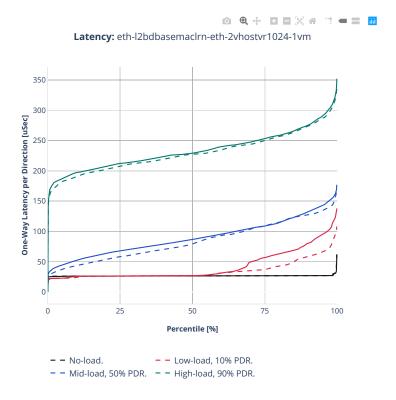

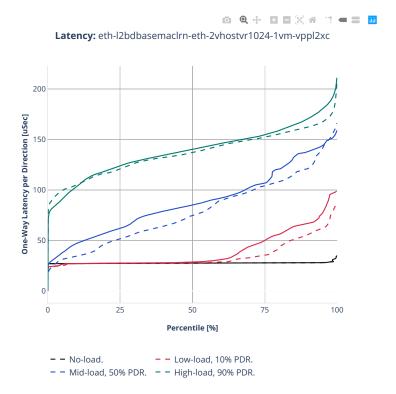

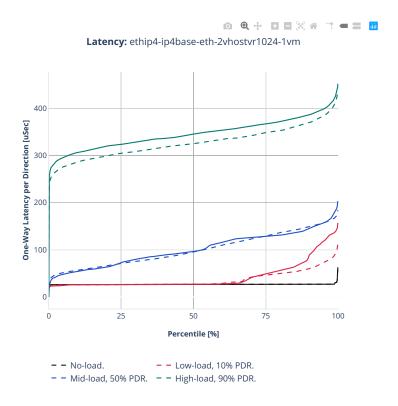

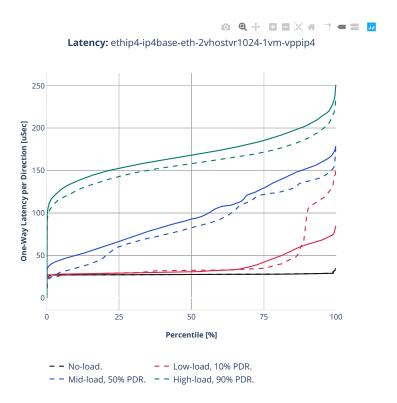

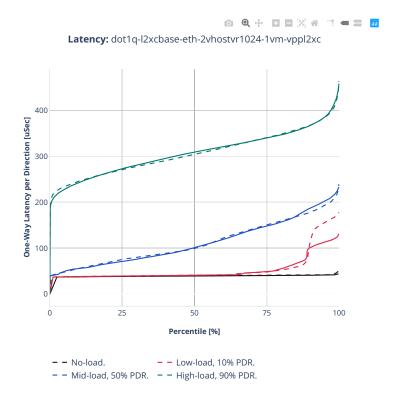

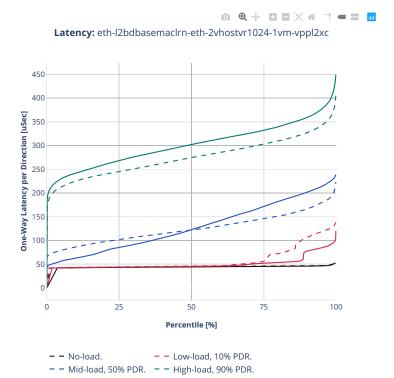

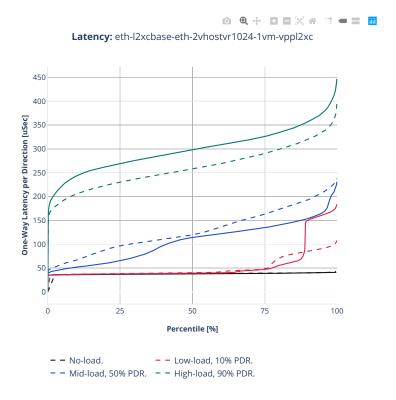

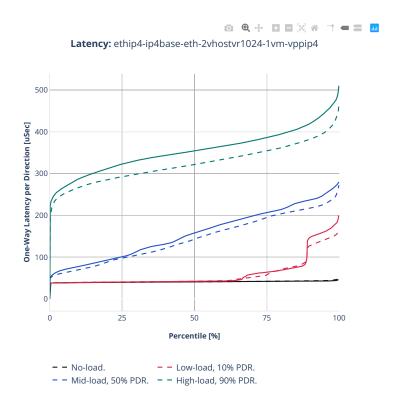

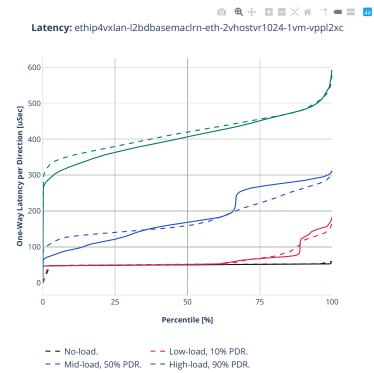

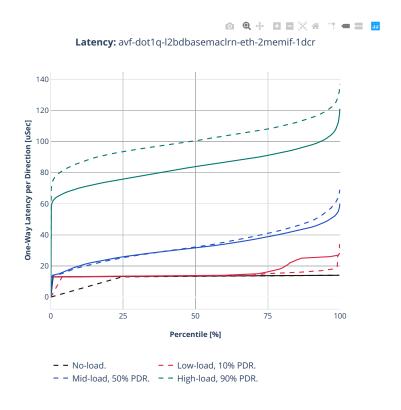

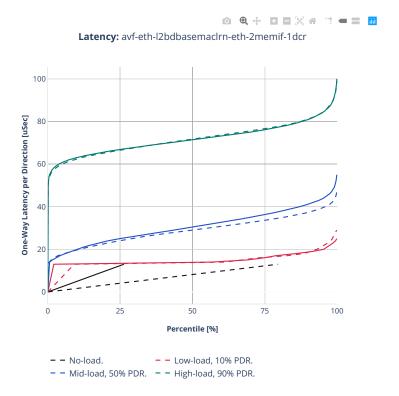

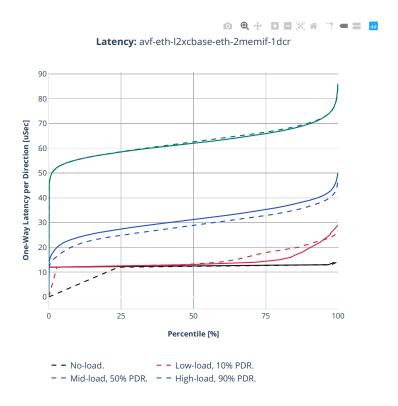

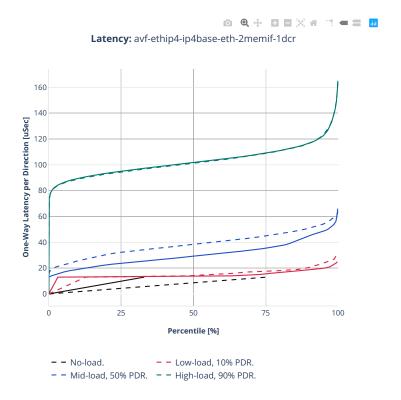

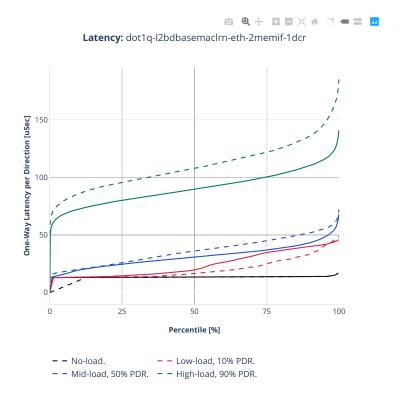

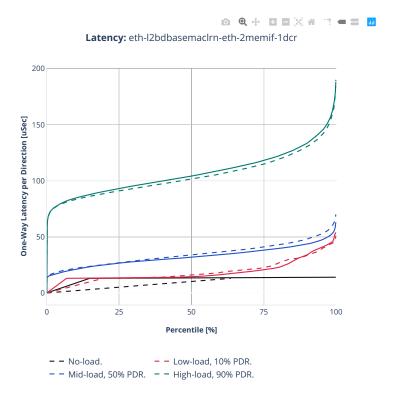

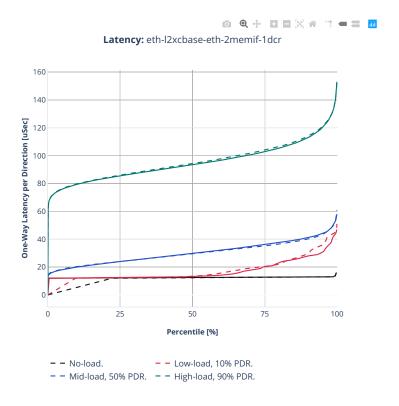

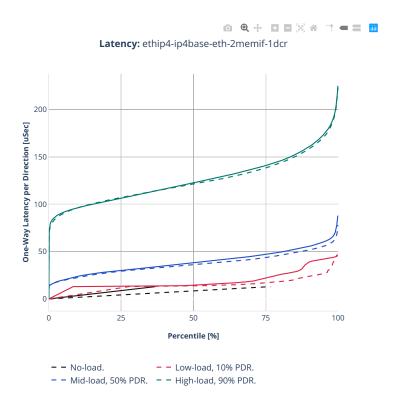

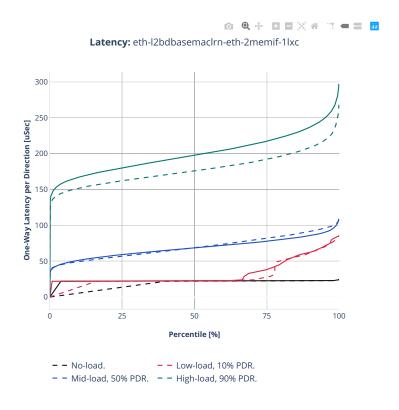

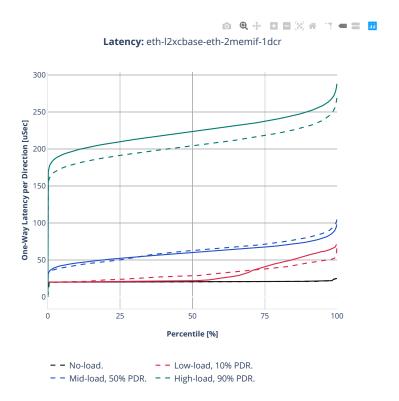

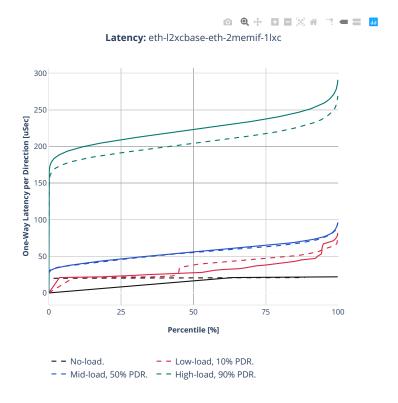

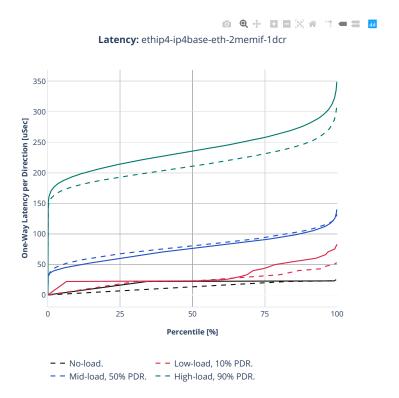

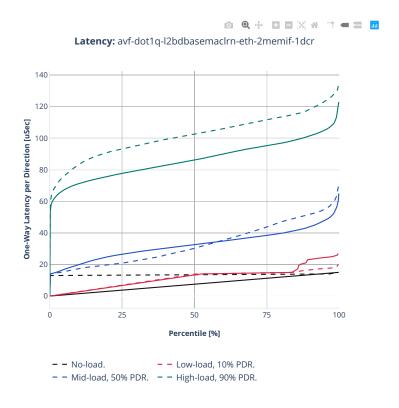

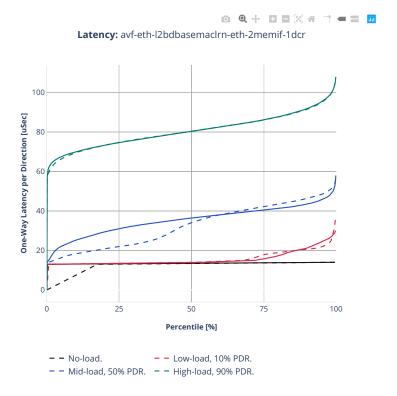

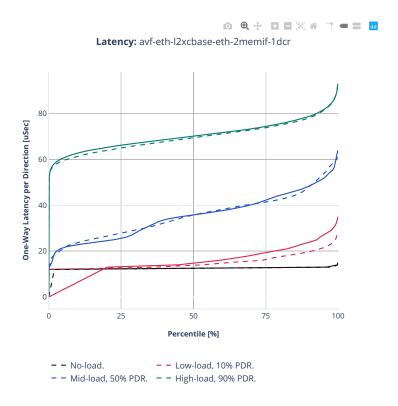

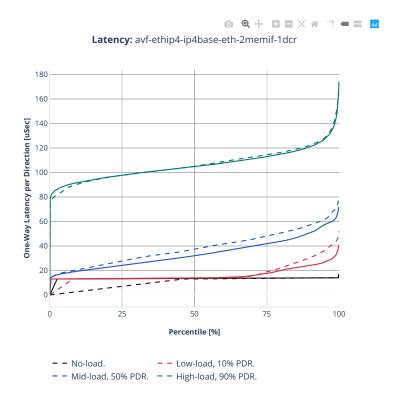

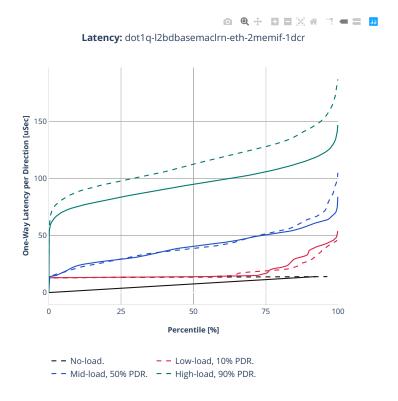

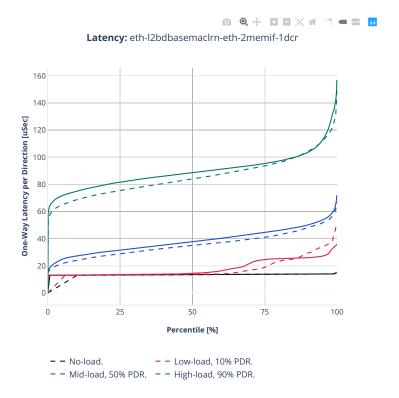

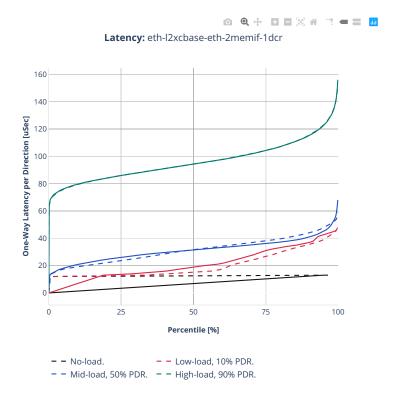

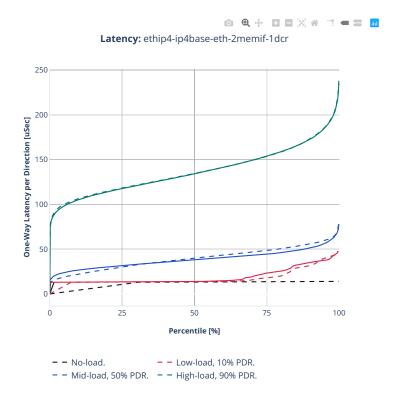

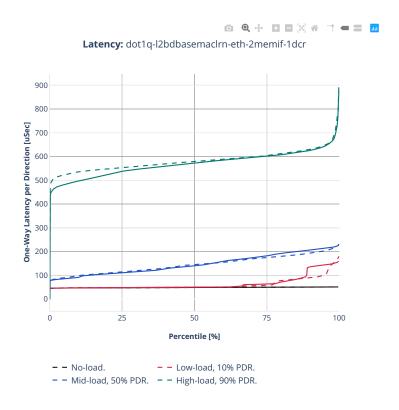

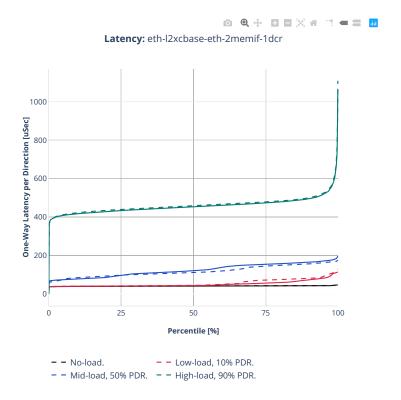

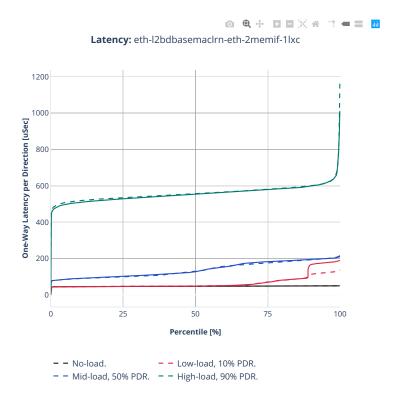

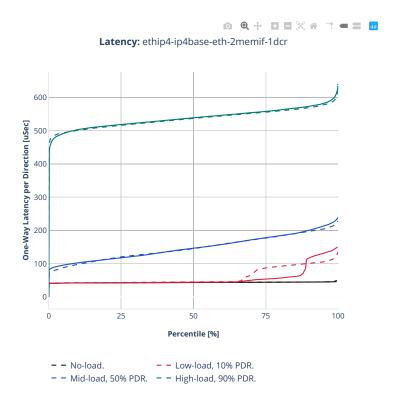

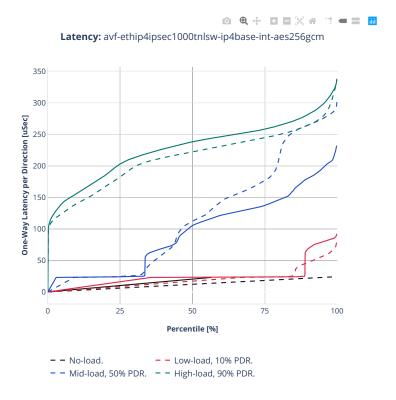

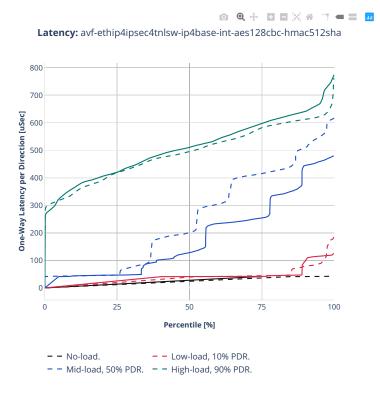

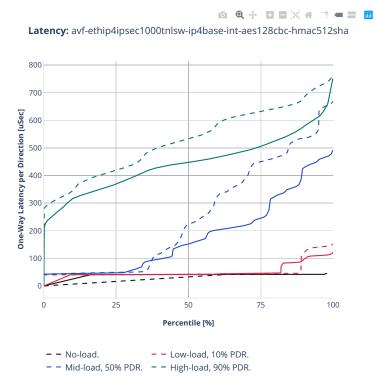

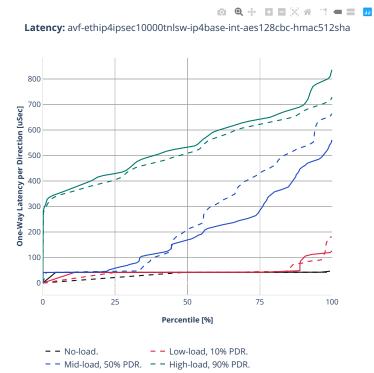

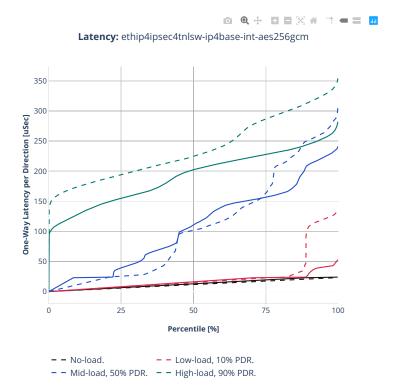

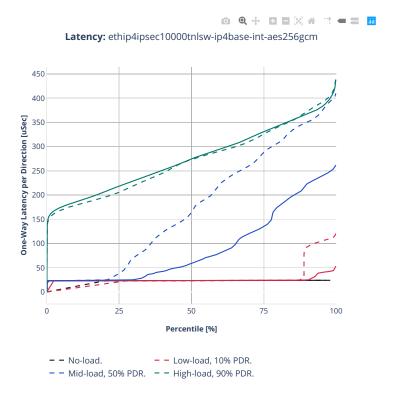

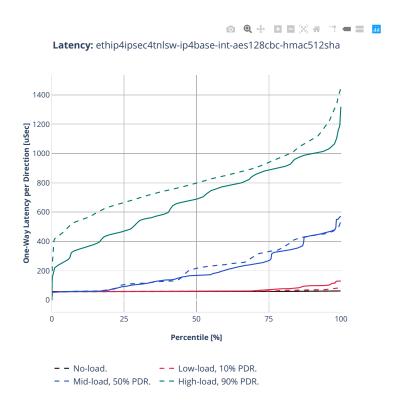

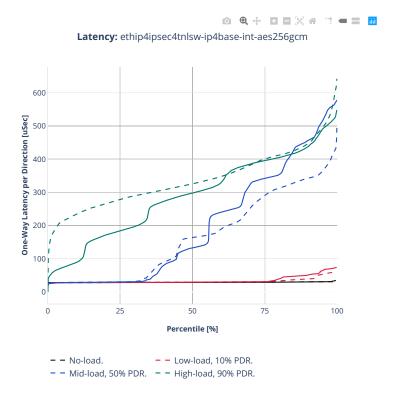

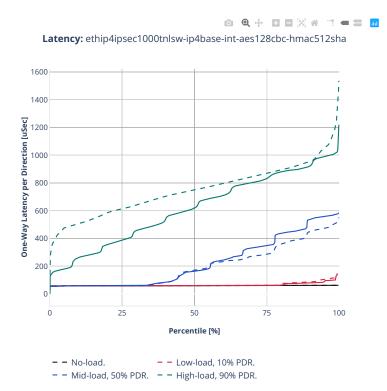

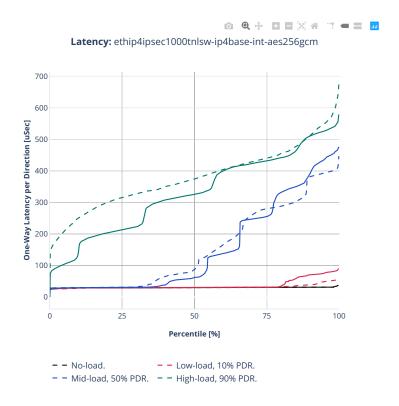

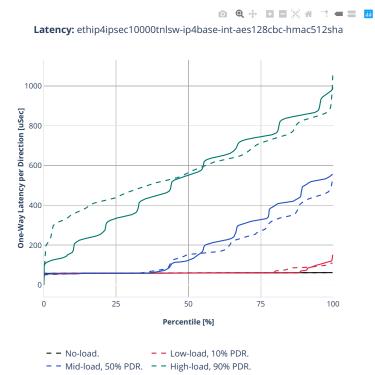

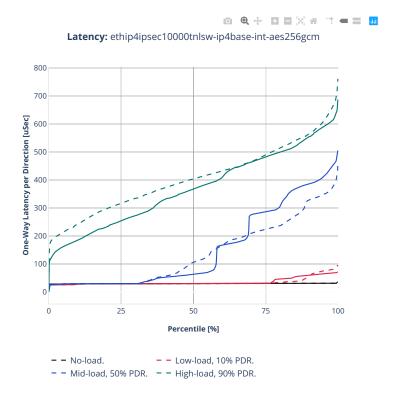

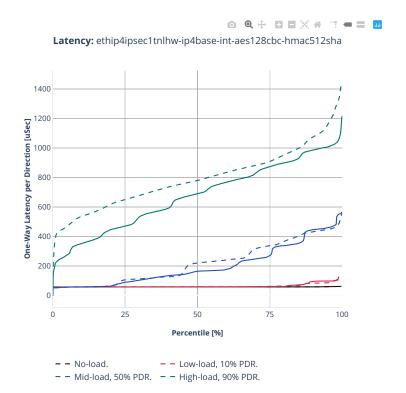

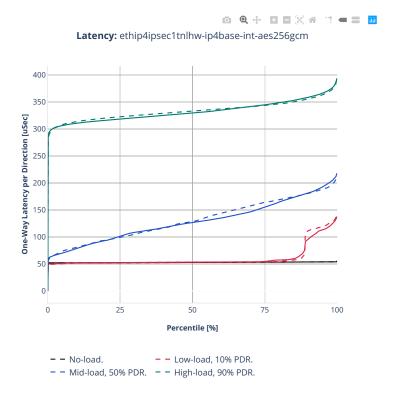

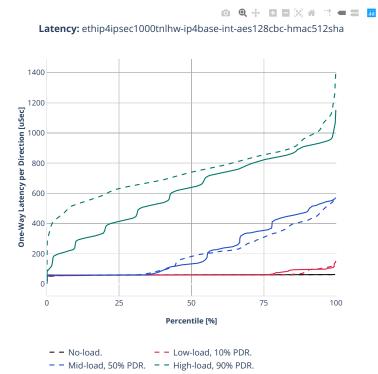

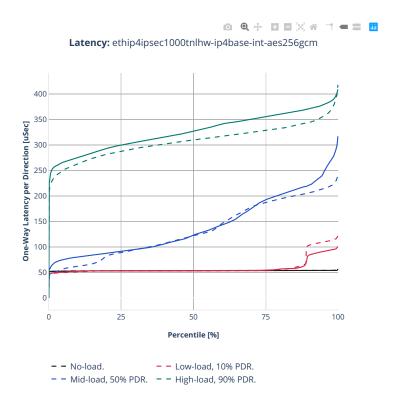

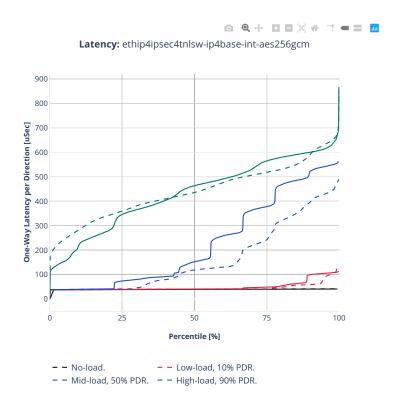

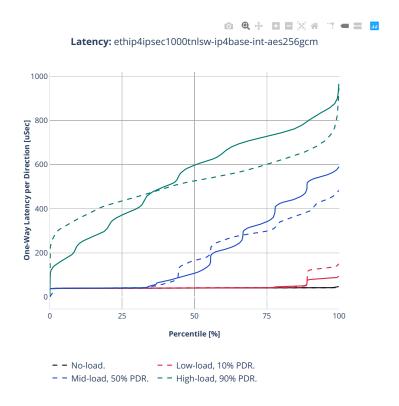

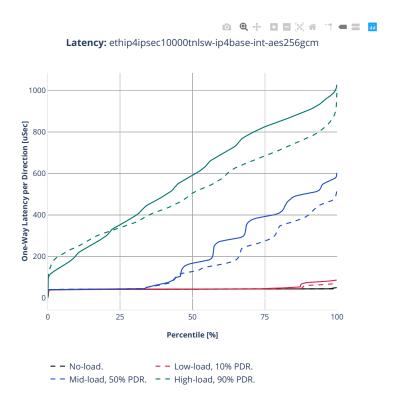

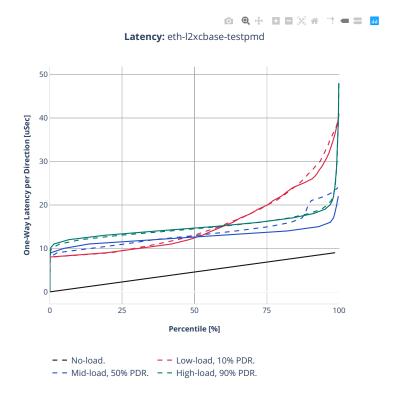

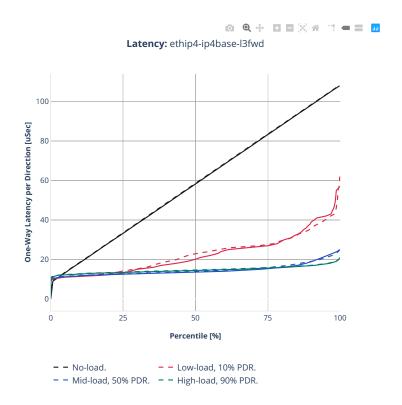

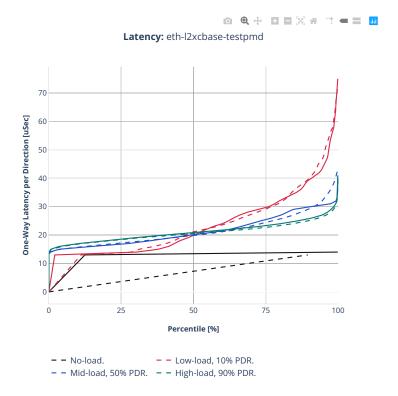

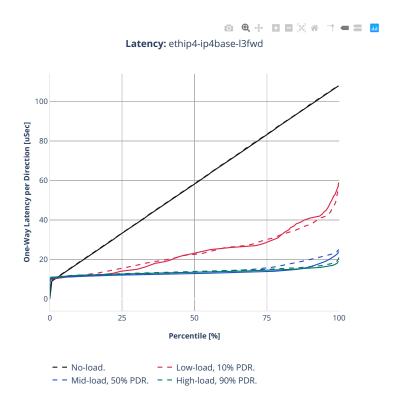

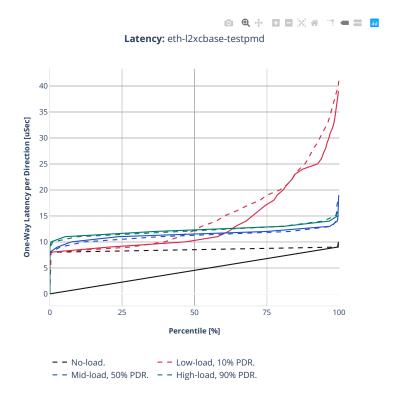

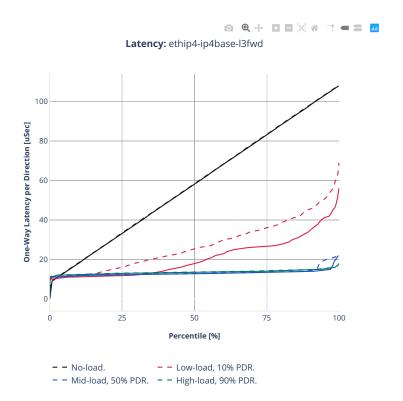

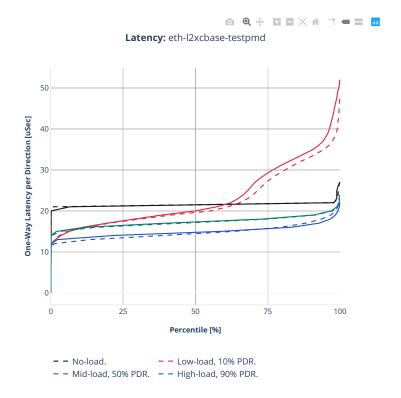

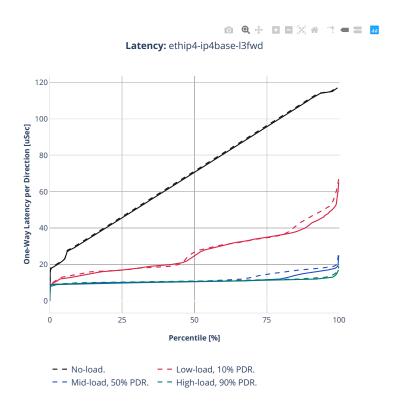

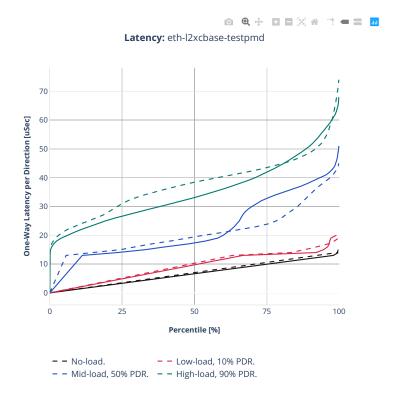

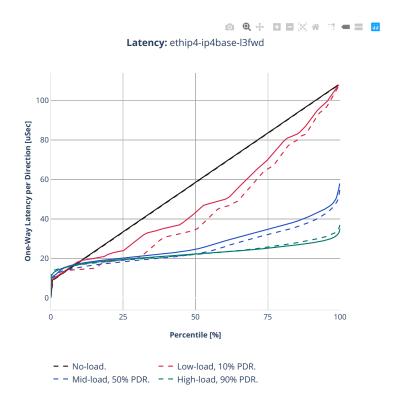

# 1.5.8 Packet Latency

TRex Traffic Generator (TG) is used for measuring latency across 2-Node and 3-Node SUT server topologies. TRex integrates A High Dynamic Range Histogram (HDRH)<sup>22</sup> code providing per packet latency distribution for latency streams sent in parallel to the main load packet streams. Packet latency is measured using following methodology:

- Latency tests are performed at following packet load levels:

- No-Load: latency streams only.

- Low-Load: at 10% PDR.

<sup>&</sup>lt;sup>22</sup> http://hdrhistogram.org/

Mid-Load: at 50% PDR.High-Load: at 90% PDR.NDR-Load: at 100% NDR.PDR-Load: at 100% PDR.

- Latency is measured for all tested packet sizes except IMIX due to TG restriction.

- TG sends dedicated latency streams, one per direction, each at the rate of 9 kpps at the prescribed packet size; these are sent in addition to the main load streams.

- TG reports Min/Avg/Max and HDRH latency values distribution per stream direction, hence two sets of latency values are reported per test case.

- Reported latency values are aggregate across tested topology.

- +/- 1 usec is the measurement accuracy advertised by TRex TG for the setup used.

- TG setup introduces an always-on Tx/Rx interface latency of about 2 \* 2 usec per direction induced by TRex SW writing and reading packet timestamps on CPU cores.

# 1.5.9 Multi-Core Speedup

All performance tests are executed with single physical core and with multiple cores scenarios.

#### Intel Hyper-Threading (HT)

Intel Xeon processors used in FD.io CSIT can operate either in HT Disabled mode (single logical core per each physical core) or in HT Enabled mode (two logical cores per each physical core). HT setting is applied in BIOS and requires server SUT reload for it to take effect, making it impractical for continuous changes of HT mode of operation.

CSIT-2009 performance tests are executed with server SUTs' Intel XEON processors configured with Intel Hyper-Threading Disabled for all Xeon Haswell testbeds (3n-hsw) and with Intel Hyper-Threading Enabled for all Xeon Skylake and Xeon Cascadelake testbeds.

More information about physical testbeds is provided in *Physical Testbeds* (page 4).

#### **Multi-core Tests**

CSIT-2009 multi-core tests are executed in the following VPP worker thread and physical core configurations:

- 1. Intel Xeon Haswell testbeds (3n-hsw) with Intel HT disabled (1 logical CPU core per each physical core):

- 1. 1t1c 1 VPP worker thread on 1 physical core.

- 2. 2t2c 2 VPP worker threads on 2 physical cores.

- 3. 4t4c 4 VPP worker threads on 4 physical cores.

- 1. Intel Xeon Skylake and Cascadelake testbeds (2n-skx, 3n-skx, 2n-clx) with Intel HT enabled (2 logical CPU cores per each physical core):

- 1. 2t1c 2 VPP worker threads on 1 physical core.

- 2. 4t2c 4 VPP worker threads on 2 physical cores.

- 3. 8t4c 8 VPP worker threads on 4 physical cores.

VPP worker threads are the data plane threads running on isolated logical cores. With Intel HT enabled VPP workers are placed as sibling threads on each used physical core. VPP control threads (main, stats) are running on a separate non-isolated core together with other Linux processes.

In all CSIT tests care is taken to ensure that each VPP worker handles the same amount of received packet load and does the same amount of packet processing work. This is achieved by evenly distributing per interface type (e.g. physical, virtual) receive queues over VPP workers using default VPP round-robin mapping and by loading these queues with the same amount of packet flows.

If number of VPP workers is higher than number of physical or virtual interfaces, multiple receive queues are configured on each interface. NIC Receive Side Scaling (RSS) for physical interfaces and multi-queue for virtual interfaces are used for this purpose.

Section *Speedup Multi-Core* (page 287) includes a set of graphs illustrating packet throughout speedup when running VPP worker threads on multiple cores. Note that in quite a few test cases running VPP workers on 2 or 4 physical cores hits the I/O bandwidth or packets-per-second limit of tested NIC.

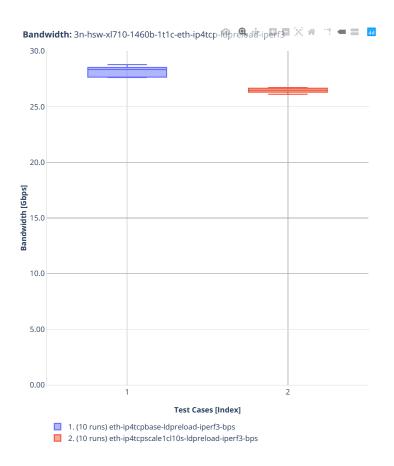

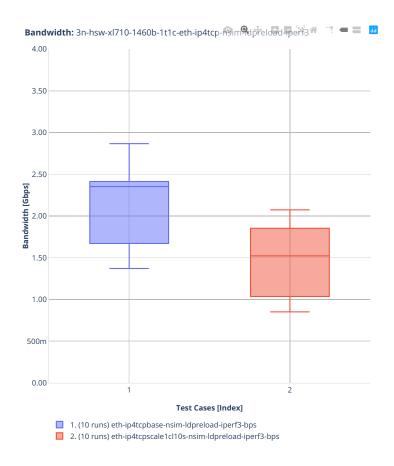

# 1.5.10 Hoststack Testing

#### TCP/IP with iperf3

iperf3 goodput measurement tool<sup>23</sup> is used for measuring the maximum attainable goodput of the VPP Host Stack connection across two instances of VPP running on separate DUT nodes. iperf3 is a popular open source tool for active measurements of the maximum achievable goodput on IP networks.

Because iperf3 utilizes the POSIX socket interface APIs, the current test configuration utilizes the LD\_PRELOAD mechanism in the linux kernel to connect iperf3 to the VPP Host Stack using the VPP Communications Library (VCL) LD\_PRELOAD library (libvcl\_ldpreload.so).

In the future, a forked version of iperf3 which has been modified to directly use the VCL application APIs may be added to determine the difference in performance of 'VCL Native' applications versus utilizing LD\_PRELOAD which inherently has more overhead and other limitations.

The test configuration is as follows:

```

DUT1 Network DUT2

[ iperf3-client -> VPP1 ]======[ VPP2 -> iperf3-server]

```

#### where,

- 1. iperf3 server attaches to VPP2 and LISTENs on VPP2:TCP port 5201.

- 2. iperf3 client attaches to VPP1 and opens one or more stream connections to VPP2:TCP port 5201.

- 3. iperf3 client transmits a uni-directional stream as fast as the VPP Host Stack allows to the iperf3 server for the test duration.

- 4. At the end of the test the iperf3 client emits the goodput measurements for all streams and the sum of all streams.

Test cases include 1 and 10 Streams with a 20 second test duration with the VPP Host Stack configured to utilize the Cubic TCP congestion algorithm.

Note: iperf3 is single threaded, so it is expected that the 10 stream test does not show any performance improvement due to multi-thread/multi-core execution.

There are also variations of these test cases which use the VPP Network Simulator (NSIM) plugin to test the VPP Hoststack goodput with 1 percent of the traffic being dropped at the output interface of VPP1 thereby simulating a lossy network. The NSIM tests are experimental and the test results are not currently representative of typical results in a lossy network.

<sup>&</sup>lt;sup>23</sup> https://github.com/esnet/iperf

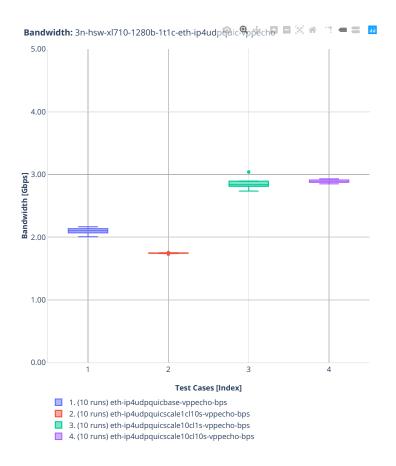

#### QUIC/UDP/IP with vpp\_echo

vpp\_echo performance testing tool<sup>24</sup> is a bespoke performance test application which utilizes the 'native HostStack APIs' to verify performance and correct handling of connection/stream events with unidirectional and bi-directional streams of data.

Because iperf3 does not support the QUIC transport protocol, vpp\_echo is used for measuring the maximum attainable goodput of the VPP Host Stack connection utilizing the QUIC transport protocol across two instances of VPP running on separate DUT nodes. The QUIC transport protocol supports multiple streams per connection and test cases utilize different combinations of QUIC connections and number of streams per connection.

The test configuration is as follows:

#### where,

- 1. vpp\_echo server attaches to VPP2 and LISTENs on VPP2:TCP port 1234.

- 2. vpp\_echo client creates one or more connections to VPP1 and opens one or more stream per connection to VPP2:TCP port 1234.

- 3. vpp\_echo client transmits a uni-directional stream as fast as the VPP Host Stack allows to the vpp\_echo server for the test duration.

- 4. At the end of the test the vpp\_echo client emits the goodput measurements for all streams and the sum of all streams.

#### Test cases include

- 1. 1 QUIC Connection with 1 Stream

- 2. 1 QUIC connection with 10 Streams

- 3. 10 QUIC connetions with 1 Stream

- 4. 10 QUIC connections with 10 Streams

with stream sizes to provide reasonable test durations. The VPP Host Stack QUIC transport is configured to utilize the picotls encryption library. In the future, tests utilizing additional encryption algorithms will be added.

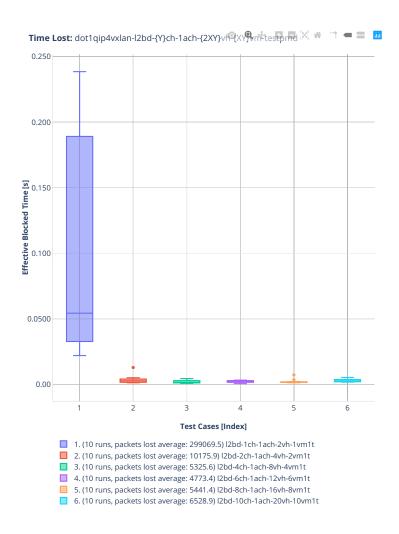

# 1.5.11 Reconfiguration Tests

**Important:** DISCLAIMER: Described reconf test methodology is experimental, and subject to change following consultation within csit-dev, vpp-dev and user communities. Current test results should be treated as indicative.

#### Overview

Reconf tests are designed to measure the impact of VPP re-configuration on data plane traffic. While VPP takes some measures against the traffic being entirely stopped for a prolonged time, the immediate forwarding rate varies during the re-configuration, as some configurations steps need the active dataplane worker threads to be stopped temporarily.

$<sup>^{24}\</sup> https://wiki.fd.io/view/VPP/HostStack\#External\_Echo\_Server.2FClient\_.28vpp\_echo.29$

As the usual methods of measuring throughput need multiple trial measurements with somewhat long durations, and the re-configuration process can also be long, finding an offered load which would result in zero loss during the re-configuration process would be time-consuming.

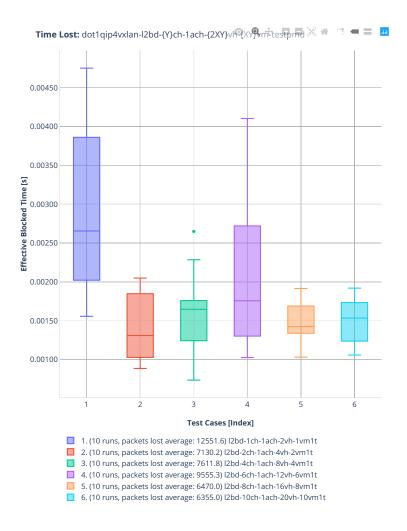

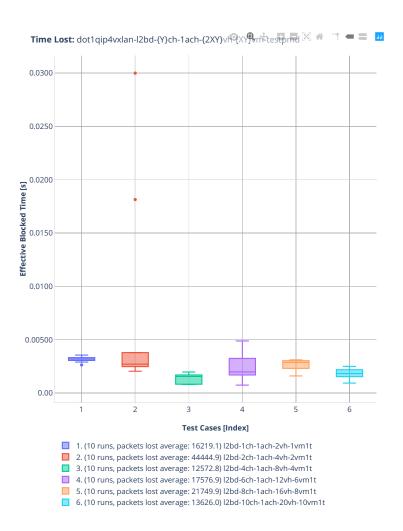

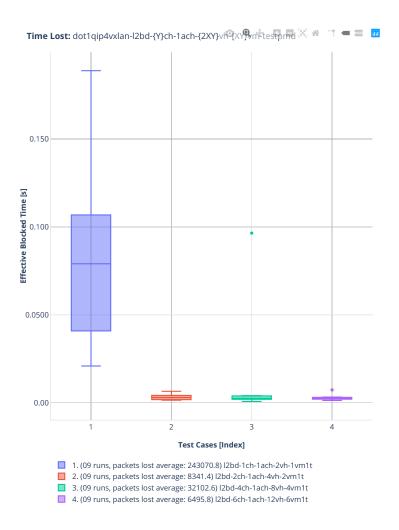

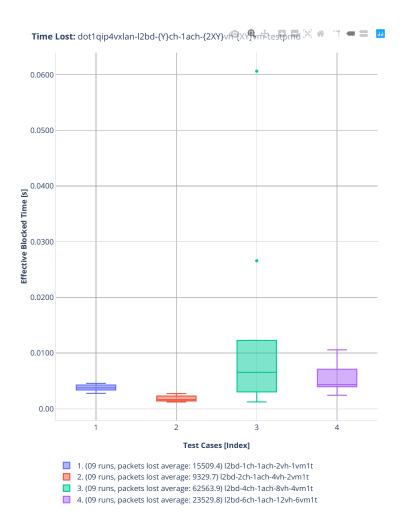

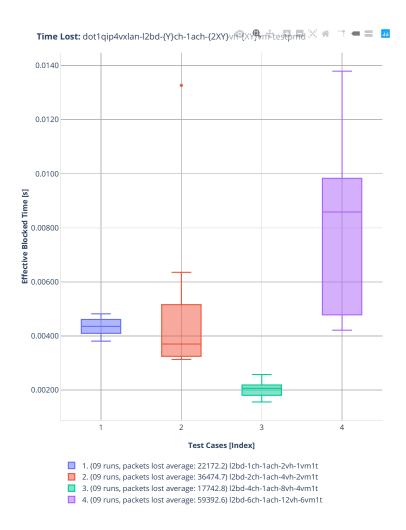

Instead, reconf tests first find a throughput value (lower bound for NDR) without re-configuration, and then maintain that ofered load during re-configuration. The measured loss count is then assumed to be caused by the re-configuration process. The result published by reconf tests is the effective blocked time, that is the loss count divided by the offered load.

#### **Current Implementation**

Each reconf suite is based on a similar MLRsearch performance suite.

MLRsearch parameters are changed to speed up the throughput discovery. For example, PDR is not searched for, and the final trial duration is shorter.

The MLRsearch suite has to contain a configuration parameter that can be scaled up, e.g. number of tunnels or number of service chains. Currently, only increasing the scale is supported as the re-configuration operation. In future, scale decrease or other operations can be implemented.

The traffic profile is not changed, so the traffic present is processed only by the smaller scale configuration. The added tunnels / chains are not targetted by the traffic.

For the re-configuration, the same Robot Framework and Python libraries are used, as were used in the initial configuration, with the exception of the final calls that do not interact with VPP (e.g. starting virtual machines) being skipped to reduce the test overall duration.

#### Discussion

Robot Framework introduces a certain overhead, which may affect timing of individual VPP API calls, which in turn may affect the number of packets lost.

The exact calls executed may contain unnecessary info dumps, repeated commands, or commands which change a value that do not need to be changed (e.g. MTU). Thus, implementation details are affecting the results, even if their effect on the corresponding MLRsearch suite is negligible.

The lower bound for NDR is the only value safe to be used when zero packets lost are expected without reconfiguration. But different suites show different "jitter" in that value. For some suites, the lower bound is not tight, allowing full NIC buffers to drain quickly between worker pauses. For other suites, lower bound for NDR still has quite a large probability of non-zero packet loss even without re-configuration.

#### 1.5.12 VPP Startup Settings